LMK00334四输出时钟缓冲器与电平转换器技术文档总结

描述

LMK00334器件是一款4输出HCSL扇出缓冲器,用于高频、低抖动时钟、数据分配和电平转换。该器件能够为 ADC、DAC、多千兆以太网、XAUI、光纤通道、SATA/SAS、SONET/SDH、CPRI 和高频背板分配参考时钟。

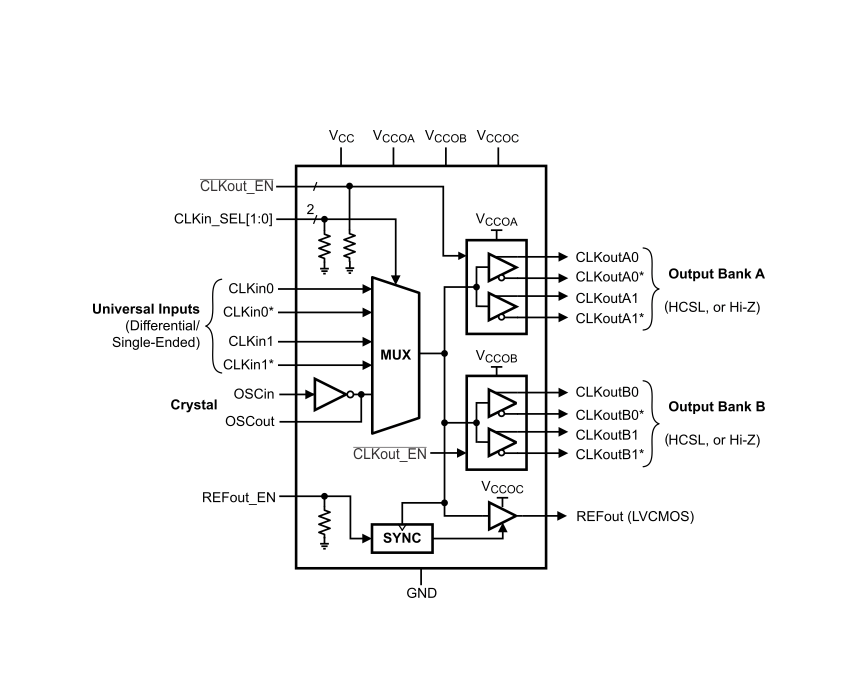

输入时钟可以从两个通用输入或一个晶体输入中选择。选定的输入时钟分配到两个HCSL输出和一个LVCMOS输出的两组。LVCMOS 输出具有同步使能输入,可在使能或禁用时实现无欠幅脉冲作。该LMK00334采用3.3V内核电源和三个独立的3.3V或2.5V输出电源供电。

*附件:lmk00334.pdf

该LMK00334具有高性能、多功能性和能效,使该器件设计用于替代固定输出缓冲器器件,同时增加系统中的时序裕量。

特性

- 3:1 输入多路复用器

- 两个通用输入工作频率高达 400MHz,并接受 LVPECL、LVDS、CML、SSTL、HSTL、HCSL 或单端时钟

- 一个晶体输入接受10MHz至40MHz晶体或单端时钟

- 两个组,每个组有两个差分输出

- HCSL 或 Hi-Z(可选)

- PCIe 规范的加法 RMS 相位抖动

- 第 5 代的 7.2fs RMS(典型值)

- 第 6 代的 5fs RMS(典型值)

- 第 7 代 3.5fs RMS(典型值)

- 高PSRR:156.25MHz时为–72dBc

- LVCMOS 输出,带同步使能输入

- 引脚控制配置

- VCC内核电源:3.3V ± 5%

- 三个独立的VCCO输出电源:3.3V、2.5V±5%

- 工业温度范围:–40°C 至 +105°C

- 32 引脚 WQFN(5mm × 5mm)

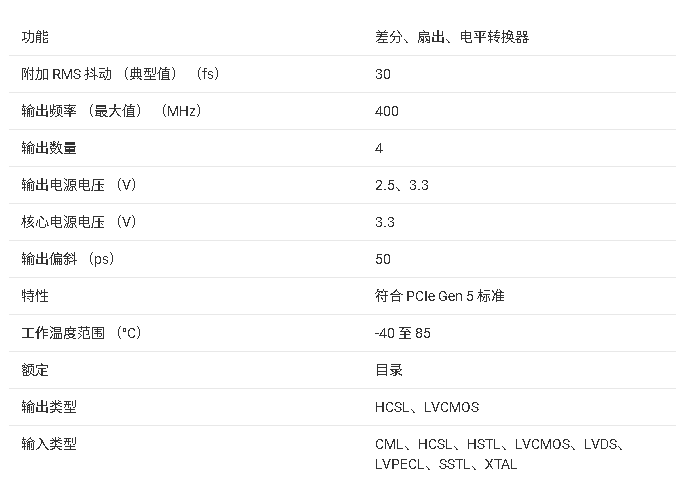

参数

方框图

1. 产品概述

LMK00334是德州仪器(TI)推出的高性能4输出HCSL时钟扇出缓冲器,专为PCIe® Gen 1至Gen 7设计,支持低附加抖动时钟分配和电平转换。其核心特性包括:

- 输入多路复用器:3:1输入选择(2个通用差分输入+1个晶体输入),支持LVPECL、LVDS、CML等多种信号类型,频率最高达400MHz。

- 输出配置:两路独立输出组(每组2个HCSL差分输出+1个LVCMOS输出),支持Hi-Z模式选择。

- 关键性能:

- 超低附加RMS相位抖动:Gen 5典型值7.2fs,Gen 6为5fs,Gen 7仅3.5fs。

- 高电源抑制比(PSRR):-72dBc @ 156.25MHz。

- 宽工作温度范围:-40°C至+105°C。

2. 应用场景

- 数据中心交换机、核心路由器

- 服务器/计算平台(PCIe Gen 3.0至5.0)

- 无线基站(远程射频单元与基带单元)

3. 技术细节

- 电源管理:

- 核心供电(VCC):3.3V ±5%

- 独立输出供电(VCCOA/B/C):3.3V或2.5V ±5%

- 封装与引脚:32引脚WQFN(5mm×5mm),集成散热焊盘(DAP)优化热性能。

- 控制功能:

- 引脚配置选择输入时钟与输出模式(如CLKin_SEL[1:0]控制输入源)。

- LVCMOS输出支持同步使能,避免使能/禁用时的脉冲干扰。

4. 设计支持

- 布局建议:优先采用差分信号输入以降低噪声,推荐高摆率(≥3V/ns)提升性能。

- 热管理:需通过PCB散热焊盘与多层板设计控制结温(最大125°C)。

- 文档资源:包含绝对最大额定值、ESD等级、典型应用电路及机械封装信息。

附件说明

本文档为完整数据手册摘要,涵盖特性、电气参数、应用指南及封装细节,适用于高速时钟分配系统的硬件设计参考。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

深入解析LMK00105:超低抖动LVCMOS扇出缓冲器与电平转换器2026-02-09 300

-

LMK00804B-Q1:高性能时钟扇出缓冲器与电平转换器2026-02-08 298

-

LMK00338 8-Output PCIe时钟缓冲器与电平转换器技术文档总结2025-09-15 751

-

LMK00334-Q1 四输出时钟缓冲器和电平转换器技术文档总结2025-09-12 919

-

LMK00334输出无波形,一直保持3.3V上拉是怎么回事?2024-11-08 332

-

LMK00308 3GHz 8路输出差动时钟缓冲器/电平转换器数据表2024-08-22 435

-

LMK00334-Q1四路输出PCIe第1代至第5代时钟缓冲器和电平转换器数据表2024-08-21 589

-

LMK00334四路输出PCIe第1代至第5代时钟缓冲器和电平转换器数据表2024-08-20 548

-

LMK00334 LMK00334 4 输出 PCIe Gen1/Gen2/Gen3 时钟缓冲器/电平转换器2019-04-18 420

全部0条评论

快来发表一下你的评论吧 !