LMK00725 芯片技术文档总结

描述

该LMK00725是一款低偏斜、高性能时钟扇出缓冲器,可从两个输入之一分配多达五个3.3V LVPECL输出,该输入可接受差分或单端输入。时钟使能输入在内部同步,以消除时钟使能引脚置位或取消置位时输出上的欠幅或毛刺脉冲。低附加抖动和相位本底噪声以及确保的输出和器件间偏斜特性使该LMK00725成为需要高性能和可重复性的应用的理想选择。

*附件:lmk00725.pdf

特性

- 5个3.3V差分LVPECL输出

- 附加抖动:43 fs RMS(典型值)@ 312.5 MHz

- 本底噪声(≥1 MHz 偏移):

–158 dBc/Hz(典型值)@ 312.5 MHz - 输出频率:650 MHz(最大值)

- 输出偏斜:35 ps(最大值)

- 零件间偏斜:100 ps(最大值)

- 传播延迟:0.37 ns(最大值)

- 两个差分输入对(引脚可选)

- CLKx、nCLK输入对可以接受LVPECL、LVDS、

HCSL、SSTL、LVHSTL或单端

信号

- CLKx、nCLK输入对可以接受LVPECL、LVDS、

- 同步时钟使能

- 电源:3.3V ±5%

- 封装:20引脚TSSOP

- 工业温度范围:–40°C 至 +85°C

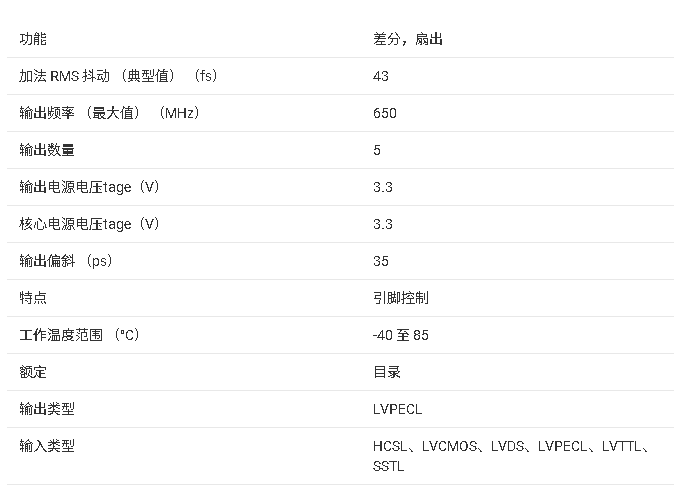

参数

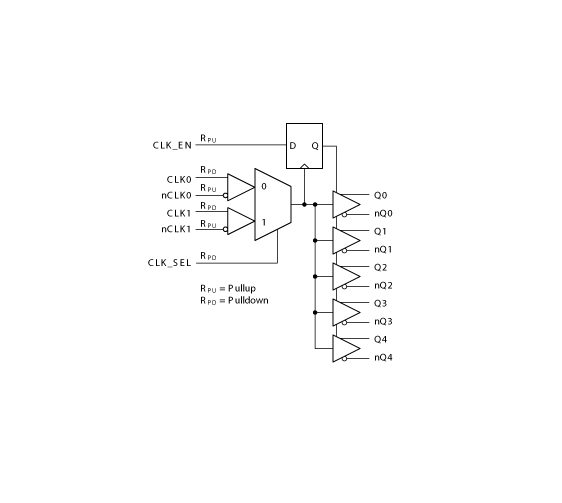

方框图

1. 产品概述

LMK00725是德州仪器(TI)推出的高性能低偏移时钟扇出缓冲器,可将1路差分输入转换为5路3.3V LVPECL输出,适用于对时序精度要求严苛的应用场景。其核心特性包括:

- 超低抖动:典型附加抖动43 fs RMS(312.5 MHz时)

- 低噪声:噪声底限-158 dBc/Hz(1 MHz偏移)

- 高频率支持:最大输出频率650 MHz

- 低延迟:最大传播延迟0.37 ns

- 宽温支持:工业级温度范围(-40°C至+85°C)

2. 关键特性

- 输入灵活性:支持LVPECL、LVDS、HCSL、SSTL等多种差分或单端输入信号

- 同步使能:时钟使能(CLK_EN)功能可消除输出端的毛刺

- 低偏移控制:输出偏移最大35 ps,器件间偏移最大100 ps

- 封装:20引脚TSSOP封装

3. 典型应用

- 无线/有线通信基础设施

- 网络与数据通信设备

- 服务器及高性能计算

- 医疗成像设备

- 高端音视频系统

4. 功能架构

- 双差分输入通道(CLK0/nCLK0、CLK1/nCLK1),通过CLK_SEL引脚选择

- 五组LVPECL输出对(Q0/nQ0至Q4/nQ4)

- 内部集成同步使能逻辑和输入偏置电阻(RPU/RPD)

5. 电气特性

- 电源要求:3.3V ±5%

- 功耗:典型60 mA静态电流,全负载时总功耗约343 mW

- ESD防护:需遵循防静电操作规范

6. 设计注意事项

- 热管理:建议通过多层PCB、增加铜厚和散热过孔控制结温

- 电源滤波:推荐每电源引脚配置0.1μF去耦电容,必要时添加磁珠隔离

- 未用引脚处理:输入引脚需按规范偏置,输出引脚可悬空或端接

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

LMK04011 低噪声时钟抖动清除器技术文档总结2025-09-18 909

-

LMK04000系列低噪声时钟抖动清除器技术文档总结2025-09-17 925

-

LMK04102 抖动清除器技术文档总结2025-09-16 869

-

LMK04906 超低噪声时钟抖动消除器与倍频器技术文档总结2025-09-15 1106

-

LMK1D2104L 系列超低附加抖动LVDS缓冲器技术文档总结2025-09-10 866

-

当LMK00725的输入为LVPECL电平时,由于芯片输入管脚内部存在51KOhm上下拉,在芯片外部是否还需要增加上下拉偏置电阻呢?2024-11-11 518

-

LMK00725低电压正射极耦合逻辑(LVPECL)扇出缓冲器数据表2024-08-23 455

-

基于JESD204B的LMK04821芯片项目开发2023-01-05 2458

全部0条评论

快来发表一下你的评论吧 !