LMK04816 高性能时钟调节器总结

描述

LMK04816 器件是业界性能最高的时钟调理器,具有卓越的性能 时钟抖动清理、生成和分配,具有满足下一代需求的高级功能 系统要求。双环路PLLATINUM架构支持111 fs RMS抖动(12 kHz至12 kHz 20 MHz)或低于200 fs RMS抖动(12 kHz至20 MHz)使用低噪声VCXO模块 低成本的外部晶体和变容二极管。

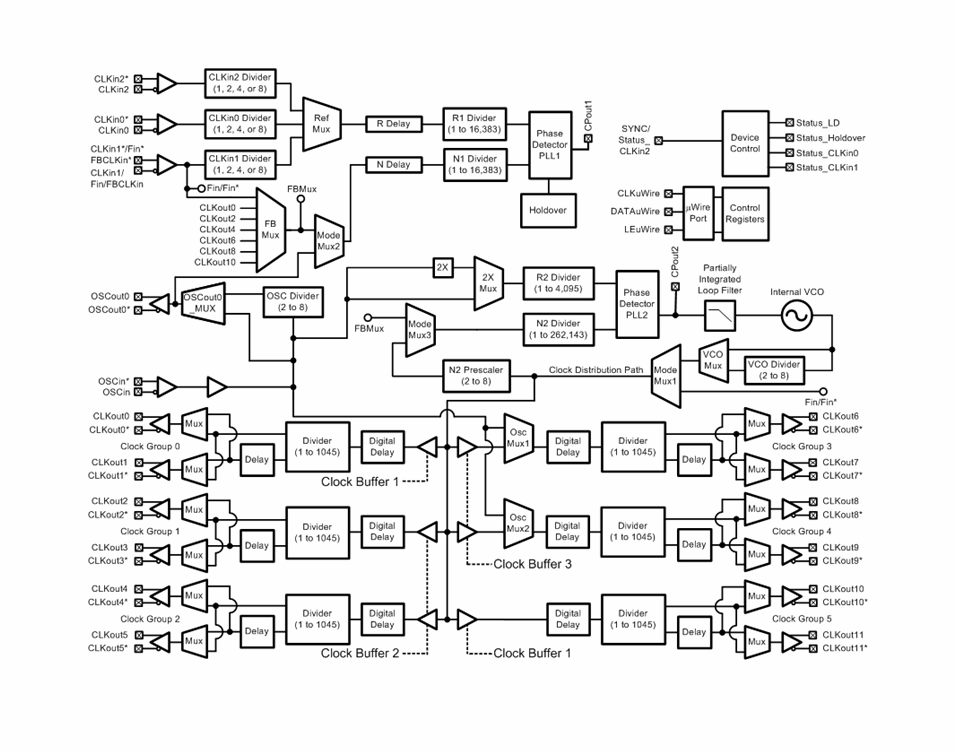

双环架构由两个高性能锁相环 (PLL) 组成,一个 低噪声晶体振荡器电路和高性能压控振荡器 (VCO)。 第一个PLL(PLL1)提供低噪声抖动清除器功能,而第二个PLL(PLL2) 执行时钟生成。PLL1 可以配置为与外部 VCXO 模块配合使用 或带有外部可调谐晶体和变容二极管的集成晶体振荡器。使用时 PLL1具有非常窄的环路带宽,使用优异的近相位噪声(偏移低于50 kHz)的 VCXO 模块或可调谐晶体来清洁输入时钟。使用 PLL1 的输出 作为PLL2的干净输入基准,锁定集成VCO。PLL2的环路带宽 可以优化以清除集成VCO 优于 PLL1 中使用的 VCXO 模块或可调谐晶体。

*附件:lmk04816.pdf

特性

- 超低RMS抖动性能

- 100 fs RMS 抖动(12 kHz 至 20 MHz)

- 123 fs RMS 抖动(100 Hz 至 20 MHz)

- 双环路PLLATINUM™ PLL架构

- PLL1

- 集成低噪声晶体振荡器

电路 - 输入时钟丢失时的保持模式

- 自动或手动触发和

恢复

- 自动或手动触发和

- 集成低噪声晶体振荡器

- PLL2

- 归一化1Hz PLL本底噪声为

–227 dBc/Hz - 相位检测器速率高达 155 MHz

- OSCin 倍频器

- 集成低噪声VCO

- VCO 频率范围为 2370 MHz

至 2600 MHz

- 归一化1Hz PLL本底噪声为

- PLL1

- 三个带LOS的冗余输入时钟

- 自动和手动切换模式

- 50% 占空比输出分频,1 至 1045(偶数

和奇数) - LVPECL、LVDS或LVCMOS可编程

输出 - 精密数字延迟,固定或动态

可调 - 25 ps 步进模拟延迟控制,高达 575 ps

- 1/2 时钟分配周期步进数字延迟,

高达 522 步 - 13 个差分输出;多达 26 个单端

- 多达5个VCXO和晶体缓冲输出

- 时钟速率高达 2600 MHz

- 0-延迟模式

- 上电时三个默认时钟输出

- 多模:双 PLL、单 PLL 和时钟

分配 - 工业温度范围:–40°C 至 +85°C

- 3.15V 至 3.45V 工作电压

- 封装:64 引脚 WQFN (9.0 × 9.0 × 0.8 mm)

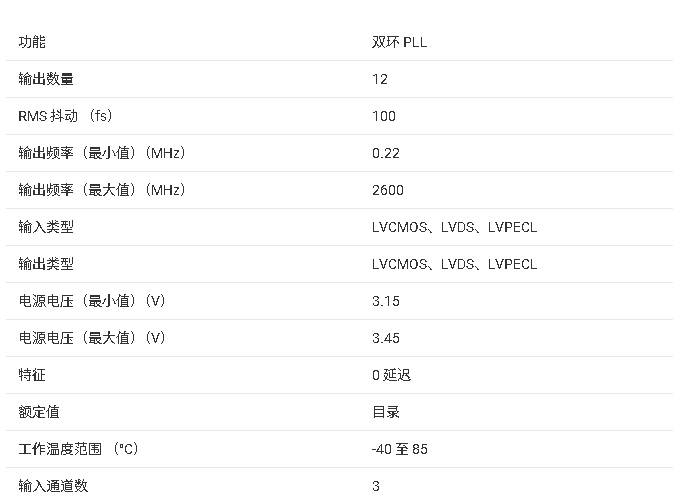

参数

方框图

LMK04816是德州仪器(TI)推出的高性能时钟调节器,专为低噪声时钟抖动清理、生成和分配设计,适用于下一代系统需求。以下是核心要点总结:

1. 关键特性

- 超低RMS抖动性能:12 kHz至20 MHz带宽下仅100 fs,100 Hz至20 MHz带宽下123 fs。

- 双环PLL架构:

- PLL1:集成低噪声晶体振荡器电路,支持输入时钟丢失时的保持模式(Holdover)。

- PLL2:归一化1 Hz PLL噪声低至-227 dBc/Hz,相位检测速率高达155 MHz,集成低噪声VCO(2370 MHz至2600 MHz)。

- 冗余输入时钟:3路冗余输入(CLKin0/1/2),支持自动/手动切换。

- 灵活输出配置:

- 13个差分输出(最多26个单端输出),支持LVPECL、LVDS或LVCMOS可编程输出。

- 50%占空比分频(1至1045,支持奇偶分频)。

- 精密延迟控制:

- 数字延迟(25 ps步进,最大575 ps)。

- 模拟延迟(半时钟周期步进,最多522步)。

2. 主要应用

- 数据转换器时钟和无线基础设施。

- 网络通信(SONET/SDH、DSLAM)。

- 医疗、视频、军事及航空航天设备。

- 测试与测量仪器。

3. 功能描述

- 双环PLL架构:PLL1用于抖动清理,PLL2用于时钟生成,结合VCXO或晶体优化相位噪声。

- 输入切换模式:支持手动、引脚选择和自动切换,确保时钟冗余。

- 保持模式(Holdover) :在输入时钟丢失时维持输出频率稳定性。

- 时钟同步(SYNC) :支持多输出相位对齐,可通过数字延迟调整相对相位。

- 0延迟模式:通过内部或外部反馈路径实现输入与输出时钟的相位同步。

4. 工作模式

- 双环模式(默认):PLL1清理输入时钟,PLL2生成低噪声输出。

- 单环模式:禁用PLL1,直接使用PLL2和OSCin参考。

- 时钟分配模式:将CLKin1直接分配至输出,支持分频和延迟。

- 外部VCO模式:通过Fin端口接入外部VCO,扩展频率范围。

5. 编程与控制

- 寄存器配置:通过MICROWIRE接口编程32位寄存器,支持时钟分频、延迟、输出类型等参数设置。

- 动态数字延迟:支持实时调整输出相位,最小步进为半时钟周期。

- 状态监控:通过专用引脚(如Status_LD、Status_Holdover)输出锁相状态、保持模式等信号。

6. 封装与电气特性

- 封装:64引脚WQFN(9.0 × 9.0 × 0.8 mm)。

- 工作电压:3.15 V至3.45 V。

- 温度范围:-40°C至+85°C(工业级)。

总结:LMK04816凭借其双环PLL架构、超低抖动和灵活配置,成为高性能时钟管理的理想选择,适用于对时序要求严苛的通信、医疗和测试设备。其丰富的功能模式和可编程性使其能够适应多样化的系统需求。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

深入剖析LMK03000系列精密时钟调节器:特性、应用与设计要点2026-02-10 560

-

LMK04816:高性能时钟调节器的全面解析2026-02-09 195

-

探索LMK04832:高性能时钟调节器的卓越之选2026-02-08 448

-

LMK03000系列精密时钟调节器技术文档总结2025-09-18 1142

-

LMK03200精密时钟调节器技术文档总结2025-09-17 953

-

LMK04816具有双环PLL的三输入低噪声时钟抖动消除器数据表2024-08-22 520

-

LMK03002/LMK03002C精密时钟调节器数据表2024-08-21 384

-

LMK04816 具有双环 PLL 的三输入低噪声时钟抖动消除器2022-07-26 623

全部0条评论

快来发表一下你的评论吧 !