Texas Instruments CDCBT1001时钟缓冲器与电平转换器技术解析

描述

Texas Instruments CDCBT1001时钟缓冲器和电平转换器是一款1.2V至1.8V时钟缓冲器和电平转换器,用于个人电子、服务器和附加卡。VDD_IN引脚电源电压定义输入LVCMOS时钟电平。VDD_OUT引脚电源电压定义输出LVCMOS时钟电平。VDD_IN = 1.2V ±10%. VDD_OUT = 1.8V ±10%. Texas Instruments CDCBT1001在24MHz时具有小于0.8ps(12kHz至5MHz)附加RMS抖动。

数据手册:*附件:Texas Instruments CDCBT1001时钟缓冲器和电平转换器数据手册.pdf

特性

- 时钟频率范围:直流至24MHz

- 1.2V至1.8V LVCMOS时钟电平转换

- VDD_IN = 1.2V ± 10%

- VDD_OUT = 1.8V ± 10%

- 低附加抖动和相位噪声

- 12kHz至5MHz附加RMS抖动 (f

out= 24MHz):最大0.8ps - 最大相位噪声:–120dBc/Hz(1kHz偏移)(f

out= 24MHz) - 最大相位噪底:–148dBc/Hz (f

out= 24MHz,f偏移≥ 1MHz)

- 12kHz至5MHz附加RMS抖动 (f

- 20%至80%上升/下降时间:5ns

- 10ns传播延迟

- 低电流消耗

- 工作温度范围:–40°C至85°C

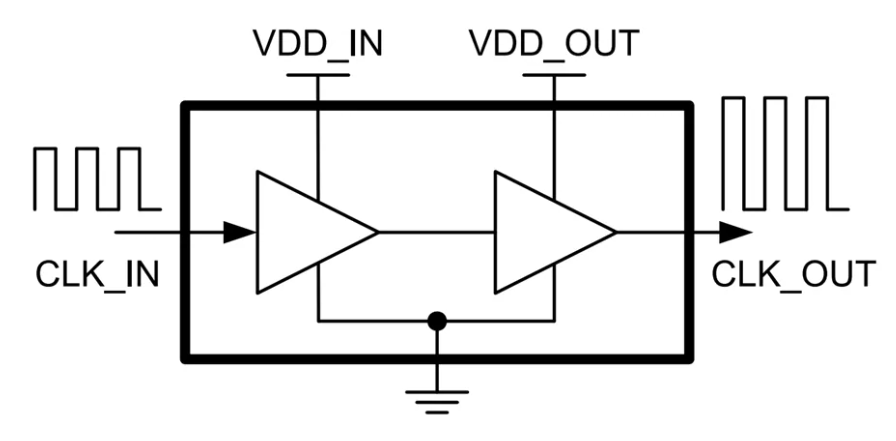

功能框图

Texas Instruments CDCBT1001时钟缓冲器与电平转换器技术解析

一、产品概述

CDCBT1001是德州仪器(TI)推出的一款高性能时钟缓冲器和电平转换器芯片,采用紧凑型X2SON-5封装(0.8mm×0.8mm)。该器件专为1.2V至1.8V系统间的时钟信号转换而设计,具有超低抖动和相位噪声特性。

关键特性

- 电压转换范围:支持1.08V-1.32V输入到1.62V-1.98V输出的电平转换

- 频率范围:DC至24MHz

- 抖动性能:12kHz-5MHz范围内附加RMS抖动<0.8ps(24MHz时)

- 相位噪声:1kHz偏移时最大-120dBc/Hz,1MHz偏移时噪声基底达-148dBc/Hz

- 快速响应:上升/下降时间5ns(20%-80%),传播延迟10ns

- 低功耗:工作电流典型值35μA(12MHz时)

二、电气特性与性能参数

1. 绝对最大额定值

- VDD_IN电压:-0.5V至1.5V

- VDD_OUT电压:-0.5V至2.25V

- 输入电压:-0.5V至1.5V

- 工作温度:-40°C至85°C

2. 典型工作条件

- VDD_IN:1.2V±10%(1.08V-1.32V)

- VDD_OUT:1.8V±10%(1.62V-1.98V)

3. 关键性能指标

- 输入特性:

- VIH≥0.8×VDD_IN

- VIL≤0.2×VDD_IN

- 输入电容典型值2pF

- 输出特性:

- VOH=VDD_OUT-0.1V(IOH=-100μA时)

- VOL=0.1V(IOL=100μA时)

- 输出阻抗34Ω

三、典型应用设计

1. 处理器时钟电平转换

典型应用电路如图8-1所示,实现1.2V处理器与1.8V系统控制器间的时钟信号转换:

- 输入侧连接1.2V处理器时钟输出

- 输出侧连接1.8V系统控制器时钟输入

- 电源端各配置0.1μF去耦电容

2. 设计注意事项

- 电源设计:

- 建议每个电源引脚配置0.1μF陶瓷去耦电容(0402封装)

- 保持电源噪声最小化

- 布局指南:

- 时钟走线尽可能短,避免直角转弯

- 参考评估模块的4层PCB设计(顶层信号+两层GND+底层辅助)

- 信号走线与电源/地平面保持良好隔离

四、封装与热特性

1. 机械特性

- 封装类型:X2SON-5(DPW)

- 尺寸:0.8mm×0.8mm×0.4mm

- 焊盘间距:0.5mm

2. 热参数

- 结到环境热阻:462.7°C/W

- 结到板热阻:326.5°C/W

- 最大结温:150°C

五、评估与开发支持

TI提供CDCBT1001EVM评估模块(DC189-001)用于性能评估,包含:

- 评估板(DC189-001)

- 完整原理图与PCB设计文件

- 物料清单(BOM)

- 测试连接指南

评估模块采用专业4层PCB设计,包含SMA连接器便于测试设备连接,典型配置下最大电流消耗不超过10mA。

六、应用领域

CDCBT1001特别适用于以下场景:

- 个人电子设备中FPGA/处理器的时钟缓冲与电平转换

- 服务器和扩展卡中的1.2V时钟缓冲系统

- 需要超低抖动时钟信号的高精度定时应用

- 混合电压系统的时钟分配网络

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Texas Instruments CDCM1804:一款强大的时钟缓冲器,电子工程师的得力助手2026-02-10 353

-

深入解析LMK00105:超低抖动LVCMOS扇出缓冲器与电平转换器2026-02-09 316

-

CDCBT1001:高性能时钟缓冲器与电平转换器的深度解析2026-02-06 1033

-

LMK00334四输出时钟缓冲器与电平转换器技术文档总结2025-09-15 1022

-

CDCBT1001 1.2V至1.8V时钟缓冲器与电平转换器技术文档总结2025-09-11 1147

-

Texas Instruments SN74HC240八通道缓冲器/线路驱动器数据手册2025-07-23 923

-

Texas Instruments SN74AHCT367六路缓冲器和线路驱动器数据手册2025-07-14 1188

-

Texas Instruments TXG104x 4位接地电平转换器数据手册2025-07-03 1135

-

CDCBT1001 1.2V至1.8V时钟缓冲器和电平转换器数据表2024-08-20 442

-

什么是时钟缓冲器(Buffer)?时钟缓冲器(Buffer)参数解析2022-10-18 31152

-

CC4049六反相缓冲器/电平转换器中文资料pdf2008-04-07 8221

全部0条评论

快来发表一下你的评论吧 !