fpga开发板 璞致ZYNQ 7000 系列之 PZ7035/PZ7045/PZ7100-FH 核心板与开发板用户手册

电子说

描述

第一章:Zynq7000 系列 FPGA 介绍

Zynq 系列是赛灵思公司(Xilinx)推出的行业第一个可扩展处理平台。旨在为 视频监视、汽车驾驶员辅助以及工厂自动化等高端嵌入式应用提供所需的处理与计 算性能水平。

名称由来

Zynq 这个词很容易让人联想到 zinc,也就是电池、日光屏、合金制品和药品 中最常见的化学元素锌。锌与其他金属的合金可实现增强型功能,根据合金的不同 对象表现为不同的色彩。锌最常见的用途就是电镀,那么这个名称与电镀之间有什 么联系?

在 2010 年 4 月硅谷举行的嵌入式系统大会上,赛灵思发布了可扩展处理平台 的架构详情,这款基于无处不在的 ARM 处理器的SoC 可满足复杂嵌入式系统的高性 能、低功耗和多核处理能力要求。赛灵思可扩展处理平台芯片硬件的核心本质就是 将通用基础双 ARMCortex-A9MPCore 处理器系统作为“主系统”,结合低功耗 28nm 工艺技术,以实现高度的灵活性、强大的配置功能和高性能。由于该新型器件的可 编程逻辑部分基于赛灵思 28nm7 系列 FPGA,因此该系列产品的名称中添加了

“7000”,以保持与 7 系列 FPGA 的一致性,同时也方便日后本系列新产品的命 名。

除了芯片外,赛灵思 Zynq-7000 系列还构成了最终平台产品的基础。赛灵思联 盟计划生态系统和 ARM 互联社区的成员提供的软件开发与硬件设计实现工具、广泛 采用的操作系统、调试器、IP 及其他元素的工具就好像“电镀”在一起一样,从 而使可扩展处理平台成为了可能。

Zynq-7000为何不是FPGA?

Zynq-7000 可扩展处理平台是采用赛灵思新一代 FPGA(Artix-7 与 Kintex-

7FPGA)所采用的同一 28nm 可编程技术的最新产品系列。可编程逻辑可由用户配

置,并通过“互连”模块连接在一起,这样可以提供用户自定义的任意逻辑功能, 从而扩展处理系统的性能及功能。不过,与采用嵌入式处理器的 FPGA 不同,Zynq- 7000 产品系列的处理系统不仅能在开机时启动,而且还可根据需要配置可编程逻 辑。采用这种方法,软件编程模式与全功能的标准 ARM 处理 SoC 毫无二致。

“可扩展”意味着什么?

在软件工程领域,可扩展性(有时会同前向兼容性相混淆)是指实现方案考虑 到未来发展需求的系统设计原理。这是一种能够扩展系统的系统性举措,也是实现 扩展所需的工作。扩展可体现为增加新功能,也可体现为现有功能的修改。其核心 主题就是在尽可能减少现有系统功能变动的基础上实现变革。

在系统架构中,可扩展性意味着系统设计时包含了通过新功能扩展/改进自身 的机制和元素(hook),而且无需对系统基础架构进行较大的修改。良好的架构反映 了实现上述目的的设计原理,也为今后可能的构建工作制定了发展蓝图。请注意, 这通常是指最终交付的产品中包含了尚不会(实际上可能永远不会)用到的功能和 机制,但这种功能并不是可有可无的,而是可维护性的必要元素,有助于避免产品 过早被淘汰。

ZYNQ=processor

Zynq-7000 嵌入式处理平台系列的每款产品均采用带有 NEON 及双精度浮点引擎

的双核 ARMCortex-A9MPCore 处理系统,该系统通过硬连线完成了包括 L1,L2 缓

存、存储器控制器以及常用外设在内的全面集成。该处理系统不仅能在开机时启动 并运行各种独立于可编程逻辑的操作系统(OS),而且还可根据需要配置可编程逻

辑。利用这种方法,软件编程模式与全功能的标准 ARM 处理 SoC 毫无二致。

应用开发人员利用可编程逻辑强大的并行处理能力,不仅可以解决多种不同信 号处理应用中的大量数据处理问题,而且还能通过实施更多外设来扩展处理系统的 特性。系统和可编程逻辑之间的高带宽 AMBA®-AXI 互联能以极低的功耗支持千兆位 级数据传输,从而解决了控制、数据、I/O 和存储器之间的常见性能瓶颈问题。

编程环境

Zynq-7000 系列提供了一个开放式设计环境,便于可编程逻辑中双核 Cortex- A9MPCore 和定制加速器的并行开发,从而加速了产品上市进程。软件开发人员可 以充分利用基于 Eclipse 的 XilinxPlatformStudio 软件开发套件(SDK)、ARM 的 DS-5 和 ARMRealViewDesignSuite(RVDS),或 ARM 互联社区和赛灵思联盟计划生态 系统的领先厂商(诸如 Lauterbach、WindRiver、PetaLogix、MathWorks、

MentorGraphics、Micrium 和 MontaVista 等)提供的编译器、调试器和应用。

此外,利用赛灵思屡获殊荣的 ISE®设计套件的优势,Zynq-7000 系列的可编程 结构经定制可以最大化系统级性能,满足特定应用的各种需求。该套件提供了包括 开发工具、AMB4AXI4 即插即用 IP 核和总线功能模型(BFM)等在内的完整硬件开发 环境,有助于加速设计和验证工作。赛灵思通过收购高级综合技术领先公司

AutoESL 进一步提升了在工具方面的进程,提供 C,C++以及系统 C 综合优化 Zynq- 7000 器件架构。未来的版本也将促进 Zynq-7000 产品系列中处理器和可编程逻辑 之间关键算法的无缝衔接。

随着时间的推移,ARM 互联社区和赛灵思联盟计划生态系统的第三方厂商将进 一步扩展上述解决方案,这是赛灵思目标设计平台的一部分,可提供包括 IP 核、

参考设计、开发套件及其他资源等在内的高效统一的开发环境,从而满足特定应用 和设计领域要求。

可编程逻辑架构

Zynq-7000 系列的可编程逻辑完全基于赛灵思最新 7 系列 FPGA 架构来设计,可 确保 28nm 系列器件的 IP 核、工具和性能 100%兼容。最小型的 Zynq-7000、Zynq- 7010 和 Zynq-7020 均基于专门针对低成本和低功耗优化的Artix-7 系列;较大型 的 Zynq-7030 和 Zynq-7040 器件基于包括 4 至 12 个 10.3Gbps 收发器通道,可支持 高速片外连接的中端 Kintex-7 系列。所有四款产品均采用基于 2 个 12 位

1MspsADC(模数转换器)模块的新型模拟混合信号模块。

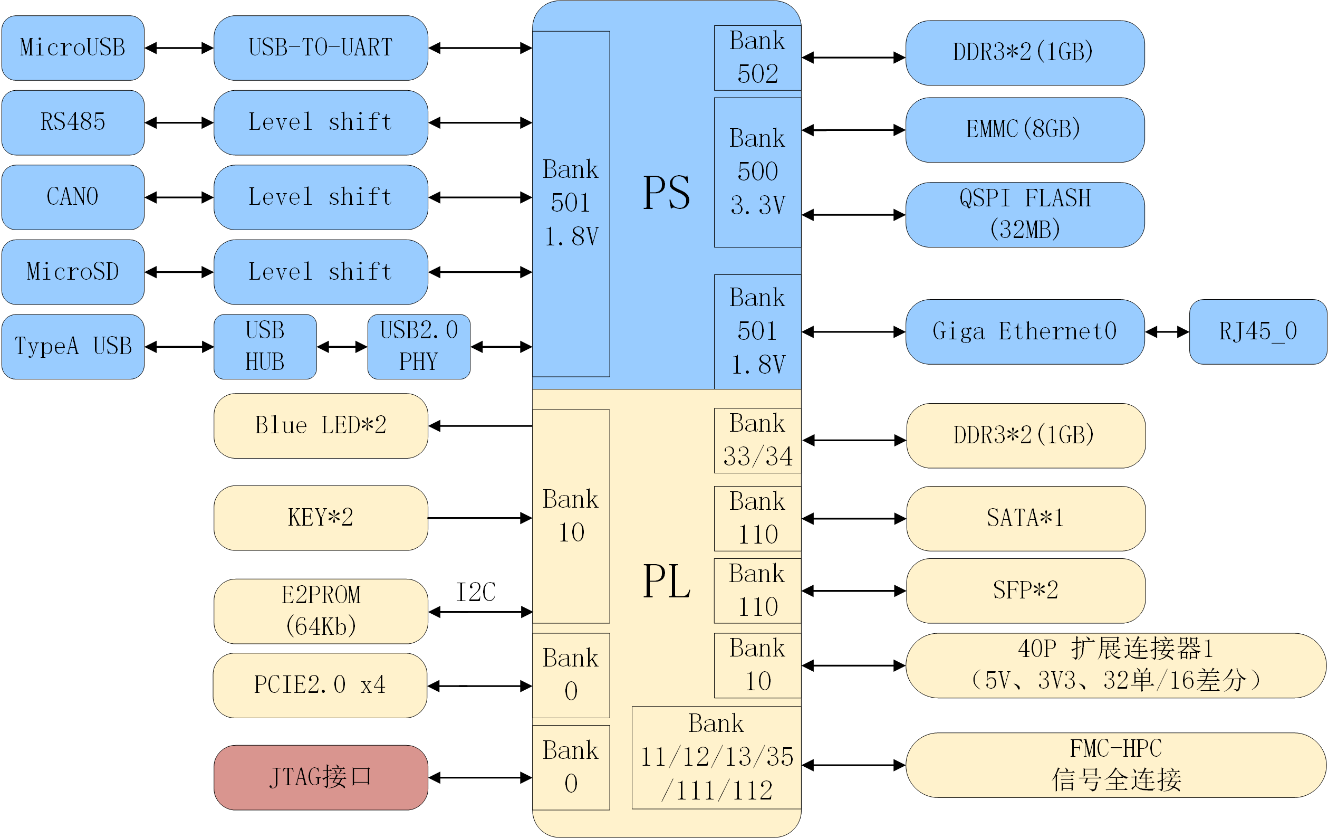

第二章:开发板概述

2.1.开发板概述

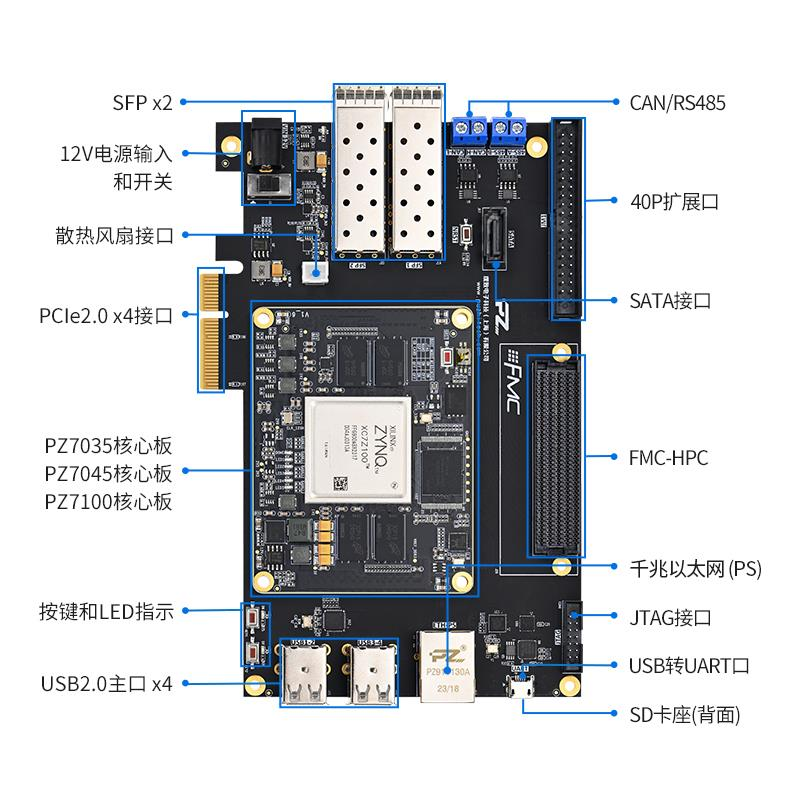

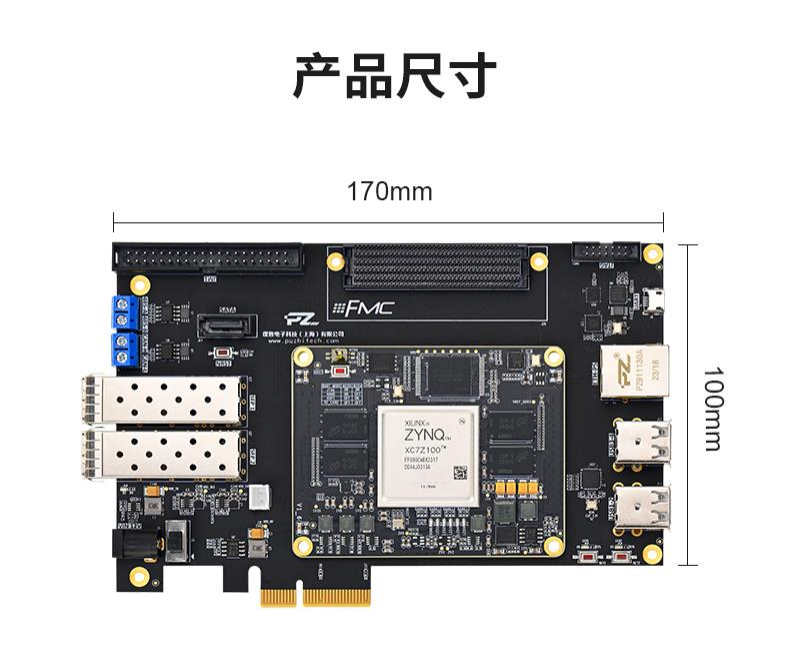

璞致电子科技 PZ7035-FH/PZ7045-FH/PZ7100-FH 开发板采用璞致电子科技自 研的核心板加底板模式。开发板分别采用 XILINX 公司的XC7Z035-2FFG900I、

XC7Z045-2FFG900I 和 XC7Z100-2FFG900I 芯片作为主控制器,三款开发板设计兼 容。开发板集成了丰富的外设资源,提供了详尽的开发例程,为用户的使用与验 证提供便利。如下图我们标示出各个外设在开发板的位置。

核心板通过四个 0.6mm 间距 120P 高速连接器扣接在底板上,使用上更加灵 活。既可以做学习使用,也可以使用核心板用于项目开发。

开发板尺寸为 170x100mm,单板的四个角各放置一个固定孔,用于安装支撑 柱或固定单板,孔径为 3.5mm。

添加图片注释,不超过 140 字(可选)

添加图片注释,不超过 140 字(可选)

添加图片注释,不超过 140 字(可选)

2.2.开发板资源与框图

如下表与框图已列出开发板板载资源,通过下表可以看到开发板所包含的 所有功能。

添加图片注释,不超过 140 字(可选)

添加图片注释,不超过 140 字(可选)

2.3.开发板尺寸

如下图标出开发板尺寸为 170x100mm,开发板的四个角各放置一个固定孔, 用于安装支撑柱或固定单板,孔径为 3.5mm。开发板配置了风扇、散热片以及亚 克力防护板,为方便展示,并没有安装到开发板上,下图列出了散热片和风扇 以及对应尺寸。

添加图片注释,不超过 140 字(可选)

第三章:PZ7035/PZ7045/PZ7100 核心板

3.1.核心板简介

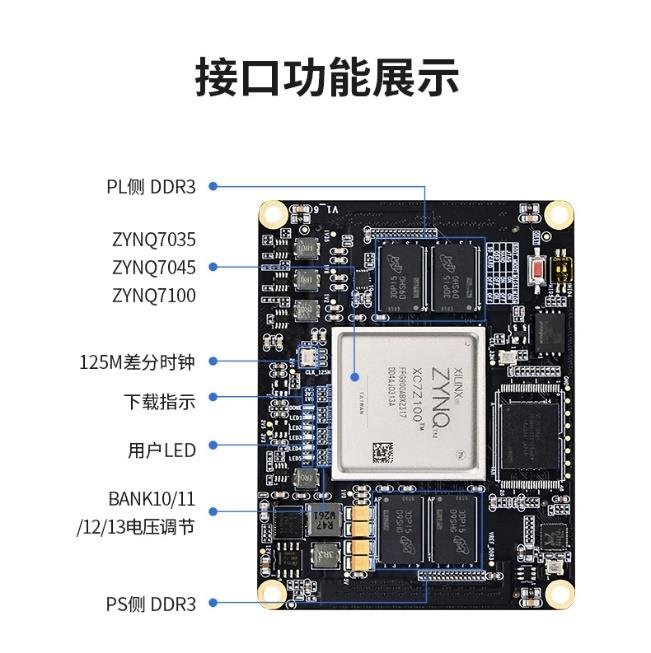

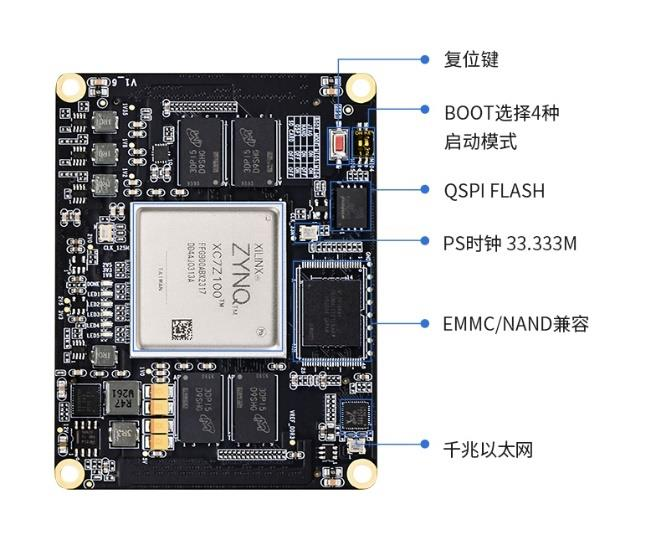

开发板采用了核心板扣接底板的方式,对于开发板的型号取决于使用的核 心板型号。核心板提供 PZ7035-SOM、PZ7045-SOM 和 PZ7100-SOM 三款,三款接 口完全兼容,通过更换核心板方式就可以实现开发板的型号更换。如下表列出 了三款核心板的参数以及之间的差异。

3.2.核心板规格

添加图片注释,不超过 140 字(可选)

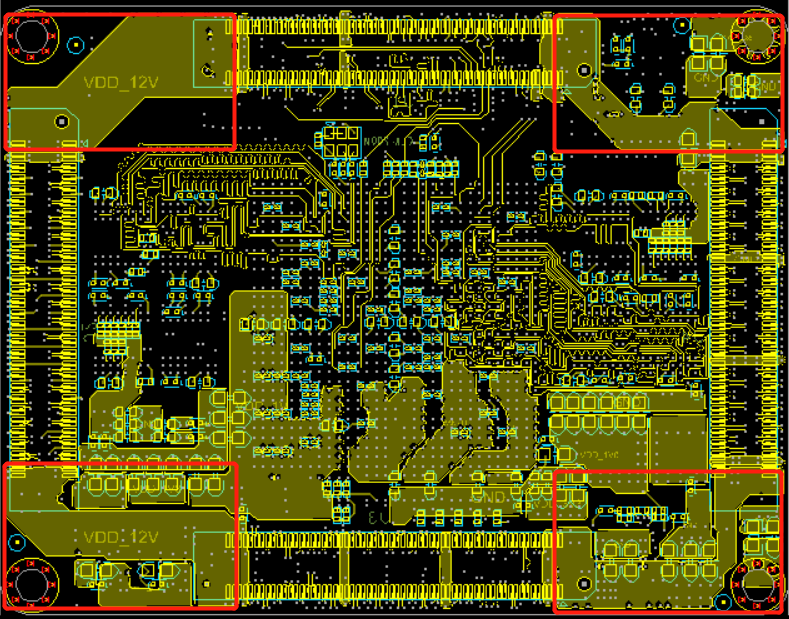

3.3.核心板供电

核心板供电电压范围是 7-12V,在模块的四个角都留有电源输入管脚,电源管脚 在模块内部已做了连通,此设计是为了方便底板的电源接入,设计时只需要连接一 个角上的电源管脚核心板即可工作,电源连接需用铜皮连接且打足够的过孔保证电 源通流能力。模块上的所有 GND 信号都需要连接到底板上,每个 GND 通过两个过孔 与底板连接以确保通流能力。

给模组供电的电源输出电压需要稳定,如果电源不稳定,则需要在模组电源输 入前级加一级 DCDC,从较高电压转到低压,DCDC 电流输出能力可以选 4A 左右,选 择的 DCDC 芯片需要考虑效率,以免芯片发热严重。

在核心板电源输入处需至少放置 2 颗 220uF/25V—470uF/25V 电容保证电源质 量,因核心板电流较大,在成本允许情况下建议核心板单独使用 DCDC 电源供电,

其他外设再用一路电源,电源分开。

添加图片注释,不超过 140 字(可选)

3.4.核心板时钟

核心板为PS侧提供了33.333333Mhz 的时钟输入,输入的管脚位置为PS_CLK_500; 为 PL 侧 提 供 了 200Mhz 的 差 分 时 钟 输 入 , PL 侧 的 时 钟 输 入 管 脚 是 FPGA_13P_MRCC_34/FPGA_13N_MRCC_34,管脚位置是H9/G9;为 GTX 提供了一路 125Mhz 的差分时钟输入,输入位置是 GTX 的 BANK110 的 CLK1,管脚位号是 AC8/AC7 的接入 了如下图列出了连接方式。

需要注意的是:核心板上的 GTX CLK 可以给到 BANK109/110/111 使用,如使用 BANK112,需要在底板上加一路差分 125M 时钟,可以参考开发板原理图连接到 BANK112 的时钟电路。

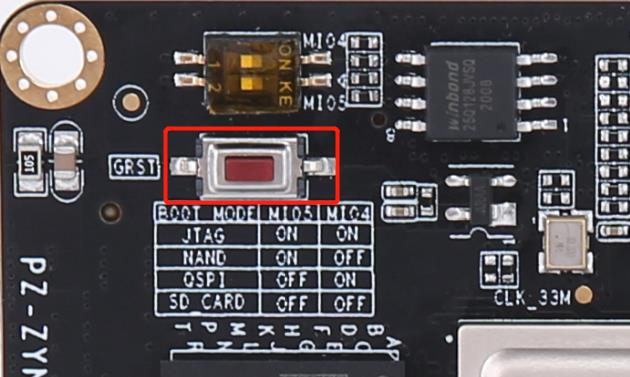

3.5.核心板全局复位

核心板提供了 nGST 复位按键,为系统复位按键,低电平有效。此引脚也引出到 了连接器,信号名称为 SYS_nRST_I,方便用户加入复位按键或者设计看门狗复位电 路。同时为了系统稳定,我们在核心板上加了复位芯片,复位输出信号也引出到了 连接器上,信号名称为 SYS_nRST_O,此信号可以用于单板其他外设的复位用,信号 电平是 3.3V。复位脚为 PS/PL 侧共用复位,分别连接到 PS 侧的 PS_POR_500 和 PL 侧 的 IO_12P_9(管脚位置 AD18)引脚上。

如果底板上需要设计复位电路有以下几种情况需考虑。

1)复位电路底板内部使用,只需要对地添加复位按键和一个 0.1uF 电容并口即 可。

2)复位电路需要预留在结构上供外部使用,需要添加对地按键,同时对地并联 0.1uF 电容和 TVS 防静电器件。

添加图片注释,不超过 140 字(可选)

3.7.网口连接

核心板上设计了一颗千兆以太网芯片,以太网芯片与 ZYNQ 芯片之间通过 RGMII 接口互联,连接对应管脚见下表,以太网对外连接只需要一个带变压器的 RJ45 即可 使用,芯片地址 PHY_AD[2:0]=001,连接原理图可参考下图

注意:产品电路需要在网口信号线和 LED 上加静电防护,0.1uF 电容选用耐压 2KV 或者 3KV。

| RMGII 信号 | 管脚名称 | 管脚位置 |

|---|---|---|

| GTX_CLK | MIO16_501 | L19 |

| TXD0 | MIO17_501 | K21 |

| TXD1 | MIO18_501 | K20 |

| TXD2 | MIO19_501 | J20 |

| TXD3 | MIO20_501 | M20 |

| TX_EN | MIO21_501 | J19 |

| RX_CLK | MIO22_501 | L20 |

| RXD0 | MIO23_501 | J21 |

| RXD1 | MIO24_501 | M19 |

| RXD2 | MIO25_501 | G19 |

| RXD3 | MIO26_501 | M17 |

| RX_CTL | MIO27_501 | G20 |

| MDC | MIO52_501 | D19 |

| MDIO | MIO53_501 | C18 |

添加图片注释,不超过 140 字(可选)

3.8.EMMC管脚定义

板载 EMMC 容量 8GB,工作温度为-40℃--+85℃,管脚定义如下表。

| EMMC 引脚 | 管脚名称 | 管脚位置 |

|---|---|---|

| EMMC_D0 | MIO10 | E22 |

| EMMC_D1 | MIO13 | F22 |

| EMMC_D2 | MIO14 | B22 |

| EMMC_D3 | MIO15 | C22 |

| EMMC_CLK | MIO12 | E21 |

| EMMC_CMD | MIO11 | A23 |

添加图片注释,不超过 140 字(可选)

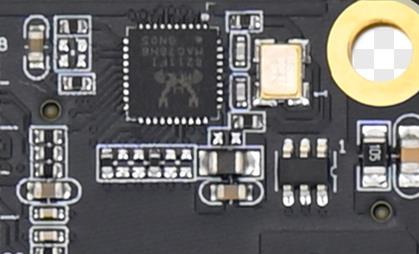

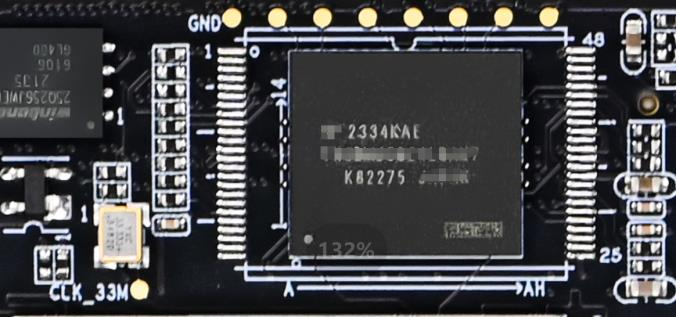

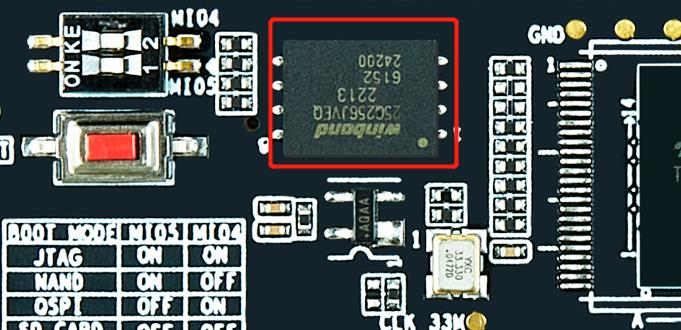

3.9.QSPIFLASH

核心板设计了一路 QSPI FLASH,容量为 256Mb,用户可以定义为 QSPI X4 来加 速启动。QSPI FLASH 可用于存储启动文件和用户文件。

| QSPI FLASH 引脚 | 管脚名称 | 管脚位置 |

|---|---|---|

| DATA0 | MIO2 | F23 |

| DATA1 | MIO3 | C23 |

| DATA2 | MIO4 | E23 |

| DATA3 | MIO5 | C24 |

| QSPI_CS | MIO1 | D23 |

| QSPI_CLK | MIO6 | D24 |

添加图片注释,不超过 140 字(可选)

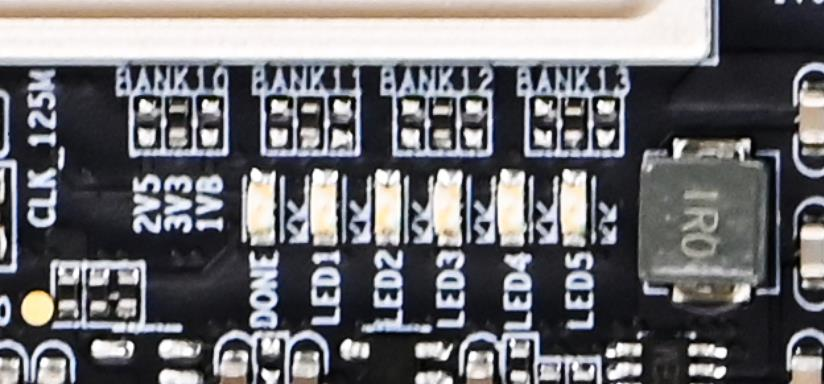

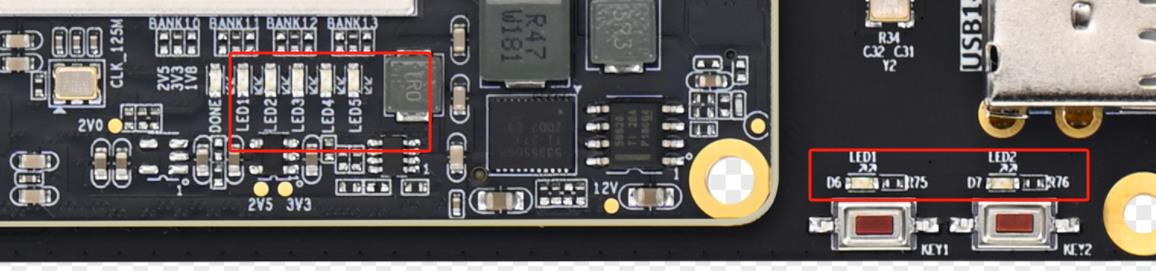

3.10.板载LED

为方便调试,核心板上放置了五颗 LED,LED 连接到 PL 侧,LED 的管脚位置如下 表,当管脚输出高电平时 LED 点亮,低电平 LED 灭。

| 序号 | 管脚名称 | 管脚位置 |

|---|---|---|

| LED1 | IO-L13N-9 | AA19 |

| LED2 | IO-L14P-9 | AB19 |

| LED3 | IO-L14N-9 | AB20 |

| LED4 | IO-L19P-9 | AD20 |

| LED5 | IO-L19N-9 | AE20 |

添加图片注释,不超过 140 字(可选)

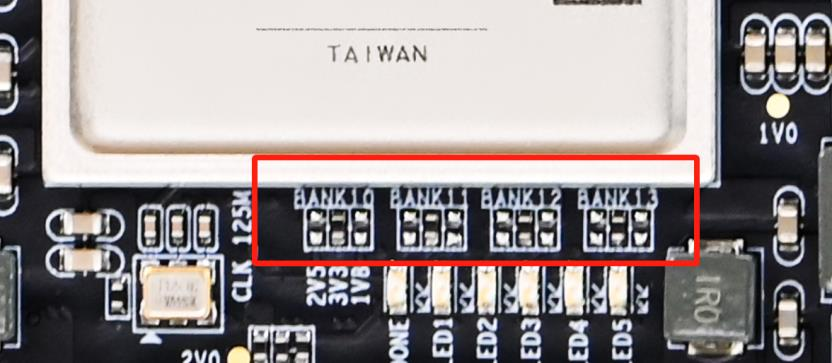

3.11.BANK接口电平选择

单板上 BANK35 为 HP BANK,接口电平固定为 1.8V,BANK10/11/12/13 都可以通 过单板上提供的指示进行 0 欧姆电阻选焊,实现 1.8V/2.5V/3.3V 三种电平转换。更 换电阻位置如下图示,顺序从左到右分别是 2.5V/3.3V/1.8V 选择,默认焊接 3.3V 位 置,即 BANK10/11/12/13 默认接口电平为 3.3V。

添加图片注释,不超过 140 字(可选)

3.12.PS侧DDR

PS 侧配置了两颗工业级 DDR3 芯片,单颗容量 512Mb,两颗共计容量为 1GB, DDR3 管脚分配直接调用系统分配即可。也可以参考我司提供的例程。

15 / 32

3.13.PL侧DDR

PL 侧配置了两颗工业级 DDR3 芯片,单颗容量 512Mb,两颗共计容量为 1GB,型号 为 MT41K256M16TW-107IT:P,DDR3 管脚分配参见下表。

| DDR3 引脚 | 管脚名称 | 管脚位置 |

|---|---|---|

| DDR3_D0 | IO-L1N-33 | J3 |

| DDR3_D1 | IO-L4N-33 | L2 |

| DDR3_D2 | IO-L1P-33 | J4 |

| DDR3_D3 | IO-L4P-33 | L3 |

| DDR3_D4 | IO-L2N-33 | K1 |

| DDR3_D5 | IO-L6P-33 | K6 |

| DDR3_D6 | IO-L5N-33 | J5 |

| DDR3_D7 | IO-L5P-33 | K5 |

| DDR3_DM0 | IO-L2P-33 | L1 |

| DDR3_DQS_P0 | IO-L3P-33 | K3 |

| DDR3_DQS_N0 | IO-L3N-33 | K2 |

| DDR3_D8 | IO-L11P-33 | H4 |

| DDR3_D9 | IO-L10N-33 | G1 |

| DDR3_D10 | IO-L8P-33 | H6 |

| DDR3_D11 | IO-L7N-33 | F2 |

| DDR3_D12 | IO-L10P-33 | H2 |

| DDR3_D13 | IO-L12N-33 | G4 |

| DDR3_D14 | IO-L8N-33 | G6 |

| DDR3_D15 | IO-L11N-33 | H3 |

| DDR3_DM1 | IO-L12P-33 | G5 |

| DDR3_DQS_P1 | IO-L9P-33 | J1 |

| DDR3_DQS_N1 | IO-L9N-33 | H1 |

| DDR3_D16 | IO-L18P-33 | E1 |

| DDR3_D17 | IO-L17P-33 | E3 |

| DDR3_D18 | IO-L16N-33 | D3 |

| DDR3_D19 | IO-L14P-33 | F4 |

| DDR3_D20 | IO-L18N-33 | D1 |

| DDR3_D21 | IO-L13N-33 | E5 |

| DDR3_D22 | IO-L16P-33 | D4 |

| DDR3_D23 | IO-L17N-33 | E2 |

| DDR3_DM2 | IO-L14N-33 | F3 |

| DDR3_DQS_P2 | IO-L15P-33 | E6 |

| DDR3_DQS_N2 | IO-L15N-33 | D5 |

| DDR3_D24 | IO-L22P-33 | C2 |

| DDR3_D25 | IO-L24N-33 | A2 |

| DDR3_D26 | IO-L20N-33 | B4 |

| DDR3_D27 | IO-L20P-33 | B5 |

| DDR3_D28 | IO-L22N-33 | C1 |

|---|---|---|

| DDR3_D29 | IO-L24P-33 | A3 |

| DDR3_D30 | IO-L19P-33 | C4 |

| DDR3_D31 | IO-L23P-33 | B2 |

| DDR3_DM3 | IO-L23N-33 | B1 |

| DDR3_DQS_P3 | IO-L21P-33 | A5 |

| DDR3_DQS_N3 | IO-L21N-33 | A4 |

| DDR3_A0 | IO-L18P-34 | H7 |

| DDR3_A1 | IO-L21P-34 | L8 |

| DDR3_A2 | IO-L7N-34 | H11 |

| DDR3_A3 | IO-L10N-34 | D10 |

| DDR3_A4 | IO-L15N-34 | H8 |

| DDR3_A5 | IO-L8N-34 | D11 |

| DDR3_A6 | IO-L19P-34 | L7 |

| DDR3_A7 | IO-L10P-34 | E10 |

| DDR3_A8 | IO-L23P-34 | L10 |

| DDR3_A9 | IO-L9P-34 | H12 |

| DDR3_A10 | IO-L18N-34 | G7 |

| DDR3_A11 | IO-L20N-34 | J9 |

| DDR3_A12 | IO-L14P-34 | F9 |

| DDR3_A13 | IO-L7P-34 | J11 |

| DDR3_A14 | IO-L22N-34 | K10 |

| DDR3_BA0 | IO-L22P-34 | K11 |

| DDR3_BA1 | IO-L21N-34 | K8 |

| DDR3_BA2 | IO-L9N-34 | G11 |

| DDR3_CS | IO-L16P-34 | F8 |

| DDR3_RAS | IO-L14N-34 | E8 |

| DDR3_CAS | IO-L17P-34 | E7 |

| DDR3_WE | IO-L16N-34 | F7 |

| DDR3_ODT | IO-L20P-34 | J10 |

| DDR3_RESET | IO-L8P-34 | E11 |

| DDR3_CLK_P | IO-L12P-34 | D9 |

| DDR3_CLK_N | IO-L12N-34 | D8 |

| DDR3_CKE | IO-L17N-34 | D6 |

3.14.核心板信号与等长

核心板引出到连接器的信号都做了严格等长,可以参考璞致提供的信号等长表 格,里面详细列出了信号名称和信号走线长度。

3.15.核心板封装库

为方便用户快速使用核心板,我们提供了对应的封装库,连接器相对位置和核 心板外框丝印都已摆放好,直接调用即可。原理图封装提供 AD/ORCAD 两个版本,PCB 封装提供 AD/Allegro 两个版本,均已存放在对应的文件夹下。另外,文件夹下提供 了核心板的 DXF 文件,方便用户对应结构。

3.16.核心板对应连接器

核心板采用了两个高密连接器与底板连接,底板上使用的连接器对应型号是 FX8-120S-SV,用户可以自行购买,也可以联系璞致客服购买。

第四章PZ7035/PZ7045/PZ7100 底板

4.1.电源供电

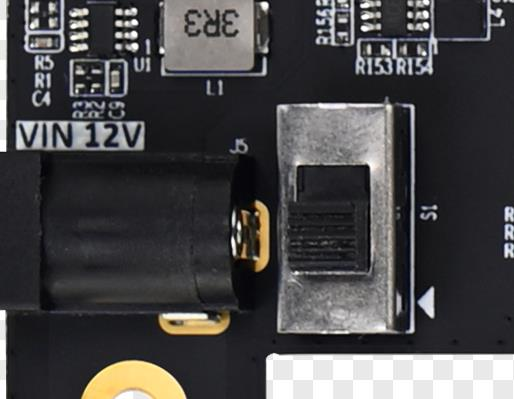

开发板采用 12V/3A 的适配器供电,电源接入后通过 DCDC 转换成 8V、5V、3.3V 等多路电压供板内器件使用。接入 12V 电源可以通过开关 S1开关来控制通断, 电源 部分详细电路可参考开发板对应的原理图。

添加图片注释,不超过 140 字(可选)

4.2.时钟电路

时钟电路主要设计在核心板上,核心板为 PS 侧提供了 33.33Mhz 的时钟输入, 输入的管脚位置为 PS_CLK_500;为 PL 侧提供了 200Mhz/125Mhz 时钟,详细电路可 参考核心板时钟电路部分说明或核心板原理图。

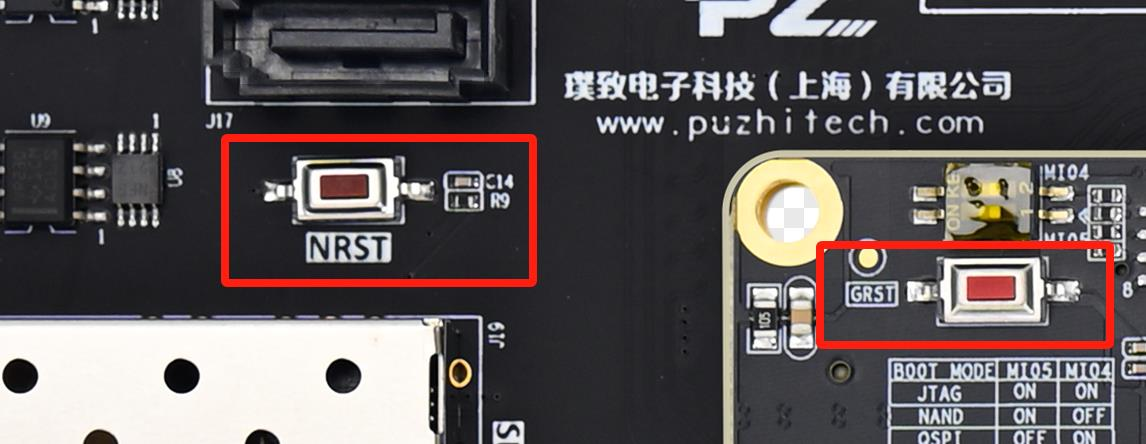

4.3.复位电路

开发板上有两个复位按键,一路集成到核心板上了,一路在开发板上。复位信 号名称是 SYS_nRST_I 。 同 时为 了系 统稳定 ,我们在核 心板上加 了 复位芯 片 MAX811TUES,复位输出信号也引出到了连接器上,信号名称为 SYS_nRST_O,此信号 可以用于单板其他外设的复位用,信号电平是 3.3V。复位脚为 PS/PL 侧共用复位, 分别连接到 PS 侧的 PS_POR_500 和 PL 侧的 IO_12P_9(管脚位置 AD18)引脚上。

添加图片注释,不超过 140 字(可选)

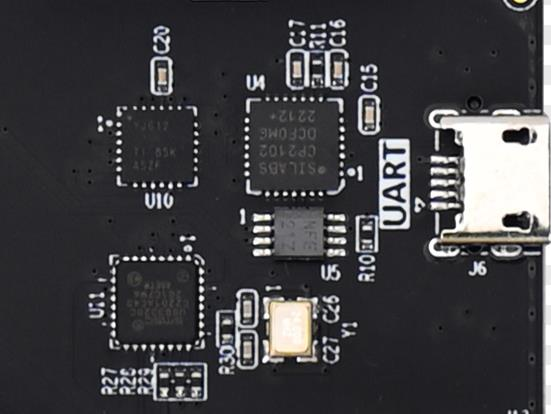

4.4.USB转串口

开发板使用 Silicon Labs CP2102GM 芯片实现 USB 转 UART, USB 接口采用 Micro USB,用户只要用一根 Micro USB 线连接到 PC 上即可进行串口通信开发。

UART 的 TX/RX 信号与 ZYNQ 的 PS 侧BANK501 相连,因为BANK501 的电平为 1.8V, 但 CP2102GM 的数据电平为 3.3V, 所以我们使用 TXS0102DCUR 进行电平转换。

如下是信号对应关系表和原理图,TX/RX 方向为 ZYNQ 端定义。

| UART0 引脚 | 管脚名称 | 管脚位置 |

|---|---|---|

| UART0_TX | MIO47 | A18 |

| UART0_RX | MIO46 | F20 |

添加图片注释,不超过 140 字(可选)

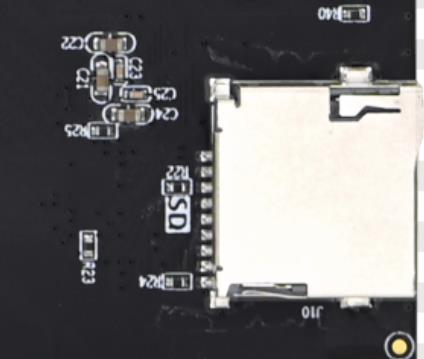

4.5.SD卡

开发板上设计了 SD 卡卡座,与 ZYNQ 的 PS 侧 BANK501 相连,因为 BANK501 的电 平为 1.8V,但 SD 的数据电平为 3.3V,我使用TXS02612RTWR 进行电平转换。

如下是 SD 卡的管脚分配与原理图。

| SD 卡引脚 | 管脚名称 | 管脚位置 |

|---|---|---|

| SD_CLK | MIO40 | B20 |

| SD_CMD | MIO41 | J18 |

| SD_DATA0 | MIO42 | D20 |

| SD_DATA1 | MIO43 | E18 |

| SD_DATA2 | MIO44 | E20 |

| SD_DATA3 | MIO45 | H18 |

添加图片注释,不超过 140 字(可选)

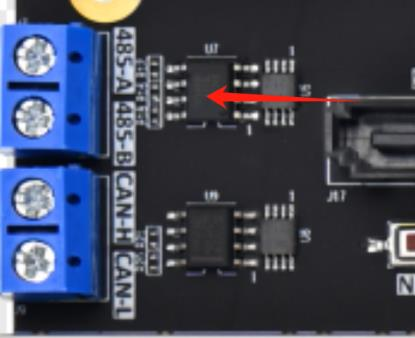

4.6.RS485接口

开发板使用 SP3485 芯片实现 RS485, RS485 对外接口采用 2 脚 KF301 连接器。

RS485 的 TX/RX 信号与 ZYNQ 的 PS 侧 BANK501 相连,即为 URAT1,因为 BANK501 的电平为 1.8V,但 SP3485EN 的数据电平为 3.3V, 所以我们使用 TXS0102DCUR 进行 电平转换。

另外 RS485 为半双工通信,需要做信号方向切换,此部分璞致电子科技已为用户 考虑周全,实现信号发送和接收的自由切换。

如下是信号对应关系表和原理图,TX/RX 方向为 ZYNQ 端定义。

| RS485 引脚 | 管脚名称 | 管脚位置 |

|---|---|---|

| RS485_TX | MIO48 | C19 |

| RS485_RX | MIO49 | D18 |

4.7.CAN接口

开发板使用 SN65HVD230D 芯片实现 CAN 通信, CAN 对外接口采用 2 脚 KF301 连 接器。CAN 的 TX/RX 信号与 ZYNQ 的 PS 侧 BANK501 相连,即为 CAN0,因为 BANK501 的 电平为 1.8V,但 SN65HVD230D 的数据电平为 3.3V, 所以我们使用 TXS0102DCUR 进行 电平转换。

如下是信号对应关系表和原理图,TX/RX 方向为 ZYNQ 端定义。

| CAN 引脚 | 管脚名称 | 管脚位置 |

|---|---|---|

| CAN_TX | MIO51 | F19 |

| CAN_RX | MIO50 | A19 |

添加图片注释,不超过 140 字(可选)

4.8.E2PROM

开发板上放置了一颗 64Kbit 的 EEPROM 芯片,型号为 AT24C64D-SSHM-T,与 FPGA 的 BANK34 通过 IIC 总线相连。EEPROM 读地址是 0xA1,写地址是 0xA0。

如下是 EEPROM 的管脚分配,详细电路可以参考开发板原理图。

| EEPROM 引脚 | 管脚名称 | 管脚位置 |

|---|---|---|

| IIC-SCL | IO-20P-10 | AA15 |

| IIC-SDA | IO-20N-10 | AA14 |

添加图片注释,不超过 140 字(可选)

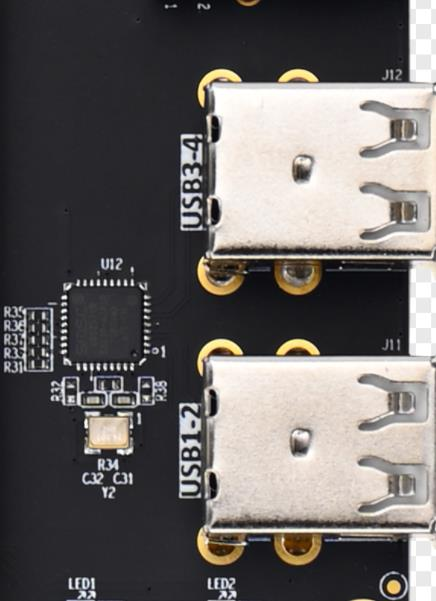

4.9.USB2.0接口

开发板设计了 USB PHY 和 USB HUB 芯片,扩展出 4 个 USB2.0 主接口。USB PHY 需要配置成 OTG 工作模式。

如下是 USB2.0 的引脚分配, 详细电路可以参考开发板原理图。

| USB 引脚 | 管脚名称 | 管脚位置 |

|---|---|---|

| USBPHY_DATA0 | MIO32 | K17 |

| USBPHY_DATA1 | MIO33 | G22 |

| USBPHY_DATA2 | MIO34 | K18 |

| USBPHY_DATA3 | MIO35 | G21 |

| USBPHY_DATA4 | MIO28 | L17 |

22 / 32

| USBPHY_DATA5 | MIO37 | B21 |

|---|---|---|

| USBPHY_DATA6 | MIO38 | A20 |

| USBPHY_DATA7 | MIO39 | F18 |

| USBPHY_STP | MIO30 | L18 |

| USBPHY_NXT | MIO31 | H21 |

| USBPHY_DIR | MIO29 | H22 |

| USBPHY_CLKOUT | MIO36 | H17 |

| USBPHY_nRSET | IO_6P_35 | J16 |

添加图片注释,不超过 140 字(可选)

4.10.千兆以太网

开发板上放置了一颗千兆以太网芯片。已集成到核心板上, 挂接在 PS 侧,我们 定义为 PHY0。以太网芯片与 ZYNQ 芯片之间均通过 RGMII 接口互连。核心板上 PHY0 对外只需要连接集成变压器的 RJ45 即可。PHY0 芯片地址 PHY_AD[2:0]=001,信号连 接参考下表,原理图如下图。

| RMGII 信号 | 管脚名称 | 管脚位置 |

|---|---|---|

| GTX_CLK | MIO16_501 | L19 |

| TXD0 | MIO17_501 | K21 |

| TXD1 | MIO18_501 | K20 |

| TXD2 | MIO19_501 | J20 |

| TXD3 | MIO20_501 | M20 |

| TX_EN | MIO21_501 | J19 |

| RX_CLK | MIO22_501 | L20 |

| RXD0 | MIO23_501 | J21 |

| RXD1 | MIO24_501 | M19 |

| RXD2 | MIO25_501 | G19 |

| RXD3 | MIO26_501 | M17 |

| RX_CTL | MIO27_501 | G20 |

| MDC | MIO52_501 | D19 |

| MDIO | MIO53_501 | C18 |

4.11.SFP接口

开发板上放置了两路 SFP 接口,ZYNQ7035/7045/7100 支持的 GTX 接口最高速度 可以到 10Ghz。GTX 时钟为 125Mhz,输入管脚名称是MGT-CLK1P-110/MGT-CLK1N-110, 管脚位置是 AC8/AC7。

如下表列出了引脚信号对应关系:

| SFP 引脚 | 管脚名称 | 管脚位置 |

|---|---|---|

| SFP1_TX_P | MGT_110_TX_P1 | AF2 |

| SFP1_TX_N | MGT_110_TX_N1 | AF1 |

| SFP1_RX_P | MGT_110_RX_P1 | AG4 |

| SFP1_RX_N | MGT_110_RX_N1 | AG3 |

| SFP1_TX_DISABLE | IO_7P_10 | AE12 |

| SFP1_RxRATE_SEL | IO_7N_10 | AF12 |

| SFP2_TX_P | MGT_110_TX_P0 | AH2 |

| SFP2_TX_N | MGT_110_TX_N0 | AH1 |

| SFP2_RX_P | MGT_110_RX_P0 | AH6 |

| SFP2_RX_N | MGT_110_RX_N0 | AH5 |

| SFP2_TX_DISABLE | IO_10P_10 | AG12 |

| SFP2_RxRATE_SEL | IO_10N_10 | AH12 |

添加图片注释,不超过 140 字(可选)

4.12.SATA接口

开发板上设计了 1 路 SATA 接口,如下表列出了管脚对应关系,详细电路可以参 考开发板原理图。

| SATA 接口 | 管脚名称 | 管脚位置 |

|---|---|---|

| SATA1_TX_P | MGT_TX_P0_110 | AD2 |

| SATA1_TX_N | MGT_TX_N0_110 | AD1 |

| SATA1_RX_P | MGT_RX_P0_110 | AD6 |

| SATA1_RX_N | MGT_RX_N0_110 | AD5 |

添加图片注释,不超过 140 字(可选)

4.13.LED

核心板设计了五路 LED,开发板设计了两路 LED,共计七路 LED。LED 高电平亮, 低电平灭。详细电路可参考开发板原理图。

| LED 位号 | 管脚名称 | 管脚位置 |

|---|---|---|

| LED1(核心板) | IO_13N_9 | AA19 |

| LED2(核心板) | IO_14P_9 | AB19 |

| LED3(核心板) | IO_14N_9 | AB20 |

| LED4(核心板) | IO_19P_9 | AD20 |

| LED5(核心板) | IO_19N_9 | AE20 |

| LED1(开发板) | IO_9P_10 | AD14 |

| LED2(开发板) | IO_9N_10 | AD13 |

添加图片注释,不超过 140 字(可选)

4.14.按键

开发板上设计了 2 路按键,按键上拉到 3.3V,按键后为低,即低电平有效。如 下表列出了按键的连接对应关系。

| 按键位号 | 管脚名称 | 管脚位置 |

|---|---|---|

| KEY1 | IO_21P_10 | AB12 |

| KEY2 | IO_21N_10 | AC12 |

添加图片注释,不超过 140 字(可选)

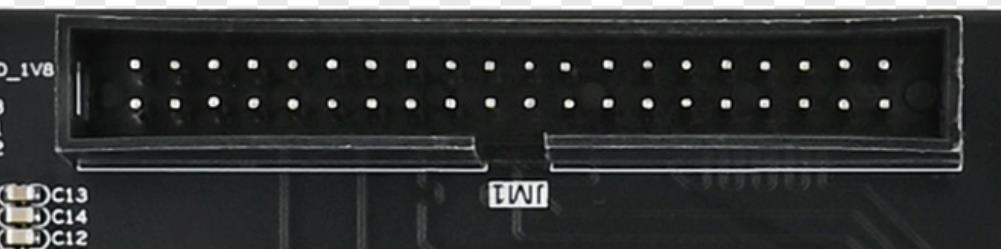

4.15.40P扩展接口

开发板板载了一个 40P 2.54mm 间距的简易牛角座,用于扩展信号的连接,接口 电平默认 3.3V。

如下表标出了信号所在的芯片位置,详细连接关系参考原理图部分。

| JM1 信号顺序 | 管脚名称 | 管脚位置 | JM1 信号顺序 | 管脚名称 | 管脚位置 |

|---|---|---|---|---|---|

| 5 | IO_L8P_10 | AH14 | 6 | IO_L12P_MRCC_1 | AF14 |

| 7 | IO_L8N_10 | AH13 | 8 | IO_L12N_MRCC_1 | AG14 |

| 9 | IO_L5P_10 | AJ15 | 10 | IO_L22P_10 | AB15 |

| 11 | IO_L5N_10 | AK15 | 12 | IO_L22N_10 | AB14 |

| 13 | IO_L3P_10 | AJ14 | 14 | IO_L19P_10 | AC14 |

| 15 | IO_L3N_10 | AJ13 | 16 | IO_L19N_10 | AC13 |

| 17 | IO_L18P_10 | AD16 | 18 | IO_L6P_10 | AH17 |

| 19 | IO_L18N_10 | AD15 | 20 | IO_L6N_10 | AH16 |

| 21 | IO_L14P_SRCC_10 | AF15 | 22 | IO_L16P_10 | AE16 |

| 23 | IO_L14N_SRCC_10 | AG15 | 24 | IO_L16N_10 | AE15 |

| 25 | IO_L17P_10 | AE18 | 26 | IO_L23P_10 | AC17 |

| 27 | IO_L17N_10 | AE17 | 28 | IO_L23N_10 | AC16 |

| 29 | IO_L13P_MRCC_10 | AG17 | 30 | IO_L15P_10 | AF18 |

| 31 | IO_L13N_MRCC_10 | AG16 | 32 | IO_L15N_10 | AF17 |

| 37 | IO_L4P_10 | AJ16 | 38 | IO_L2P_10 | AH18 |

| 39 | IO_L4N_10 | AK16 | 40 | IO_L2N_10 | AJ18 |

添加图片注释,不超过 140 字(可选)

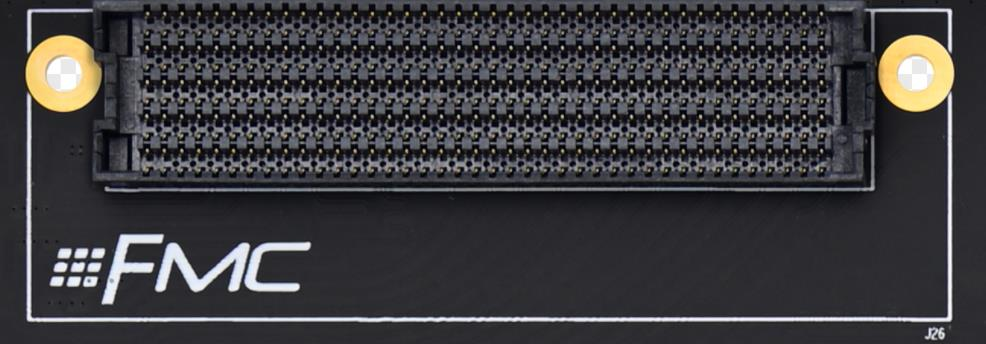

4.16.FMC扩展接口

开发板上设计了一路 FMC 连接器,接口类型为 HPC,如下表列出了信号对应关 系。详细连接关系参考原理图部分。

| FMC-HPC 管脚 | 管脚名称 | 管脚位置 |

|---|---|---|

| LA00_P_CC | IO_L14P_SRCC_13 | R27 |

| LA00_N_CC | IO_ L14N_SRCC | T27 |

| LA01_P_CC | IO_L13P_MRCC_13 | R25 |

| LA01_N_CC | IO_ L13N_MRCC | R26 |

| LA02_P | IO_L19P_13 | P21 |

| LA02_N | IO_L19N_13 | R21 |

| LA03_P | IO_L3P_13 | N28 |

| LA03_N | IO_L3N_13 | P28 |

| LA04_P | IO_L17P_13 | T24 |

| LA04_N | IO_L17N_13 | T25 |

| LA05_P | IO_L22P_13 | U22 |

| LA05_N | IO_L22N_13 | V22 |

| LA06_P | IO_L2P_13 | T30 |

| LA06_N | IO_L2N_13 | U30 |

| LA07_P | IO_L4P_13 | N29 |

| LA07_N | IO_L4N_13 | P29 |

| LA08_P | IO_L8P_13 | W29 |

| LA08_N | IO_L8N_13 | W30 |

| LA09_P | IO_L7P_13 | V28 |

| LA09_N | IO_L7N_13 | V29 |

| LA10_P | IO_L23P_13 | U24 |

| LA10_N | IO_L23N_13 | V24 |

| LA11_P | IO_L21P_13 | R22 |

| LA11_N | IO_L21N_13 | R23 |

| LA12_P | IO_L10P_13 | W25 |

| LA12_N | IO_L10N_13 | W26 |

| LA13_P | IO_L6P_13 | R28 |

| LA13_N | IO_L6N_13 | T28 |

| LA14_P | IO_L9P_13 | V27 |

| LA14_N | IO_L9N_13 | W28 |

| LA15_P | IO_L18P_13 | P23 |

| LA15_N | IO_L18N_13 | P24 |

| LA16_P | IO_L16P_13 | P25 |

| LA16_N | IO_L16N_13 | P26 |

| LA17_P_CC | IO_L12P_MRCC_13 | U26 |

| LA17_N_CC | IO_L12N_MRCC_13 | U27 |

| LA18_P_CC | IO_L11P_SRCC_13 | U25 |

| LA18_N_CC | IO_L11N_SRCC_13 | V26 |

| LA19_P | IO_L20P_13 | T22 |

| LA19_N | IO_L20N_13 | T23 |

| LA20_P | IO_L15P_13 | N26 |

| LA20_N | IO_L15N_13 | N27 |

| LA21_P | IO_L24P_13 | V23 |

|---|---|---|

| LA21_N | IO_L24N_13 | W24 |

| LA22_P | IO_L1P_13 | P30 |

| LA22_N | IO_L1N_13 | R30 |

| LA23_P | IO_L5P_13 | T29 |

| LA23_N | IO_L5N_13 | U29 |

| LA24_P | IO_L8P_12 | AD30 |

| LA24_N | IO_L8N_12 | AE30 |

| LA25_P | IO_L3P_12 | Y26 |

| LA25_N | IO_L3N_12 | Y27 |

| LA26_P | IO_L20P_12 | AJ30 |

| LA26_N | IO_L20N_12 | AK30 |

| LA27_P | IO_L16P_12 | AF30 |

| LA27_N | IO_L16N_12 | AG30 |

| LA28_P | IO_L9P_12 | AC29 |

| LA28_N | IO_L9N_12 | AD29 |

| LA29_P | IO_L1P_12 | Y30 |

| LA29_N | IO_L1N_12 | AA30 |

| LA30_P | IO_L24P_12 | AJ26 |

| LA30_N | IO_L24N_12 | AK26 |

| LA31_P | IO_L10P_12 | AD25 |

| LA31_N | IO_L10N_12 | AE26 |

| LA32_P | IO_L23P_12 | AH26 |

| LA32_N | IO_L23N_12 | AH27 |

| LA33_P | IO_L17P_12 | AG26 |

| LA33_N | IO_L17N_12 | AG27 |

| FMC_IIC_SCL | IO_L11P_10 | AE13 |

| FMC_IIC_SDA | IO_L11N_10 | AF13 |

| DP0_M2C_P | MGT_RX_P0_111 | AC4 |

| DP0_M2C_N | MGT_RX_N0_111 | AC3 |

| DP1_M2C_P | MGT_RX_P1_111 | AB6 |

| DP1_M2C_N | MGT_RX_N1_111 | AB5 |

| DP2_M2C_P | MGT_RX_P2_111 | Y6 |

| DP2_M2C_N | MGT_RX_N2_111 | Y5 |

| DP3_M2C_P | MGT_RX_P3_111 | AA4 |

| DP3_M2C_N | MGT_RX_N3_111 | AA3 |

| DP4_M2C_P | MGT_RX_P0_112 | V6 |

| DP4_M2C_N | MGT_RX_N0_112 | V5 |

| DP5_M2C_P | MGT_RX_P1_112 | U4 |

| DP5_M2C_N | MGT_RX_N1_112 | U3 |

| DP6_M2C_P | MGT_RX_P2_112 | T6 |

| DP6_M2C_N | MGT_RX_N2_112 | T5 |

| DP7_M2C_P | MGT_RX_P3_112 | P6 |

| DP7_M2C_N | MGT_RX_N3_112 | P5 |

| GBTCLK0_M2C_P | MGT_CLK0_P_111 | U8 |

| GBTCLK0_M2C_N | MGT_CLK0_N_111 | U7 |

| GBTCLK1_M2C_P | MGT_CLK0_P_112 | N8 |

| GBTCLK1_M2C_N | MGT_CLK0_N_112 | N7 |

| DP0_C2M_P | MGT_TX_P0_111 | AB2 |

|---|---|---|

| DP0_C2M_N | MGT_TX_N0_111 | AB1 |

| DP1_C2M_P | MGT_TX_P1_111 | Y2 |

| DP1_C2M_N | MGT_TX_N1_111 | Y1 |

| DP2_C2M_P | MGT_TX_P2_111 | W4 |

| DP2_C2M_N | MGT_TX_N2_111 | W3 |

| DP3_C2M_P | MGT_TX_P3_111 | V2 |

| DP3_C2M_N | MGT_TX_N3_111 | V1 |

| DP4_C2M_P | MGT_TX_P0_112 | T2 |

| DP4_C2M_N | MGT_TX_N0_112 | T1 |

| DP5_C2M_P | MGT_TX_P1_112 | R4 |

| DP5_C2M_N | MGT_TX_N1_112 | R3 |

| DP6_C2M_P | MGT_TX_P2_112 | P2 |

| DP6_C2M_N | MGT_TX_N2_112 | P1 |

| DP7_C2M_P | MGT_TX_P3_112 | N4 |

| DP7_C2M_N | MGT_TX_N3_112 | N3 |

| HA00_P_CC | IO_L13P_MRCC_11 | AG21 |

| HA00_N_CC | IO_L13N_MRCC_11 | AH21 |

| HA01_P_CC | IO_L12P_MRCC_11 | AE22 |

| HA01_N_CC | IO_L12N_MRCC_11 | AF22 |

| HA02_P | IO_L5P_11 | AH23 |

| HA02_N | IO_L5N_11 | AH24 |

| HA03_P | IO_L11P_11 | AD23 |

| HA03_N | IO_L11N_11 | AE23 |

| HA04_P | IO_L7P_11 | AC24 |

| HA04_N | IO_L7N_11 | AD24 |

| HA05_P | IO_L21P_11 | Y22 |

| HA05_N | IO_L21N_11 | Y23 |

| HA06_P | IO_L1P_11 | AJ25 |

| HA06_N | IO_L1N_11 | AK25 |

| HA07_P | IO_L8P_11 | AG24 |

| HA07_N | IO_L8N_11 | AG25 |

| HA08_P | IO_L19P_11 | AB21 |

| HA08_N | IO_L19N_11 | AB22 |

| HA09_P | IO_L22P_11 | AA24 |

| HA09_N | IO_L22N_11 | AB24 |

| HA10_P | IO_L16P_11 | AK17 |

| HA10_N | IO_L16N_11 | AK18 |

| HA11_P | IO_L2P_11 | AK22 |

| HA11_N | IO_L2N_11 | AK23 |

| HA12_P | IO_L24P_11 | AC22 |

| HA12_N | IO_L24N_11 | AC23 |

| HA13_P | IO_L9P_11 | AF23 |

| HA13_N | IO_L9N_11 | AF24 |

| HA14_P | IO_L6P_11 | AG22 |

| HA14_N | IO_L6N_11 | AH22 |

| HA15_P | IO_L23P_11 | AA22 |

| HA15_N | IO_L23N_11 | AA23 |

| HA16_P | IO_L18P_11 | AF19 |

|---|---|---|

| HA16_N | IO_L18N_11 | AG19 |

| HA17_P_CC | IO_L14P_SRCC_11 | AF20 |

| HA17_N_CC | IO_L14N_SRCC_11 | AG20 |

| HA18_P | IO_L4P_11 | AJ23 |

| HA18_N | IO_L4N_11 | AJ24 |

| HA19_P | IO_L17P_11 | AH19 |

| HA19_N | IO_L17N_11 | AJ19 |

| HA20_P | IO_L20P_11 | W21 |

| HA20_N | IO_L20N_11 | Y21 |

| HA21_P | IO_L3P_11 | AJ21 |

| HA21_N | IO_L3N_11 | AK21 |

| HA22_P | IO_L10P_11 | AD21 |

| HA22_N | IO_L10N_11 | AE21 |

| HA23_P | IO_L15P_11 | AJ20 |

| HA23_N | IO_L15N_11 | AK20 |

| HB00_P_CC | IO_L12P_MRCC_35 | F15 |

| HB00_N_CC | IO_L12N_MRCC_35 | F14 |

| HB01_P | IO_L18P_35 | B17 |

| HB01_N | IO_L18N_35 | A17 |

| HB02_P | IO_L15P_35 | F17 |

| HB02_N | IO_L15N_35 | E17 |

| HB03_P | IO_L16P_35 | D16 |

| HB03_N | IO_L16N_35 | C16 |

| HB04_P | IO_L17P_35 | C17 |

| HB04_N | IO_L17N_35 | B16 |

| HB05_P | IO_L1P_35 | L15 |

| HB05_N | IO_L1N_35 | L14 |

| HB06_P | IO_L14P_SRCC_35 | D15 |

| HB06_N | IO_L14N_SRCC_35 | D14 |

| HB07_P | IO_L4P_35 | J14 |

| HB07_N | IO_L4N_35 | H14 |

| HB08_P | IO_L20P_35 | C12 |

| HB08_N | IO_L20N_35 | B12 |

| HB09_P | IO_L8P_35 | G15 |

| HB09_N | IO_L8N_35 | G14 |

| HB10_P | IO_L24P_35 | A13 |

| HB10_N | IO_L24N_35 | A12 |

| HB11_P | IO_L19P_35 | C14 |

| HB11_N | IO_L19N_35 | C13 |

| HB12_P | IO_L21P_35 | B15 |

| HB12_N | IO_L21N_35 | A15 |

| HB13_P | IO_L2P_35 | J13 |

| HB13_N | IO_L2N_35 | H13 |

| HB14_P | IO_L7P_35 | G17 |

| HB14_N | IO_L7N_35 | G16 |

| HB15_P | IO_L22P_35 | C11 |

| HB15_N | IO_L22N_35 | B11 |

| HB16_P | IO_L3P_35 | L13 |

|---|---|---|

| HB16_N | IO_L3N_35 | K13 |

| HB17_P_CC | IO_L11P_SRCC_35 | E13 |

| HB17_N_CC | IO_L11N_SRCC_35 | D13 |

| HB18_P | IO_L9P_35 | G12 |

| HB18_N | IO_L9N_35 | F12 |

| HB19_P | IO_L10P_35 | F13 |

| HB19_N | IO_L10N_35 | E12 |

| HB20_P | IO_L5P_35 | K15 |

| HB20_N | IO_L5N_35 | J15 |

| HB21_P | IO_L23P_35 | B14 |

| HB21_N | IO_L23N_35 | A14 |

添加图片注释,不超过 140 字(可选)

4.17.PCIE2.0接口

开发板设计了PCIE2.0 接口,为 x4 接口,如下表列出了PCIE 接口对应关系。

| PCIE2.0 | 管脚名称 | 管脚位置 |

|---|---|---|

| PERST_N | IO_24N_10 | AB16 |

| REF_CLK_P | MGT_109_CLK_P0 | AD10 |

| REF_CLK_N | MGT_109_CLK_N0 | AD9 |

| PER0_P | MGT_109_TX_P3 | AK2 |

| PER0_N | MGT_109_TX_N3 | AK1 |

| PER1_P | MGT_109_TX_P2 | AJ4 |

| PER1_N | MGT_109_TX_N2 | AJ3 |

| PER2_P | MGT_109_TX_P1 | AK6 |

| PER2_N | MGT_109_TX_N1 | AK5 |

| PER3_P | MGT_109_TX_P0 | AK10 |

| PER3_N | MGT_109_TX_N0 | AK9 |

| PET0_P | MGT_109_RX_P3 | AE8 |

| PET0_N | MGT_109_RX_N3 | AE7 |

| PET1_P | MGT_109_RX_P2 | AG8 |

| PET1_N | MGT_109_RX_N2 | AG7 |

| PET2_P | MGT_109_RX_P1 | AJ8 |

| PET2_N | MGT_109_RX_N1 | AJ7 |

| PET3_P | MGT_109_RX_P0 | AH10 |

| PET3_N | MGT_109_RX_N0 | AH9 |

添加图片注释,不超过 140 字(可选)

4.18.JTAG接口

开发板设计了一个 JTAG 接口,购买开发板后,我们会提供配套的下载器,对应 连接线序就可以下载调试板卡。

添加图片注释,不超过 140 字(可选)

审核编辑 黄宇

-

[XILINX] 正点原子ZYNQ7035/7045/7100开发板发布、ZYNQ 7000系列、双核ARM、PCIe2.0、SFPX2!2024-09-02 10307

-

STM32-PZ6806L开发板原理图2018-11-28 4652

-

AVboardHD开发板用户手册2010-11-12 527

-

STM32-PZ6806L开发板电路原理图免费下载2019-05-16 3194

-

ZYNQ7000开发平台的AX7Z035开发板用户手册免费下载2019-06-24 3696

-

STM32F407PZ6808L开发板的电路原理图免费下载2020-03-05 2635

-

PZ-DSP28335-L开发板的电路原理图免费下载2020-03-12 4026

-

STM32 PZ6806L开发板的电路原理图免费下载2020-04-10 2718

-

AX7Z035 ZYNQ开发板的用户手册资料免费下载2020-10-22 3551

-

普中PZ6806开发板入门教程2023-06-09 1146

-

正点原子fpga开发板不同型号2024-11-13 6867

-

ZYNQ 7035/7045开发板原理图2024-12-05 1474

-

【PZ7020-StarLite 入门级开发板】——FPGA 开发的理想起点,入门与工业场景的双重优选2025-08-08 1597

-

FPGA开发板—璞致 Kintex-7 系列核心板PZ-K7325T/PZ-K7410T 使用说明 XILINX核心板简介2025-09-22 1201

-

fpga开发板 璞致 Kintex UltraScale Plus PZ-KU3P 与 PZ-KU5P核心板与开发板用户手册2025-09-26 1858

全部0条评论

快来发表一下你的评论吧 !