LMK04133 芯片文档摘要

描述

LMK04100系列精密时钟调节器无需高性能VCXO模块即可提供抖动清除、时钟倍增和分配。

当连接到恢复的系统基准时钟和VCXO时,该器件可生成5个LVCMOS、LVDS或LVPECL格式的低抖动时钟。

*附件:lmk04133.pdf

特性

- 级联 PLLatinum PLL 架构

- PLL1冗余基准输入信号丢失

检测自动和手动选择

基准时钟输入 - PLL2相位检测器速率高达100 MHz输入

倍频器集成VCO

- PLL1冗余基准输入信号丢失

- 输出

- LVPECL/2VPECL、LVDS 和

LVCMOS 格式 - 支持高达 1080 MHz 的时钟速率

- 五个专用通道分频器模块

- 支持的常见输出频率:

30.72 MHz、61.44 MHz、62.5 MHz、

74.25 MHz、75 MHz、77.76 MHz、100 MHz、

106.25 MHz、125 MHz、122.88 MHz、

150 MHz、155.52 MHz、156.25 MHz、159.375 MHz、

187.5 MHz、200 MHz、

212.5 MHz、245.76 MHz、250 MHz、311.04 MHz、

312.5 MHz、368.64 MHz、

491.52 MHz、622.08 MHz、625 MHz、983.04 MHz

- LVPECL/2VPECL、LVDS 和

- MICROWIRE (SPI) 编程接口

- 工业温度范围:–40 至 85 °C

- 3.15 V 至 3.45 V 工作电压

- 封装:48 引脚 WQFN(7.0 × 7.0 × 0.8 mm)

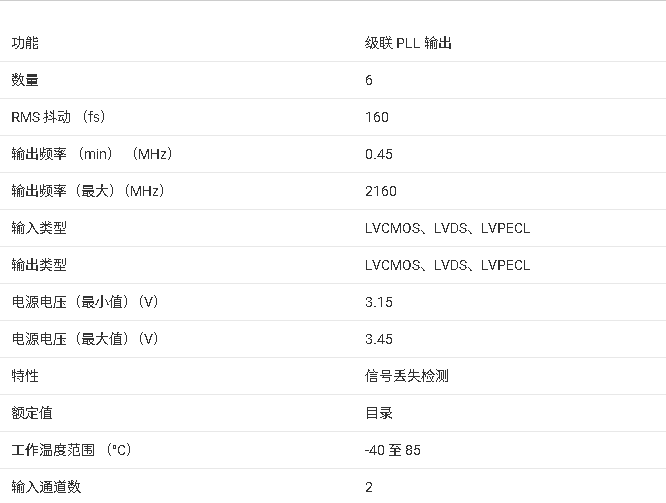

参数

方框图

1. 产品系列与型号

- 所属系列:LMK04100 家族时钟抖动清除器

- 包含型号:LMK04100/01/02/10/11/31/33

- 文档版本:SNAS516B(2011年4月发布,2012年11月修订)

2. 核心特性

- 双级联PLL架构

- PLL1:支持冗余参考输入、信号丢失检测、自动/手动参考时钟选择

- PLL2:相位检测速率达100 MHz,集成VCO,支持输入频率倍频

- 多样化输出

- 支持格式:LVPECL/2VPECL、LVDS、LVCMOS

- 最高输出频率:1080 MHz

- 专用分频器通道:5个

- 常见输出频率:覆盖30.72 MHz至983.04 MHz(如61.44 MHz、125 MHz、622.08 MHz等)

- 控制接口:MICROWIRE(SPI)编程接口

- 工作条件

- 电压范围:3.15 V ~ 3.45 V

- 温度范围:-40°C ~ 85°C(工业级)

- 封装:48引脚WQFN(7.0 x 7.0 x 0.8 mm)

3. 典型应用场景

- 2G/3G/4G多载波/多模式/多频段基站

- 蜂窝中继器

- 高速ADC时钟

- SONET/SDH OC-48/192/768设备

4. 关键优势

- 高集成度:双PLL+VCO设计简化系统时钟架构

- 灵活性:支持多种输出格式与频率配置

- 工业级可靠性:宽温范围与冗余设计

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

深入剖析 LMK04100 系列时钟抖动清理器:性能、应用与设计要点2026-02-09 185

-

LMK00725 芯片技术文档总结2025-09-15 841

-

LMK04832-SEP 芯片技术文档摘要2025-09-11 854

-

请问LMK04133是否有内部EEPROM可供程序烧写?2024-11-11 328

-

基于JESD204B的LMK04821芯片项目开发2023-01-05 2452

-

基于布谷鸟搜索算法与多目标函数的多文档摘要方法2021-03-30 939

-

LMK04832-SP时钟抖动清除器2021-03-24 1492

-

求助 LMK040010B时钟芯片问题2014-10-17 3005

-

基于词频统计的多文档自动摘要生成方案2009-12-18 814

全部0条评论

快来发表一下你的评论吧 !