一文详解SOI异质结衬底

描述

文章来源:学习那些事

原文作者:前路漫漫

本文介绍了与SOI相关的技术。

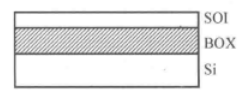

SOI(silicon-on-insulator,绝缘衬底上的硅)技术的核心设计,是在顶层硅与硅衬底之间引入一层氧化层,这层氧化层可将衬底硅与表面的硅器件层有效分隔(见图 1)。借助在绝缘体上形成半导体薄膜的结构,SOI 材料具备体硅无法比拟的优势:能实现集成电路中元器件的介质隔离,彻底根除体硅 CMOS 电路中的闩锁(Latch-up)效应;基于该材料制作的集成电路还拥有寄生电容低、集成密度高、运行速度快、制备工艺简化、短沟道效应弱等特点,尤其适配低压低功耗电路场景,因此 SOI 有望成为深亚微米级低压低功耗集成电路的主流技术方向。

SOI 的核心材料主要包括三类:通过注氧隔离制备的 SIMOX(separation by implanted oxygen,注氧隔离)材料、经硅片键合与反面腐蚀制成的 BESOI(bonding-etchback SOI,键合 - 回蚀 SOI)材料,以及融合键合与离子注入技术的 Smart Cut SOI 材料。在这三类材料中,SIMOX 适用于制备薄膜全耗尽超大规模集成电路,BESOI 材料更适配部分耗尽集成电路的制作;而后续发展的 Smart Cut(智能剥离)技术,整合了 SIMOX 与 BESOI 的优势,属于极具发展潜力的 SOI 材料,未来有望成为 SOI 材料的主流类型。

注氧隔离技术(SIMOX)

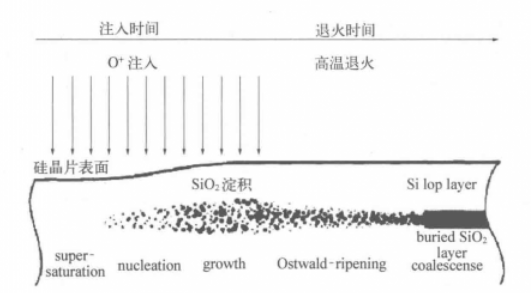

作为 SOI 圆片制备领域发展最早的技术之一,SIMOX 曾被认为有望实现大规模应用。该技术的核心步骤包含离子注入与高温退火 —— 具体为高能量、高剂量的氧离子注入及后续退火处理,其中注入能量通常为几十 keV,注入剂量约为 1×10¹⁸ cm⁻²。在注入过程中,氧离子进入硅圆片内部并与硅发生反应,形成二氧化硅沉淀物;经过 1150℃下 2 分钟的退火处理后,可在硅圆片表面下方 380nm 处形成厚度为 210nm 的 SiO₂层,其工艺流程如图 2 所示。

尽管 SIMOX 技术因发展历史悠久而相对成熟,但长时间大剂量的离子注入,以及后续需进行的超高温长时间退火工艺,导致 SIMOX 材料在质量稳定性与成本控制方面难以实现突破,这也是目前该技术尚未被产业界完全接纳并大规模应用的根本原因。SIMOX 技术面临的核心难点包括:颗粒污染控制、埋层(尤其低剂量 / 超低剂量埋层)的结构完整性、金属杂质沾污、界面台阶控制、界面与表面粗糙度,以及表层硅中的缺陷问题,其中材料质量的稳定性更是难以保证。

薄膜全耗尽(FDSOI)

通常依据绝缘体上硅膜的厚度,可将 SOI 结构划分为薄膜全耗尽(FD,fully depleted)与厚膜部分耗尽(PD,partially depleted)两类。由于 SOI 具备介质隔离特性,制作于厚膜 SOI 结构上的器件,其正面与背面界面的耗尽层互不影响,两层之间存在一个中性体区。该中性体区的存在会使硅体处于电学浮空状态,进而产生两种明显的寄生效应:一是 “翘曲效应”(即 Kink 效应),二是器件源极与漏极之间形成的基极开路 NPN 寄生晶体管效应。若将该中性区通过体接触接地,厚膜 SOI 器件的工作特性便与体硅器件几乎一致。

而基于薄膜 SOI 结构的器件,因硅膜可实现完全耗尽,能彻底消除 “翘曲效应”;同时这类器件还具备低电场、高跨导、优异的短沟道特性,以及接近理想值的亚阈值斜率等优势,因此薄膜全耗尽 FDSOI 被认为是极具前景的 SOI 结构类型。

键合技术(BESOI)

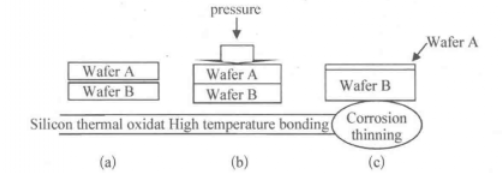

通过键合(bond)技术,可使硅(Si)与二氧化硅(SiO₂)、或二氧化硅与二氧化硅之间的两个圆片紧密结合,并在两圆片中间形成 SiO₂层作为绝缘层。BESOI 圆片的制备需在键合完成后,将其中一个圆片的一侧削薄至目标厚度,整个过程分为三步(见图 3)。

键合技术面临的核心问题是表层硅厚度的均匀性控制,这也是限制该技术广泛推广的根本原因。除此之外,键合边缘的控制、界面缺陷、圆片翘曲度与弯曲度的控制、滑移线抑制、颗粒污染防控、崩边问题,以及界面沾污等,均是制约 BESOI 产业化制备的关键技术难题。而成品率与成本控制,则是决定键合类 SOI 产品能否被量产客户接受的核心商业因素。另外,Wafer A(待减薄圆片)的减薄效率,也是影响 BESOI 技术实用化进程的重要因素,具体可参考图 3(c)。

智能剥离法(Smart-cut)

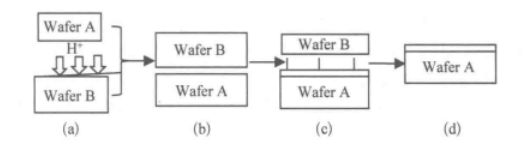

Smart-cut(智能剥离)技术是融合 SIMOX 技术与 BESOI 技术优势的创新工艺,既继承了两者的核心特点,又克服了各自的不足,属于当前较为理想的 SOI 制备方案。其技术特征体现在改进型 Smart-cut 制备 SOI 基底的流程中:通过该工艺制备 SOI 基底后,结合电子束光刻与深反应离子刻蚀技术,可制作具有二维周期结构的光子晶体,同时引入线缺陷构建光子晶体波导。该技术主要包含四个关键步骤,具体如图 4 所示。

H⁺离子注入:在室温环境下,以特定能量向硅片 A 注入定量 H⁺离子,使硅片表层下方形成一层富含 H⁺离子的硅层;与此同时,对支撑硅片进行热氧化处理,在其表面生成一层氧化层,具体结构如图 4(a)所示。

预键合:先对硅片 A 与另一硅片 B 进行严格的清洗与活化处理,随后在室温下将两片硅片的抛光面贴合,实现初步键合,如图 4(b)所示。需注意,硅片A 与 B 中至少有一片的键合表面需通过热氧化法生长SiO₂层,该层将作为 SOI 结构中的隐埋绝缘层。

热处理:整体分为两步进行:第一步,将键合后的硅片置于高温环境中,注入的高浓度 H⁺离子层会发生成核并形成气泡,气泡急剧膨胀促使硅片在富含 H⁺离子的层位发生剥离,剥离后的硅层留存备用,剩余硅层则作为 SOI 结构的顶部硅层,如图 4(c)所示;第二步,通过高温热处理进一步提升键合界面的结合强度,并消除 SOI 层中因离子注入产生的结构损伤。

化学机械抛光:对剥离后的硅片表面进行抛光处理,降低表面粗糙度,如图 4(d)所示。断裂面经轻度抛光后,即可达到体硅的表面光洁度,目前已能制备出顶层硅厚度为 200±4nm 的 4 英寸SOI 材料。

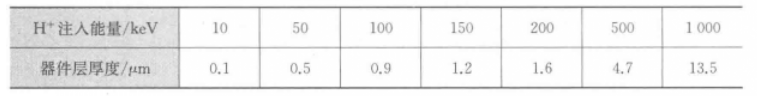

SOI 片顶层硅膜的厚度与 H⁺注入能量直接相关:H⁺注入能量越高,H⁺注入峰的深度越大,顶层硅膜的厚度也随之增加。表 9-1 详细列出了器件层厚度与 H⁺注入能量的对应关系。

相较于 SIMOX 与 BESOI 两种 SOI 制备技术,Smart-cut 技术的优势十分显著:其一,H⁺注入剂量仅为 1×10¹⁶ cm⁻²,比 SIMOX 低两个数量级,可采用普通离子注入机完成,降低设备成本;其二,埋氧层通过热氧化工艺形成,不仅 Si/SiO₂界面质量优异,氧化层本身性能也更稳定;其三,剥离后的硅片可重新作为键合衬底循环使用,大幅降低原材料消耗,同时硅层减薄效率显著提升。因此,Smart-cut 技术已成为 SOI 材料制备领域中竞争力最强、发展前景最广的技术之一。自 1995 年开发以来,该技术发展迅速,法国 SOITEC 公司已能提供基于 Smart-cut 技术制备的商用 SOI 硅片,并拥有相关核心专利。

GaAs 和 Ge 有源衬底层

当互补型金属氧化物半导体(CMOS)场效应管的栅极长度接近 10nm 后,传统 CMOS 技术的缩放效应面临根本性的物理限制。下表对比了几类相关半导体材料的电学性质。

由于 GaAs 系列 Ⅲ-Ⅴ 族化合物半导体的电子迁移率远高于硅材料,因此有望替代硅用于制作 nMOSFET。不过,Ⅲ-Ⅴ 族 MOSFET 的研发面临两大核心挑战:一是如何在硅基平台上集成高品质的 GaAs 系列 Ⅲ-Ⅴ 族沟道层材料;二是如何实现稳定的 Ⅲ-Ⅴ 族半导体 / 高 k 栅绝缘层界面,并规避常见的费米能级钉扎效应(Fermi Pinning Effect,该效应会导致金属栅的费米能级被钉扎在半导体禁带中央附近,无法满足双金属栅 MOS 器件对阈值电压的要求)。

近年来,薄膜淀积技术取得显著突破。H.J.Oh 团队报道了在氧化硅上生长砷化镓绝缘体的成果,成功实现硅基平台上的 GaAs 异质外延层制备;结合金属有机物化学气相淀积(MOCVD)技术,进一步制作出 InGaAs/HfO₂叠层结构,有效规避了界面费米能级钉扎问题,基于该结构的 NMOS 场效应管速度比传统硅基器件快近 3 倍。

对于 pMOSFET 而言,锗硅(GeSi)异质结系列半导体的空穴迁移率远高于硅材料,因此可作为硅的替代材料制作 pMOSFET。由于锗材料与硅材料的晶格匹配度较高,在硅基底上制备锗硅系列 pMOSFET 的难度相对较低。MT.Currie 团队与张雪锋团队通过在高 k 介质与 Ge 表面引入 HfO₂/HfON 叠层栅介质,制作出的 pMOS 器件有效迁移率可达硅基器件的 2 倍左右。

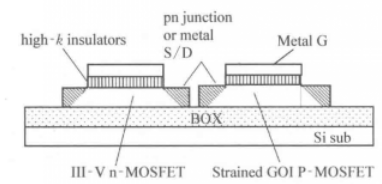

图 5 展示了以 GaAs 为 nMOS、Ge 为 pMOS 的下一代硅基 CMOS 结构,该结构仍以硅基 SOI 为衬底材料,有望成为下一代集成电路(IC)中 CMOS 的首选电路单元。

-

常见几种SOI衬底及隔离的介绍2012-01-12 15965

-

异质结双极晶体管2012-08-20 2487

-

异质结2009-11-07 5795

-

异质结双极晶体管,异质结双极晶体管是什么意思2010-03-05 5768

-

异质结,异质结是什么意思2010-03-06 17500

-

什么是双异质结(DH)激光器2010-04-02 7684

-

砷化硼异质结—潜在的光电薄膜和衬底材料2020-05-07 7914

-

自清洁半导体异质结衬底说明2022-03-25 764

-

二维材料电致横向PN结及纵向异质结快速转移制备2023-02-15 2832

-

石墨烯/硅异质结光电探测器的制备工艺与其伏安特性的关系2023-05-26 2759

-

异质结电池的ITO薄膜沉积2023-09-21 1890

-

什么是SOI衬底?SOI衬底的优势是什么?2023-10-10 7368

-

异质外延对衬底的要求是什么?2024-04-17 2090

-

异质结类型的介绍2024-11-26 18467

-

一文详解BSIM-SOI模型2025-09-22 2585

全部0条评论

快来发表一下你的评论吧 !