LMH1983 3G/HD/SD视频时钟发生器技术文档总结

描述

该LMH1983是一款高度集成的可编程音频/视频 (A/V) 时钟发生器 适用于广播和专业应用。它可以取代使用的多个 PLL 和 VCXO 在支持 SMPTE 串行数字视频 (SDI) 和数字音频 AES3/EBU 标准的应用中。 它为任何 SDI 发射器提供低抖动参考时钟,以满足严格的输出抖动 规格,没有额外的时钟清洁电路。

该LMH1983具有自动输入格式检测功能,可对多个 A/V 进行简单编程 输出格式、同步锁相或数字自由运行模式,以及各种可编程性 自动功能。公认的输入格式包括主要视频标准的 HVF 同步、 27 MHz、10 MHz 和 32/44.1/48/96 kHz 音频字时钟。

*附件:lmh1983.pdf

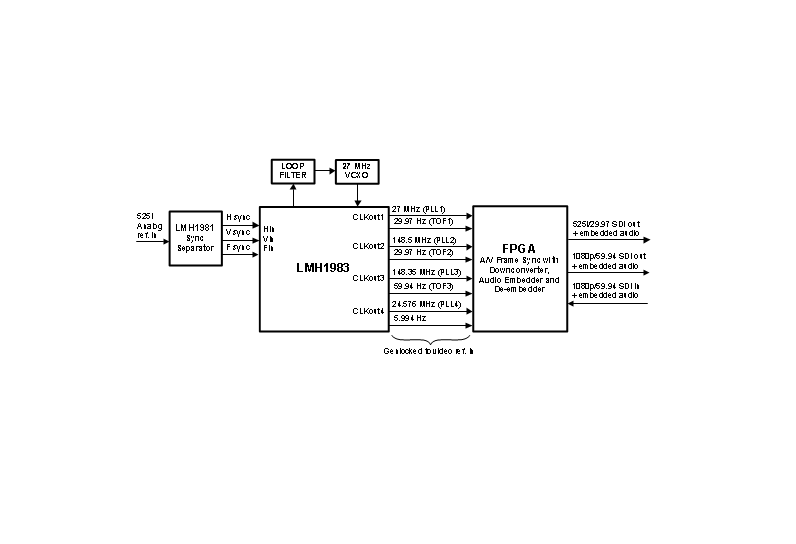

双级PLL架构集成了四个PLL和三个片上VCO。第一个 级 (PLL1) 使用具有窄环路带宽的外部低噪声 27 MHz VCXO 来提供干净的 下一阶段的参考时钟。第二级(PLL2、3、4)由三个并联VCO组成 用于同时生成主要数字 A/V 时钟基频速率的 PLL,包括 148.5 MHz、148.5/1.001 MHz 和 98.304 MHz(4 × 24.576 MHz)。每个PLL可以生成一个时钟和一个时序 脉冲以指示帧顶部 (TOF)。

当锁定到基准电压源时,内部10位ADC将跟踪环路滤波器控制 电压。当发生基准丢失 (LOR) 时,可以对LMH1983进行编程以保持控制 电压,以将输出精度保持在前一个基准电压源的 ±0.5 ppm(典型值)以内。这 LMH1983可以配置为以无毛刺的方式重新同步到先前的参考 操作。

特性

- 四个PLL,用于同时生成A/V时钟

- PLL1:27 或 13.5 MHz

- PLL2:148.5 或 74.25 MHz

- PLL3:148.5/1.001 或 74.25/1.001 MHz

- PLL4:98.304 兆赫 / 2 ^X^ (X = 0 到 15)

- 3 x 2 视频时钟交叉点

- 灵活的 PLL 带宽可优化抖动性能

和锁定时间 - 软重新同步到新参考

- 数字滞留或失去参考时自由运行

- 丢失参考和丢失 PLL 锁定的状态标志

- 3.3 V单电源工作

- 我^2^C 接口,带地址选择引脚(3 种状态)

参数

方框图

1. 产品概述

LMH1983是德州仪器(TI)推出的高集成度可编程音视频时钟发生器,专为广播和专业应用设计。该器件通过四路PLL同步生成多种音视频时钟,可替代传统多PLL和VCXO方案,适用于SDI串行数字视频和AES3/EBU数字音频标准。

2. 核心特性

- 四路独立PLL:

- PLL1:27/13.5 MHz(需外接VCXO)

- PLL2:148.5/74.25 MHz

- PLL3:148.5/1.001或74.25/1.001 MHz

- PLL4:98.304 MHz(支持2^X分频,X=0-15)

- 低抖动性能:满足SMPTE SDI输出抖动规范,无需额外时钟清洁电路。

- 灵活工作模式:支持Genlock(参考锁定)、Free-run(自由运行)和Holdover(保持模式)。

- 自动格式检测:支持NTSC、PAL、720p、1080i/p等31种标准视频格式及用户自定义格式。

3. 关键功能模块

- 输入处理:支持H/V/F同步信号、27 MHz时钟、10 MHz GPS时钟及音频字时钟(32/44.1/48/96 kHz)。

- 输出配置:

- 3×2视频时钟交叉矩阵,可灵活分配PLL输出至CLKout1-3。

- 每路时钟配套TOF(帧顶脉冲)输出,支持帧同步编程。

- 控制接口:I2C接口(地址可配置为0x65-0x67)。

4. 典型应用场景

- 广播设备:SDI串行器/解串器、帧同步器、格式转换器。

- 专业视频:摄像机、投影仪、A/D-D/A转换卡。

- 测试测量:音视频测试设备时钟源。

5. 技术参数

- 电源:3.3V单电源供电,典型功耗212mA(全功能模式)。

- 抖动性能:

- 27 MHz输出:随机抖动2.7 ps(RMS),确定性抖动250 fs。

- 148.5 MHz输出:随机抖动3.0 ps,确定性抖动8 ps。

- 封装:40引脚WQFN(6mm×6mm),带裸露焊盘散热。

6. 设计支持

- 外部元件:需外接27 MHz VCXO和环路滤波器(推荐CTS 357LB3C027M0000)。

- 布局建议:差分时钟走线需等长,避免干扰;电源层需低电感设计。

7. 文档结构

包含特性说明、引脚配置、电气特性、寄存器映射(共47个寄存器)、典型应用电路及布局示例,配套评估板(SD1983EVK)支持快速原型开发。

附件说明

当前文档为完整数据手册(SNLS309I版本),涵盖硬件设计、软件配置及性能测试数据,适用于工程师进行系统集成和调试。

-

探究LMH1983:3G/HD/SD视频时钟发生器的设计与应用2026-02-09 549

-

LMH0302 3 - Gbps HD/SD SDI 电缆驱动器:设计与应用全解析2025-12-27 1089

-

探索LMH0318:3Gbps HD/SD SDI时钟恢复器的卓越性能与应用实践2025-12-19 1474

-

探索时钟发生器的竞争优势2025-10-23 933

-

LMH1982多速率视频时钟发生器技术文档总结2025-09-18 884

-

LMK3H2104 4-Output PCIe时钟发生器技术文档总结2025-09-10 1119

-

LMH1982多速率视频时钟发生器数据表2024-08-22 406

-

LMH1983高度集成的可编程音频/视频(AV)时钟发生器数据表2024-08-21 436

-

时钟发生器AD9516-0技术手册2022-01-25 1056

-

如何选择合适的时钟发生器2020-11-22 4002

-

LMH1983 具有音频时钟的 3G/HD/SD 视频时钟发生器2018-10-16 772

-

介绍MEMS时钟发生器的特点及应用介绍2018-07-08 5085

-

Microchip基于MEMS的时钟发生器2018-06-07 6154

-

NS LMH1982 多速率视频时钟方案2010-02-06 555

全部0条评论

快来发表一下你的评论吧 !