关于基于DDS技术的杂散抑制和正弦信号源的实现

描述

0 引言

在设备检测和电子测量技术中,常常需要一个高精度、频率可变的信号源,信号源的稳定往往关系到这些系统工作的性能。如在磨粒检测传感器中,需要对激励线圈施加以高频正弦信号,据理论分析和仿真验证,在一定的频率下,检测灵敏度随激励频率的增大而增大[1]。相比较其他信号合成技术,直接数字频率合成(Direct Digital frequency Synthesis,DDS)具有频率转换时间短,频率分辨率高,可编程和全数字化[2]。

文献[3]基于simulink软件搭建了DDS仿真模型,对DDS理想数学模型和有相位截断误差模型进行了分析,但文中并没有提出方法减少杂散分量。文献[4]通过AVR单片机和芯片AD9835设计出了一种高精度高频率的正弦波交流电源,但其变频范围太窄,仅为100 kHz~300 kHz,不能够满足对兆赫兹频率源的需求。

为弥补上述不足,论文首先通过simulink软件搭建DDS仿真系统模型,通过压缩ROM查询表的数据量用以增加其位数,减少DDS杂散信号的输出。然后利用DDS芯片AD9851和微处理AT89S52设计出一种正弦信号源,实现了1 Hz~50 MHz的正弦波输出。

1 DDS工作原理

DDS是一种将数字处理方法引入频率合成的新技术,把一系列数字量信号通过数/模转换成模拟量信号。基本原理框图如图1(a)所示,主要由相位累加器、ROM查询表、D/A转换器和低通滤波器构成。

在参考时钟Fclk的作用下,N位累加器每接收到一次时钟脉冲对频率控制字M进行一次累加,把累加后的结果送至ROM查询表中,查询表事先存入了2N个相位-幅度转换数据。不同的频率控制字M会引起累加器相位增量的不同,这样通过查询表就得到不同频率的数字正弦序列,经过D/A转换器后,输出阶梯型正弦信号,最后经过滤波器模块滤除高频分量并进行平滑后,得到模拟的正弦波信号[5]。其中各个模块的输出波形如图1(b)所示。

据上述工作原理和DDS系统的几项参数,可以得到输出信号的频率和频率分辨率分别为:

2 DDS仿真模型的建立

DDS仿真模型的搭建是在软件simulink中完成的,它可以提供一个动态系统建模、仿真和综合分析的集成环境[6]。据上述对DDS基本工作原理的分析,利用simulink中已有或自定义的功能模块来搭建DDS的仿真模型。

2.1 DDS仿真模型图

DDS仿真模型框架如图2所示,其中参考时钟由Pulse Generator提供,频率控制字由Constant模块给出。N位累加器由Triggered Subsystem模块和内部相关程序构成。ROM查询表模块由Look-up table模块构成,里面存储了正弦相位值到幅度值之间的转换表。由于查询表模块已经集成了D/A转换器,因此该模块输出的信号就是模拟量。低通滤波器由Analog filter design构成,对上一级的输出信号进行平滑处理和滤波。余下模块是一些信号显示和信号处理模块。

图3是DDS仿真模型各个节点的输出波形,它与原理框图各个节点的输出波形一致。此模型中,时钟参考频率为400 kHz,累加器的位数为16位,频率控制字给定的是3 277,则根据式(1)计算理论输出的正弦信号频率为20 kHz。图3中实际输出频率为1/(0.5×10-4 s)=20 kHz,从而验证了该模型的正确性,修改相应的频率控制字实现指定频率信号的输出。

2.2 基于对称性的压缩方法

由DDS原理可知,ROM查询表存储的数据越详细,输出的数字正弦序列越精确,从而得到的正弦信号杂散越小[7],但这会使存储表的数据量过多。既要减少查询表对DDS资源的占用同时尽量避免影响正弦序列输出的精度,对查询表存储数据量进行压缩的方法就显得尤为重要。而每当ROM查询表的数据被压缩一倍,就相当于减少了一位截断位数,杂散抑制便可得到6 dB的提高[8]。

利用正弦波的对称性将一个周期(0,2π)的波形由1/4周期(0,π/2)的波形变换得到,将ROM查询表的数据量可以缩减至1/4。图4(a)中的1/4 压缩模块就是根据正弦波的对称性进行数据压缩。

可以从图4(b)中看出经过压缩模块后,其输出波形的精度并没有受到影响。原先ROM查询表存储了216个数据,经过该模块后,只需存储214个数据就可以达到相同的结果。因此原先的16位累加器便可以等效存储218个数据。

2.3 基于Sunderland算法的压缩方法

D.A.Sunderland提出的粗细分割算法原理是基于三角函数的近似算法,把DDS中相位累加器的输出分为三部分(X,Y和Z),利用三角函数展开可得:

用查询表分别存储sin(X+Y)和cosXsinZ的值,然后将两个查询表的结果相加,得到的值就是近似相位累加器值所对应的正弦信号幅度。

图5中的Sunderland压缩模块为该数据压缩方法的具体实现框图,原先ROM查询表存储数据量为216,压缩后数据量为26×24+26×26=5 120,其压缩比为1:12.8。通过仿真分析对比,存储数据量的减少,并没有影响到输出正弦信号的精度。

2.4 两种压缩方法相结合

把上述两种压缩方法结合起来。首先由正弦信号对称性,将16位的ROM查询表的位数压缩至14位,然后由Sunderland算法采用(5,4,5)的分割形式,查询表数据量为25×24+25×25=1 536,压缩比为1:42.67。图6为1/4压缩模块和Sunderland压缩模块相结合的DDS仿真模型图。

经过压缩后,相同的数据量降低了所占用的查询表位数,使得相同位的查询表可以存储更多的数据,而数据量越详细,杂散信号越可以得到有效抑制。

3 正弦信号源的实现

系统主要由微处理器AT89S52和DDS集成芯片AD9851构成,其中AT89S52输出相应的端口初始化和控制字,AD9851根据工作时序图接收相应的控制字,输出正弦信号。

3.1 AD9851芯片介绍

AD9851芯片采用先进的DDS技术,可以实现全数字编程的频率合成,可接收32位的频率控制字输入,其内部含有一个6倍频的REFCLK倍频器[9]。

3.2 系统硬件设计模块

产生指定频率的正弦信号,需要通过微处理器向DDS芯片输入相应的频率控制字,并需要对其端口进行初始化。其硬件设计框图如图7所示,其中AT89S52的P2.5控制频率更新控制信号(FQ-UD),P2.6控制写装入信号(W-CLK),P2.7控制复位信号(RESET)。将微处理的引脚P0.0~P0.7作为频率、相位控制字和工作方式控制字的输入口,连接到AD9851的D0~D7。在AD9851外接30 MHz有源晶振产生180 MHz内部基准时钟。

DDS信号的合成是数字量化产生的阶梯型正弦波,杂散寄生分量大部分集中在高频段,因此合成的信号在输出之前需要通过低通滤波器。考虑到设计的频率源有一定的带载能力,采用巴氏有源低通滤波器,滤波之后进行功率放大。

3.3 系统软件设计模块

AD9851接收数据的方式有并行和串行两种方式。并行比串行传输的速度要快,设计中选用并行工作方式,其工作时序图如图8所示。

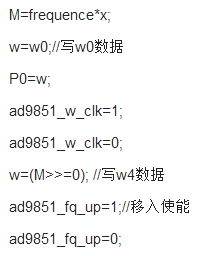

由AD9851的并行工作时序图,在微处理器中相关程序的实现如下:

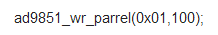

调用程序如下,只需在程序中写入需要输出的频率,程序会自动计算出相应的控制字,按照并行时序图依次将频率控制字M送入到AD9851的D0~D7。

其中0x01含有8位数据,5位相位控制字、6倍频使能控制、电源休眠和逻辑0。设计中需用到六倍频模式,其他位选择默认即可,故将此八位设置为0x01,送入到w0中。程序中100为输出100 Hz的正弦信号,进行相关计算后得到一个32位的频率控制字,依次送入到w1、w2、w3和w4中。

3.4 系统测试结果

利用altium designer软件设计相应的电路板如图9所示,主要由微处理器模块、DDS模块、滤波模块和功率放大模块构成。

图10为输出频率为2 MHz的信号波形,其波形比较精确和稳定,频谱图也比较干净,在指定频率处频谱增益最大,在其他频率处有不同程度的衰减。

经过对PCB板的测试,可以输出1 Hz~50 MHz的正弦信号,当频率大于50 MHz时,波形已有明显的失真,频谱的各次谐波逐渐增多。

4 结论

通过在simulink中搭建DDS仿真模型,对DDS的工作原理进行验证,仿真与理论分析的结果相一致,修改频率控制字,可以得到指定频率的正弦信号。为了降低DDS的杂散,分别利用正弦波的对称性和Sunderland结合算法对ROM查询表进行压缩,最终压缩比为1:46.67,使得同样的查询表可以存储更多的数据,间接提高了查询表的位数,有效地抑制了DDS杂散信号的输出。

基于微处理器AT89S52和DDS芯片AD9851设计出了一种实现高频正弦信号的方法。在相关软件中绘制原理图和PCB图,制成实际PCB板,通过测试实现了1 Hz~50 MHz的正弦信号输出,其频率稳定性较高,并且该系统的电路结构简单,控制方便。可用做于模拟传感器线圈的激励部分,同时也能够在不同的领域用作高频信号源。

-

如何抑制DDS输出信号中杂散问题?2021-05-26 3178

-

DDS工作原理是?用DDS芯片AD9858宽带雷达信号源要设计最佳?2021-04-06 2815

-

采用AD9858实现雷达信号源的应用设计2020-11-24 1583

-

基于AD9958的双通道正弦信号源的设计2017-11-14 2289

-

基于DDS的信号源设计论文资料2017-07-19 1241

-

应用AD9851实现正弦波信号源2016-12-17 1308

-

基于DDS技术的多路同步信号源的设计2016-05-27 9378

-

基于FPGA的DDS信号源研究与设计_南楠2016-05-16 587

-

基于FPGA的DDS杂散分析及抑制方法2012-11-26 890

-

FPGA+DDS实现数控信号源的设计2012-03-23 1323

-

基于DDS技术的杂散分析及抑制方法2010-07-31 1099

-

基于FPGA和DDS的信号源设计2010-02-21 2176

-

基于FPGA的DDS信号源设计与实现2010-02-11 999

-

基于DSP和DDS的三维感应测井高频信号源实现2010-01-08 1276

全部0条评论

快来发表一下你的评论吧 !