CDCM7005-SP 高性能抗辐射时钟同步器与抖动清除器总结

描述

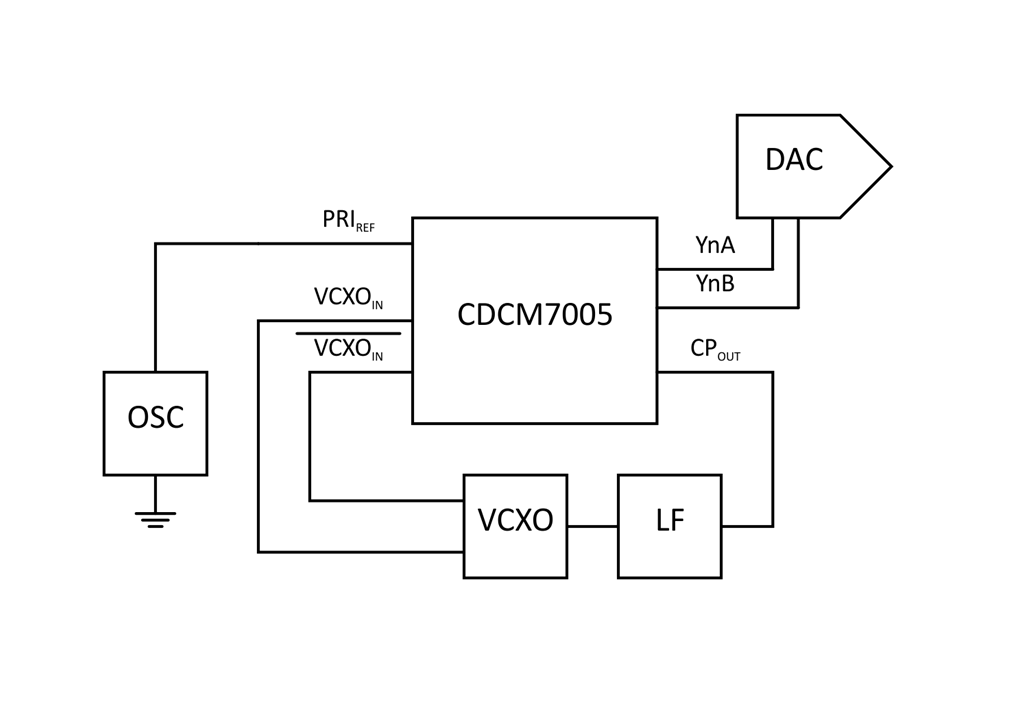

CDCM7005-SP 是一款高性能、低相位噪声和低偏斜时钟同步器 同步 VCXO(压控晶体振荡器)或 VCO(压控 振荡器)频率到两个参考时钟之一。可编程预分频器 M 和 反馈分频器 N 和 P 为参考时钟的频率比提供了高度的灵活性 VC(X)O 为 VC(X)O_IN / PRI_REF = (N × P) / M 或 VC(X)O_IN / SEC_REF = (N × P) / M。

*附件:cdcm7005-sp.pdf

VC(X)O_IN时钟工作频率高达 2 GHz。通过选择外部VC(X)O和环路 滤波器组件,PLL环路带宽和阻尼系数可调整以满足不同系统 要求。

CDCM7005-SP 可以锁定到两个参考时钟输入(PRI_REF 和 SEC_REF)之一, 支持频率保持模式和快速频率锁定,以实现故障安全和增强系统 冗余。CDCM7005-SP 的输出是用户可定义的,可以是高达 5个LVPECL输出或多达10个LVCMOS输出。LVCMOS输出成对排列(Y0A:Y0B, Y1A:Y1B,Ω),以便每对具有相同的频率。但每个输出都可以单独反转 和禁用。内置同步锁存器确保所有输出同步为低电平 输出偏差。

所有设备设置,如输出信号、分频器值、输入选择等 更多,可通过SPI(3线串行外设接口)进行编程。SPI 允许单独控制 的设备设置。

该器件在3.3 V环境中工作,工作温度为–55°C 至125°C(T 箱 ).

特性

- 高性能LVPECL和LVCMOS PLL

时钟同步器 - 两个参考时钟输入(初级和

次级时钟),用于冗余支持

,可手动或自动选择 - 接受高达 200 MHz 的

LVCMOS 输入频率 - VCXO_IN时钟与

两个参考时钟之一同步 - VCXO_IN频率高达 2 GHz (LVPECL)

- 输出可以是LVPECL和

LVCMOS的组合(最多5个差分LVPECL

输出或多达10个LVCMOS输出) - 输出频率可通过每个输出

的 x1、/2、/3、/4、

/6、/8、/16 单独选择 - 低 PLL 环路

带宽的高效抖动清除 - 低相位噪声 PLL 内核

- 可编程相位偏移(PRI_REF和

SEC_REF输出) - 电荷泵电流范围为200 μA至3 mA

- 模拟和数字 PLL 锁定指示

- 为单

端输入信号 (VCXO_IN) 提供 VBB 偏置电压输出 - 频率保持模式提高了故障安全

作 - 上电控制强制LVPECL输出在V时处于三态

CC< 1.5 伏 - SPI可控器件设置

- 3.3V 电源

- 高性能 52 针陶瓷四方扁平

包装 (HFG) - 耐辐射性:50 kRad (Si) TID

- QML-V 认证,SMD 5962-07230

- 军用温度范围:–55°C 至 125°C T

箱 - 提供工程评估 (/EM) 样品^(1)^

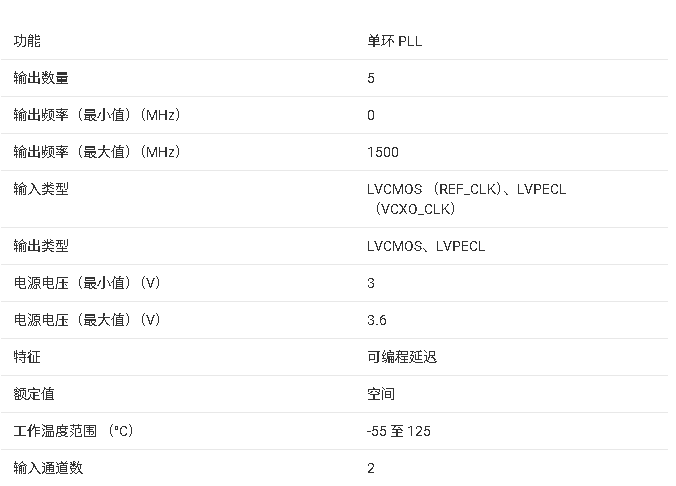

参数

方框图

1. 产品概述

CDCM7005-SP是德州仪器(TI)推出的3.3V高性能抗辐射(Rad-Tolerant)Class V时钟同步器和抖动清除器,专为严苛环境设计(如航空航天、军事应用),支持-55°C至125°C军用温度范围,符合QML-V标准(SMD 5962-07230)。

2. 核心特性

- 时钟输入:支持双参考时钟(主/备输入),频率最高200 MHz(LVCMOS)或2 GHz(LVPECL),支持手动/自动切换冗余。

- 输出配置:可配置为5对差分LVPECL或10路LVCMOS输出,支持独立分频(/1至/16)、相位偏移(可编程±1750 ps)及90°/270°相移。

- PLL性能:低相位噪声PLL核心,支持频率保持(Hold-Over)模式,提升系统容错性;电荷泵电流可调(200 μA至3 mA)。

- 抗辐射能力:耐受50 kRad(Si)总电离剂量(TID)。

3. 关键功能

- 抖动清除:通过低带宽PLL环路滤除参考时钟抖动。

- SPI控制:所有参数(分频比、输出模式等)可通过3线SPI接口编程。

- 锁相检测:提供数字/模拟锁相指示(PLL_LOCK引脚),可配置检测窗口(3.5 ns至18.5 ns)。

4. 应用场景

- 低抖动时钟分配、SERDES链路、高速ADC/DAC时钟同步。

- 典型用例:为插值DAC(如DAC5687)提供相位对齐的采样时钟,支持CPRI/OBSAI等通信标准。

5. 封装与电源

- 封装:52引脚陶瓷扁平封装(CFP/HFG),尺寸13.97 mm × 13.97 mm。

- 电源:3.3 V主电源(VCC/AVCC),电荷泵独立供电(VCC_CP:2.3 V至3.6 V)。

6. 设计支持

- 提供相位噪声优化工具(PLL-SIM),典型相位噪声性能:

- 10 kHz偏移:-153 dBc/Hz(LVCMOS输出,61.44 MHz)。

- 布局建议:高频信号最短路径布线,差分对等长处理,接地层隔离。

7. 文档与资源

- 包含详细寄存器配置表(Word 0-3)、时序图及典型应用电路(如被动环路滤波器设计)。

- 支持EVM评估模块,可通过TI社区(E2E)获取设计支持。

备注:工程评估样品(/EM)仅限非合规性测试使用,不适用于辐射测试或飞行应用。

-

CDCM7005:高性能时钟同步器与抖动清理器的深度解析2026-02-10 331

-

LMK0482x系列时钟抖动清除器:高性能时钟解决方案解析2026-02-09 288

-

解读LMK04832 - SP:空间级超低噪声时钟抖动清除器的卓越性能与应用2026-02-08 393

-

LMK5C33414A:高性能网络同步器与抖动清除器的深度剖析2026-02-06 772

-

CDC7005高性能时钟合成器与抖动清除器技术文档总结2025-09-22 887

-

CDCM7005 高性能时钟同步器和抖动清除器技术文档总结2025-09-19 1163

-

CDCE72010 高性能时钟同步器、抖动清除器和时钟分配器总结2025-09-18 1065

-

LMK5C33216A 网络同步器与抖动清除器总结2025-09-11 961

-

CDCM7005高性能时钟同步器和抖动消除器数据表2024-08-21 476

-

CDCM7005-SP高性能、低相位噪声和低偏斜时钟同步器数据表2024-08-20 466

-

AD9543:四路输入、10路输出、双DPLL/IEEE 1588同步器和抖动清除器2021-05-27 952

-

LMK04832-SP时钟抖动清除器2021-03-24 1517

-

CDCM7005-SP 3.3V 高性能抗辐射 V 类时钟同步器和抖动消除器2018-11-02 1167

全部0条评论

快来发表一下你的评论吧 !