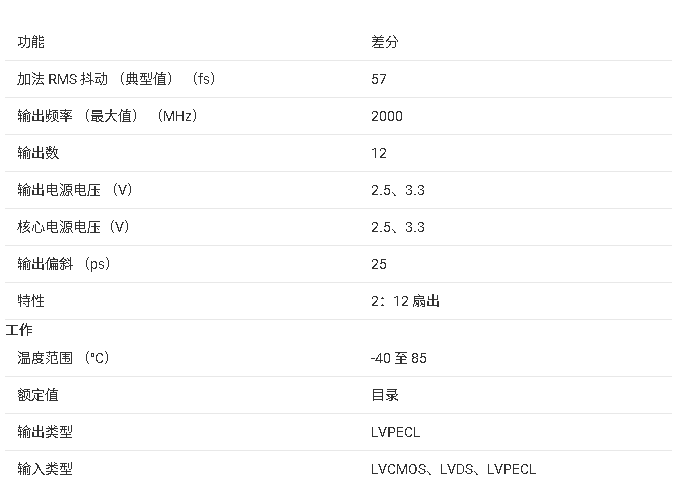

CDCLVP1212 高性能时钟缓冲器技术文档总结

描述

该CDCLVP1212是一种高度通用、低附加抖动缓冲器,可产生12 来自两个可选LVPECL、LVDS或LVCMOS输入之一的LVPECL时钟输出副本,用于 各种通信应用。它的最大时钟频率高达 2 GHz。The CDCLVP1212 具有片上多路复用器 (MUX),用于选择可轻松配置的两个输入之一 仅通过控制终端。整体加性抖动性能小于 0.1 ps,RMS 从 10 kHz 到 20 MHz,总输出偏斜低至 25 ps,使该器件成为完美的 适用于要求苛刻的应用。

*附件:cdclvp1212.pdf

CDCLVP1212时钟缓冲器将两个可选时钟输入(IN0、IN1)中的一个分配给 12对差分LVPECL时钟输出(OUT0、OUT11),时钟偏移最小 分配。该CDCLVP1212可以接受两个时钟源进入输入多路复用器。输入可以 是 LVPECL、LVDS 或 LVCMOS/LVTTL。

该CDCLVP1212专为驱动 50 Ω输电线路而设计。开车时 单端模式下的输入,LVPECL 偏置电压 (V AC_REF ) 应该是 应用于未使用的负极输入端子。但是,对于高达 2 GHz 的高速性能, 强烈建议使用差分模式。

该CDCLVP1212采用小型40端子、6mm×6mm QFN封装,具有 工作温度范围为 –40°C 至 85°C。

特性

- 2:12 差分缓冲器

- 通过控制端子选择时钟输入

- 通用输入接受LVPECL、LVDS和

LVCMOS/LVTTL - 12 个 LVPECL 输出

- 最大时钟频率:2 GHz

- 最大内核电流消耗:88 mA

- 极低的附加抖动:10 kHz 至20 MHz 失调范围内的 <100 fs、rms:

- 57 fs,rms(典型值)@ 122.88 MHz

- 48 fs,rms(典型值)@ 156.25 MHz

- 30 fs,rms(典型值)@ 312.5 MHz

- 2.375V至3.6V器件电源

- 最大传播延迟:550 ps

- 最大输出偏斜:25 ps

- LVPECL 基准电压,V

AC_REF,可用于电容耦合输入 - 工业温度范围:–40°C 至 85°C

- ESD 保护超过 2 kV (HBM)

- 支持 105°C PCB 温度(使用导热垫测量

) - 提供 6 mm × 6 mm QFN-40 (RHA) 封装

参数

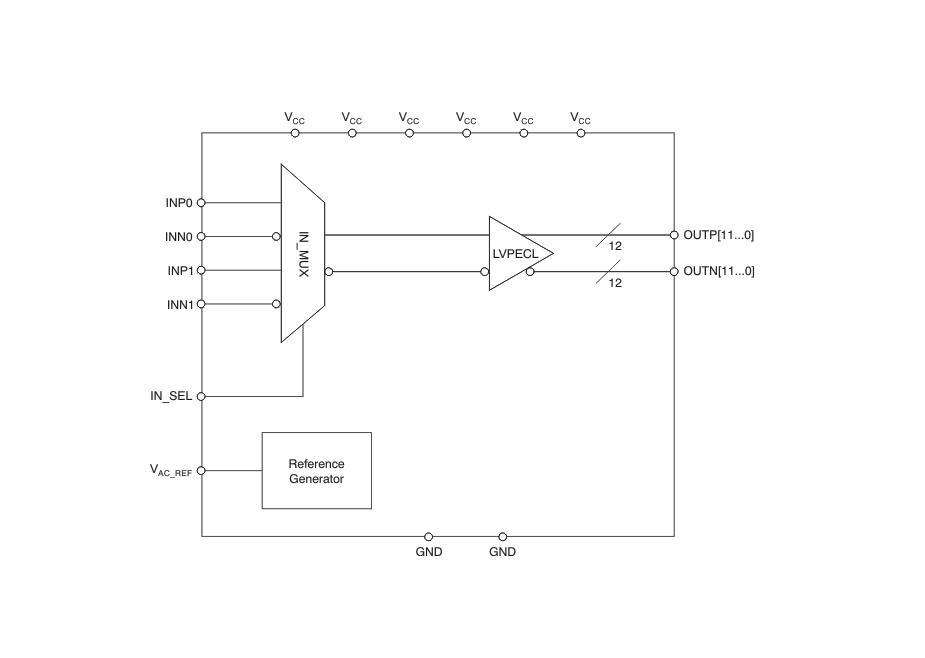

方框图

1. 产品概述

CDCLVP1212是德州仪器(TI)推出的高性能低附加抖动时钟缓冲器,可将1路LVPECL/LVDS/LVCMOS输入转换为12路LVPECL输出,适用于无线通信、医疗成像等高精度时钟分配场景。核心特性包括:

- 输入兼容性:支持双路可选输入(IN0/IN1),兼容LVPECL、LVDS、LVCMOS/LVTTL电平。

- 输出性能:12路差分LVPECL输出,最大频率2 GHz,输出偏移低至25 ps。

- 低抖动:典型附加抖动<100 fs(10 kHz-20 MHz频偏范围),特定频点如156.25 MHz时仅48 fs。

- 宽电压范围:2.375V至3.6V供电,工业级温度范围(-40°C至85°C)。

2. 关键参数

- 电气特性:

- 差分输入峰峰值电压:0.1V(≤1.5 GHz)至0.2V(2 GHz)。

- 输出差分峰峰值电压:0.5V(2.5V供电)至1.35V(3.3V供电)。

- 传播延迟:最大550 ps。

- 功耗:核心电流最大88 mA(未端接输出时)。

- 封装:6mm×6mm QFN-40封装(RHA),带散热焊盘。

3. 应用设计要点

- 输入配置:支持DC/AC耦合,单端输入时需通过VAC_REF引脚提供偏置电压。

- 输出端接:推荐50Ω端接至VCC-2V,若PCB无此电压可采用戴维南等效电路(如2.5V供电时用250Ω+62.5Ω组合)。

- 热管理:需将散热焊盘焊接至PCB地平面,并通过多通孔增强散热,确保结温≤125°C。

4. 典型应用场景

- 通信设备:如线卡时钟分配,驱动PHY、ASIC、FPGA等多负载。

- 测试仪器:高精度时钟同步,依赖其低抖动特性(实测156.25MHz输入时附加抖动47 fs)。

5. 文档结构

- 功能框图:包含输入多路复用器、参考电压生成器及12路输出驱动器。

- 修订历史:2015年12月更新,新增105°C PCB温度支持及热参数优化。

- 封装信息:提供QFN-40机械尺寸、焊盘布局及钢网设计建议。

6. 注意事项

- 未使用的输入/输出可悬空,但需注意单端输入时互补引脚处理。

- 电源需高频去耦(每供电引脚配0.1μF电容),建议串联铁氧体磁珠抑制噪声。

全部0条评论

快来发表一下你的评论吧 !