SN74SSQEA32882 芯片技术文档摘要

描述

这款符合 JEDEC SSTE32882 标准的 28 位 1:2 或 26 位 1:2 和 4 位 1:1 寄存时钟驱动器,具有奇偶校验功能,设计用于在 VDD1.5 V 和 DDR3L 寄存器 DIMM 上 VDD1.35 伏。

所有输入均兼容 1.5 V 和 1.35 V CMOS。所有输出都是经过优化的 CMOS 驱动器,可在 DDR3 RDIMM 应用中驱动端接走线上的 DRAM 信号。时钟输出 Yn 和 Yn 以及控制网络输出 DxCKEn、DxCSn 和 DxODTn 可以以不同的强度和偏斜驱动,以优化信号完整性、补偿不同的负载并均衡信号传输速度。

*附件:sn74ssqea32882.pdf

该SN74SSQEA32882具有与四芯片选择使能 (QCSEN) 输入相关的两种基本作模式。当QCSEN输入引脚开路(或拉高)时,该元件有两个芯片选择输入DCS0和DCS1,以及每个芯片选择输出的两个拷贝,QACS0、QACS1、QBCS0和QBCS1。这是“禁用 QuadCS”模式。当QCSEN输入引脚拉低时,该元件有四个芯片选择输入DCS[3:0]和四个芯片选择输出QCS[3:0]。这是“启用 QuadCS”模式。在本规范的其余部分,DCS[n:0]将指示所有芯片选择输入,其中n=1表示禁用QuadCS,n=3表示启用QuadCS。QxCS[n:0] 将指示所有芯片选择输出。

该器件还支持将单个器件安装在 DIMM 背面的模式。如果MIRROR=HIGH,则在这种情况下,输入总线终端(IBT)必须对所有输入信号保持启用状态。

SN74SSQEA32882采用差分时钟(CK和CK)工作。数据记录在 CK 变高和 CK 变低的交叉点处。该数据可以重新驱动到输出端,也可用于访问设备内部控制寄存器。

输入总线数据完整性由奇偶校验功能保护。将所有地址和命令输入信号相加,并将总和的最后一位与系统在一个时钟周期后PAR_IN输入端提供的奇偶校验信号进行比较。如果它们不匹配,器件将拉开漏输出 ERROUT LOW。控制信号(DCKE0、DCKE1、DODT0、DODT1、DCS[n:0])不属于此计算的一部分。

该SN74SSQEA32882实现了不同的省电机制,以减少热功耗并支持系统断电状态。通过禁用未使用的输出,功耗进一步降低。

该封装经过优化,可支持高密度 DIMM。通过将输入和输出位置对齐 DIMM 手指信号排序和 SDRAM 球出,该器件可以对 DIMM 走线进行去扰乱,从而实现低串扰设计和低互连延迟。

边沿控制输出可减少振铃并改善SDRAM输入端的信号眼图开度。

特性

- 符合 JEDEC SSTE32882标准

- 1 对 2 寄存器输出和 1 对 4 时钟对输出支持

堆叠式 DDR3 RDIMM - CKE 掉电模式可优化系统功耗

- 1.5V/1.35V锁相环时钟驱动器,用于缓冲一个

差分时钟对(CK和CK)并分配

到四个差分输出 - 1.5V/1.35V CMOS输入

- 检查命令和地址(CS 门控)数据输入的奇偶校验

- 可配置的驱动器强度

- 使用内部反馈回路

- 应用

- DDR3 寄存器 DIMM,最高可达 DDR3-1600

- DDR3L 寄存器 DIMM,最高可达 DDR3L-1333

- 单列、双列和四列 RDIMM

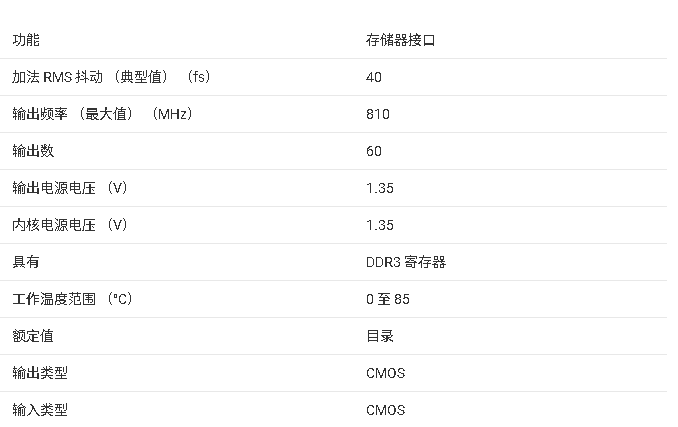

参数

1. 产品概述

SN74SSQEA32882 是一款符合 JEDEC SSTE32882 标准的 28 位至 56 位注册缓冲器,集成地址奇偶校验功能和 1:4 差分时钟 PLL 驱动器,专为 DDR3/DDR3L 寄存式 DIMM(RDIMM)设计。

- 工作电压:支持 DDR3(1.5V)和 DDR3L(1.35V)。

- 核心功能:

- 1:2 寄存器输出和 1:4 时钟对输出,支持堆叠式 DDR3 RDIMM。

- 奇偶校验保护命令和地址输入数据。

- 可配置驱动强度和时钟相位调整。

2. 关键特性

- 低功耗设计:支持 CKE 省电模式,可禁用未使用的输出以降低功耗。

- 时钟驱动:通过内部 PLL 缓冲 1 对差分时钟(CK/CK)并分配至 4 对差分输出。

- 模式配置:

- QuadCS 模式:通过 QCSEN 引脚选择 2 或 4 个片选信号(DCS/QCS)。

- 镜像模式:支持背对背安装(MIRROR=HIGH)。

3. 应用场景

- DDR3 RDIMM(最高 DDR3-1600)和 DDR3L RDIMM(最高 DDR3L-1333)。

- 单/双/四列 RDIMM 模块。

4. 封装与引脚

- 封装:176 球 BGA(8mm×13.5mm,0.65mm 球间距),优化高密度 DIMM 布局。

- 引脚配置:

- 支持前/后配置(通过 MIRROR 引脚选择)。

- 保留引脚(如 A9、W7)需悬空或焊盘预留。

5. 电气特性

- 绝对最大额定值:

- 电源电压:-0.4V 至 +1.975V。

- 工作温度:依速度等级不同(DDR3-800 至 DDR3-1600)为 +103°C 至 +109°C。

6. 附加信息

- SPD 配置:提供厂商特定字节(如 Vendor ID 0x8097,Revision ID 0x28)。

- 文档声明:包含德州仪器标准免责条款,强调 ESD 防护和关键应用注意事项。

-

解析SN74SSQEA32882:DDR3/DDR3L注册时钟驱动器的卓越之选2026-04-23 198

-

探索 SN74SSQEC32882:DDR3 注册 DIMM 的理想时钟驱动器2026-02-09 336

-

SN74SSQEB32882 芯片技术文档摘要2025-09-16 783

-

SN74SSQEC32882 芯片技术文档总结2025-09-15 981

-

SN74CBTD3306能用于2.5V-3.3V双向电平转换吗?2025-02-05 387

-

请问SN74LV165A和SN74LV4040A芯片VQFN封装的Thermal pad是否需要接地?2024-12-17 573

-

ARM芯片为什么能够直连SN74LVC1G17?2024-12-03 581

-

SSQEA32882差分时钟PLL驱动器数据表2024-08-23 335

-

SN74SSQE32882寄存器缓冲器数据表2024-08-22 411

-

请问SN74系列的芯片是用于什么方面的?2018-07-05 3373

-

SN74AHCT245DW芯片问题2017-12-23 6895

-

SN74V3640,SN74V3650,SN74V3660,2010-08-19 737

全部0条评论

快来发表一下你的评论吧 !