TPS50601A-SP Buck Converter评估模块深度解析

描述

Texas Instruments TPS50601ASPEVM-S转换器评估模块 (EVM) 设计用于获取TPS5061A-SP的各种特性。TPS50601A-SP是一款辐射硬化型6.3V、6A同步降压转换器,通过高效集成高侧和低侧MOSFET进行了小尺寸设计优化。通过电流模式控制进一步节省空间,从而降低元件数量,并且高开关频率减少了电感器占位面积。Texas Instruments TPS50601ASPEVM-S的布局方便客户按用户需求修改配置,并针对不同的输入、输出电容器和输出电感器进行调整。

数据手册:*附件:Texas Instruments TPS50601ASPEVM-S转换器评估模块数据手册.pdf

特性

- 辐射硬化型同步降压转换器,采用散热增强型封装

- 逐周期电流限制实现电流模式控制

- 逻辑电路的分路输入电压V

IN和MOSFET的分路输入电压PVIN - 灵活的开关频率(从100kHz到1Mhz

- 通过外部电容器可调节软启动时间

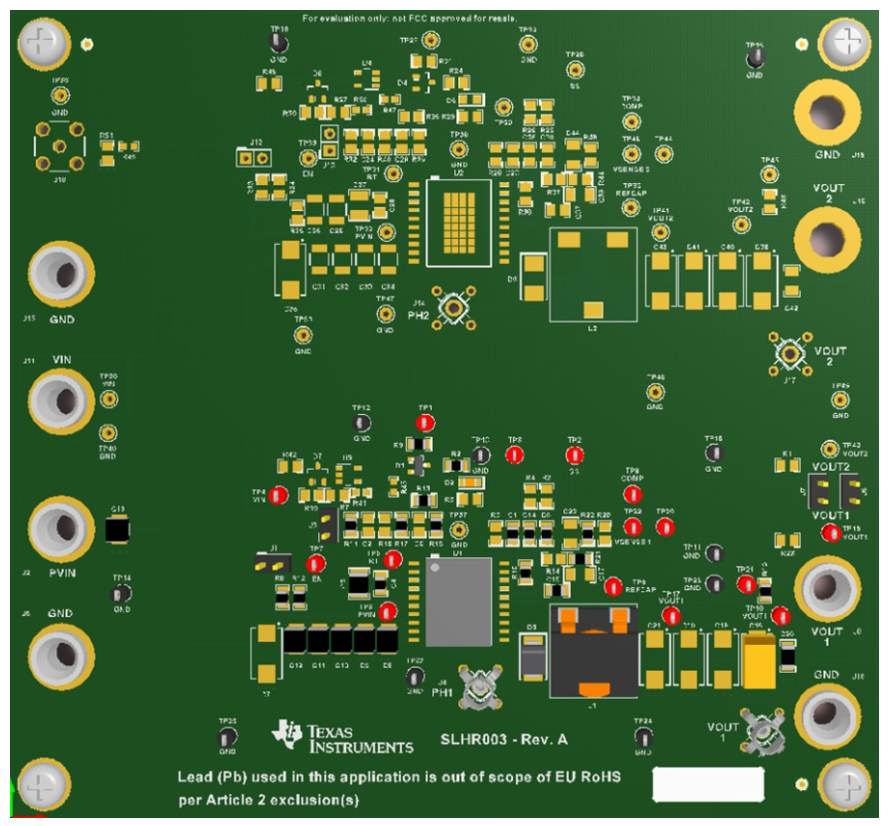

板布局

TPS50601A-SP Buck Converter评估模块深度解析

一、产品概述

Texas Instruments的TPS50601ASPEVM-S是一款用于评估TPS50601A-SP同步降压转换器性能的开发模块。该评估板基于TPS50601A-SP芯片设计,具有以下显著特点:

- 宽输入电压范围:3V至6.3V(PVIN=VIN配置)

- 高输出电流:最大6A连续输出

- 可调输出电压:通过外部电阻网络配置(默认2.5V)

- 开关频率:100kHz(可调至1MHz)

- 高效率设计:峰值效率达95%(VIN=5V,VOUT=2.5V,1A负载时)

二、关键性能参数

根据测试数据,模块在25°C环境温度下表现如下:

| 参数 | 测试条件 | 典型值 |

|---|---|---|

| 输入电压范围 | PVIN=VIN | 4.5-6.3V |

| 启动电压 | 无负载 | 4.5V |

| 关断电压 | 无负载 | 4.3V |

| 输出电压精度 | VIN=5V | 2.49V |

| 峰值效率 | VIN=5V, IOUT=1A | 95% |

| 负载调整率 | 0-6A | ±0.7% |

三、硬件配置与设计

3.1 功率架构

评估板采用四层PCB设计(2oz铜厚),包含:

- 输入滤波电路:多颗22μF陶瓷电容(C8-C13)并联

- 功率转换电路:集成MOSFET的TPS50601A-SP芯片

- 输出滤波电路:330μF聚合物钽电容(C7)搭配4.7μH电感(L1)

3.2 关键配置选项

- 输出电压设置:

- 通过R21(10kΩ)和R22(4.7kΩ)电阻分压网络设定

- 计算公式:VOUT = 0.804V × (1 + R22/R21)

- 常见配置:

- 1.2V输出:R22=20kΩ

- 1.8V输出:R22=8.06kΩ

- 3.3V输出:R22=3.2kΩ

- 使能控制:

- J3跳线连接EN至GND可禁用输出

- 默认通过R13(10kΩ)和R15(3.4kΩ)设置UVLO阈值

- 缓启动时间:

- 由C1(0.01μF)设定,计算公式:Tss = (C1 × 0.804V)/2μA

- 默认4ms启动时间

四、PCB布局要点

- 层叠结构:

- 顶层:主功率走线(PVIN/VIN/VOUT)

- 第二层:完整地平面

- 第三层:信号走线

- 底层:辅助地平面

- 关键布局原则:

- 输入电容(C8-C13)尽可能靠近IC放置

- 电压设定分压电阻靠近FB引脚

- 功率地(PGND)与信号地(AGND)单点连接

- IC底部添加多个散热过孔(连接各层地平面)

- 热管理:

- 采用20引脚HKW封装(带裸露散热垫)

- 底层铜箔作为辅助散热路径

五、典型测试结果

- 效率曲线:

- 峰值效率95% @1A负载

- 6A满载时效率约88%

- 动态响应:

- 3mA→5A负载阶跃时输出电压偏差<50mV

- 环路带宽:约15kHz(相位裕度60°)

- 纹波性能:

- 输出纹波:<20mVpp @6A(20MHz带宽限制)

- 输入纹波:<50mVpp @6A

六、应用设计指南

- 元件选型建议:

- 电感:推荐4.7μH/9.4A饱和电流

- 输出电容:低ESR聚合物钽电容(330μF/10V)

- 补偿网络:R16=2.26kΩ, C14=33nF, C6=680pF

- 辐射敏感设计:

- 采用星型接地策略

- 敏感信号远离高频开关节点

- 增加局部去耦电容(C20=0.1μF)

- 高可靠性设计:

- 所有元件符合AEC-Q200标准

- 关键电阻采用0.1%精度(R21/R22)

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

TPS56921 Buck Converter评估模块:性能、设置与设计详解2026-04-25 331

-

TPS51020 Buck 控制器评估模块深度解析2026-04-24 289

-

TPS23750 Buck-Converter评估板HPA107:设计与应用解析2026-04-23 148

-

TPS50601A-SP:辐射加固同步降压转换器的深度解析2026-02-05 422

-

TPS50601A-SP 抗辐射 QMLV、3V 至 7V 输入、6A 同步降压转换器数据手册2025-06-23 968

-

TPS50601A-SP最坏情况分析未加密PSpice平均模型用户指南2024-11-29 422

-

TPS50601x-SP比较指南2024-09-25 362

-

耐辐射3V至7V输入、6A 同步降压转换器TPS50601A-SP数据表2024-04-03 492

-

TPS50601-SP MINI POL转换器的参考设计2022-09-23 3248

-

TPS50601 SP MINI POL转换器参考设计2022-09-07 880

-

TPS50601-SP V 类 1.6V 至 6.3V 输入、6A 同步降压 SWIFT 转换器2018-11-02 4986

-

TPS50601-SP DC/DC 转换器设计参考2018-07-24 4023

全部0条评论

快来发表一下你的评论吧 !