CDCS503 时钟缓冲器/时钟倍频器技术文档总结

描述

该CDCS503是一款具有扩频功能的LVCMOS输入时钟缓冲器,具有可选的倍频功能。

它与CDCS502共享主要功能,但使用 LVCMOS 输入级而不是CDCS502的晶体输入级。此外,CDCS503中还添加了一个输出使能引脚。

*附件:cdcs503.pdf

该器件在输入端接受3.3V LVCMOS信号。

输入信号由PLL处理,其输出频率等于输入频率或乘以4倍。

PLL 还能够通过三角调制将时钟信号以输出时钟频率为中心以 ±0%、±0.5%、±1% 或 ±2% 的分布。

通过这种方式,该器件可以在有或没有SSC的情况下产生8MHz至108MHz之间的输出频率。

可以使用单独的控制引脚来启用或禁用输出。该CDCS503在 3.3V 环境中工作。

它的工作温度范围为–40°C至85°C,采用8引脚TSSOP封装。

特性

- 易于使用的时钟发生器器件

系列的一部分,带有可选的 SSC - 具有可选输出频率和

可选SSC的时钟乘法器 - SSC 可通过 2 个外部引脚控制

- ±0%、±0.5%、±1%、±2% 中心价差

- 频率倍增可在 x1 或 x4

之间选择,带有一个外部控制引脚 - 通过控制引脚输出禁用

- 单 3.3V 器件电源

- 宽温度范围 –40°C 至 85°C

- 采用8引脚TSSOP封装,空间消耗低

- 应用

- 需要

通过扩频时钟

和/或时钟倍增降低EMI的消费类和工业应用

参数

- 需要

1. 产品概述

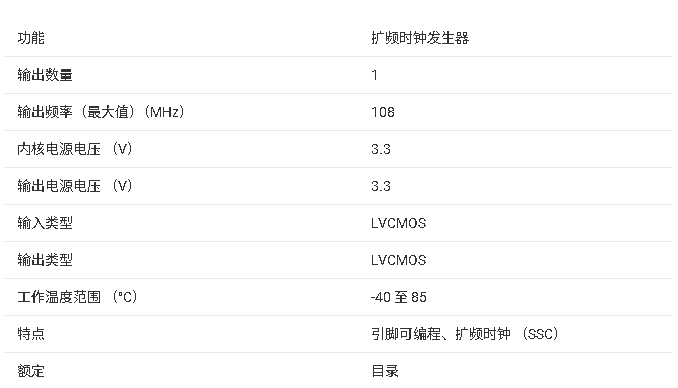

CDCS503是德州仪器(TI)推出的具有可选扩频时钟(SSC)功能的LVCMOS输入时钟缓冲器/倍频器,属于易用型时钟发生器系列。核心特性包括:

- 频率倍频:通过外部引脚选择×1或×4倍频模式。

- 扩频控制:支持±0%、±0.5%、±1%、±2%中心扩频调制(三角波),通过2个引脚配置。

- 输出使能:独立控制引脚(OE)可禁用输出。

- 工作条件:3.3V单电源供电,温度范围-40°C至85°C,8引脚TSSOP封装。

2. 关键功能

- 输入/输出:LVCMOS电平兼容,输入频率范围8MHz–32MHz(×1模式)或8MHz–27MHz(×4模式),输出频率最高108MHz。

- 扩频调制:调制频率由输入频率和倍频模式决定(公式:FS=0时f_mod=f_IN/708;FS=1时f_mod=f_IN/620)。

- 低功耗设计:典型供电电流19mA(20MHz无SSC)。

3. 应用场景

- 消费电子和工业设备中需通过扩频时钟降低EMI的场合。

- 需要灵活时钟倍频或缓冲的电路设计。

4. 封装与订购信息

- 封装:8引脚TSSOP(PW),符合RoHS标准。

- 型号选项:含标准型号(如CDCS503PW)和汽车级(CDCS503-Q1)。

5. 技术参数

- 电气特性:输出抖动(典型110ps)、上升/下降时间(≤2ns)、占空比(45%–55%)。

- 绝对最大额定值:电源电压-0.5V至4.6V,存储温度-65°C至150°C。

6. 设计支持

- 提供测试负载电路图(10pF容性负载)和50Ω板级环境匹配建议。

- 文档包含热阻数据(θJA=65°C/W)和封装尺寸图。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

汽车级时钟缓冲器/乘法器CDCS503-Q1:特性、应用与设计要点2026-02-09 214

-

汽车级时钟缓冲器与乘法器 CDCS504-Q1 设计指南2026-02-08 309

-

时钟缓冲器技术选型与设计要点2025-12-16 618

-

LMH2180 75 MHz双时钟缓冲器技术文档总结2025-09-18 800

-

CDCS501 时钟发生器/缓冲器技术文档总结2025-09-17 830

-

CDCS503-Q1 时钟缓冲器/时钟倍频器技术文档总结2025-09-15 1037

-

CDCS504-Q1 时钟缓冲器和时钟乘法器技术文档总结2025-09-12 1229

-

CDCS504-Q1时钟缓冲器和时钟乘法器数据表2024-08-23 448

-

CDCS503带可选SSC的时钟缓冲器/时钟乘法器数据表2024-08-22 464

-

什么是时钟缓冲器(Buffer)?时钟缓冲器(Buffer)参数解析2022-10-18 31179

-

时钟缓冲器选型目录2021-11-19 2473

-

CDCS503-Q1带有可选展频时钟(SSC) 的时钟缓冲器倍乘器的数据手册2018-11-20 1083

全部0条评论

快来发表一下你的评论吧 !