CDCM61001 低抖动时钟发生器技术文档总结

描述

该CDCM61001是一款高度通用的低抖动频率合成器,可从低频晶体或LVCMOS输入生成低抖动时钟输出,可在低压正发射极耦合逻辑(LVPECL)、低压差分信号(LVDS)或低压互补金属氧化物半导体(LVCMOS)输出之间进行选择,适用于各种有线和数据通信应用。该CDCM61001具有板载PLL,只需通过控制引脚即可轻松配置。整体输出随机抖动性能小于 1ps、RMS(从 10 kHz 到 20 MHz),使该器件成为 SONET、以太网、光纤通道和 SAN 等要求苛刻应用的完美选择。该CDCM61001采用小型 32 引脚、5 mm × 5 mm QFN 封装。

*附件:cdcm61001.pdf

该CDCM61001是一款高性能、低相位噪声、全集成压控振荡器(VCO)时钟合成器,具有一个通用输出缓冲器,可配置为与LVPECL、LVDS或LVCMOS兼容。通用输出也可以转换为两个LVCMOS输出。此外,LVCMOS 旁路输出时钟可在输出配置中提供,有助于晶体负载,以实现精确所需的输入频率。它有一个完全集成、低噪声、基于LC的VCO,工作频率范围为1.75 GHz至2.05 GHz。

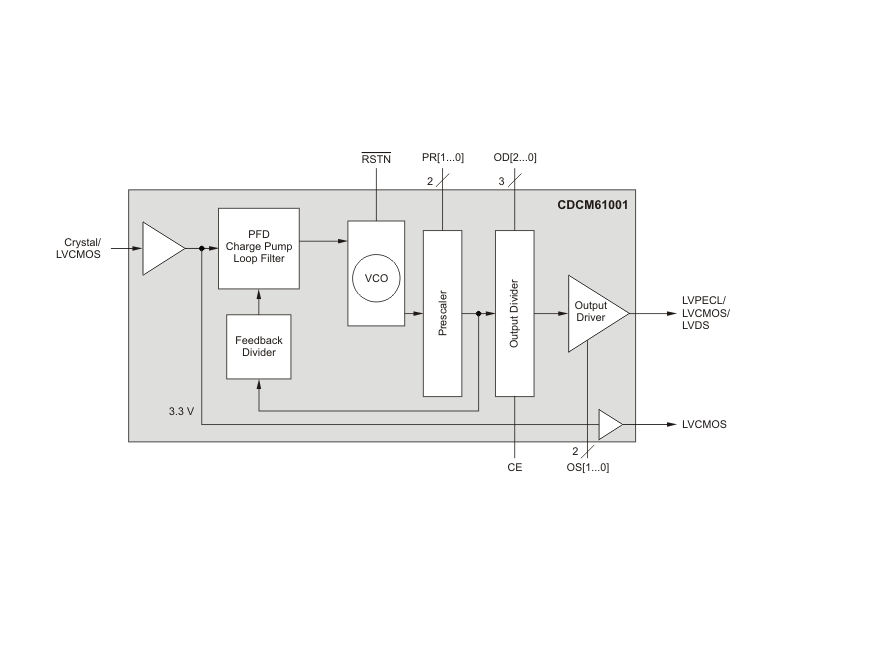

锁相环 (PLL) 使 VCO 相对于输入同步,输入可以是低频晶体。输出具有来自VCO内核的输出分压器。所有器件设置都通过控制引脚结构进行管理,该结构有两个控制预分频器和反馈分频器的引脚,三个控制输出分频器的引脚,两个控制输出类型的引脚,以及一个控制输出使能的引脚。每当PLL设置(包括输入频率、预分频器分频器或反馈分频器)发生变化时,都必须通过Reset控制引脚发出复位(器件复位为低电平有效)。复位启动 PLL 重新校准过程以确保 PLL 锁定。当器件处于复位状态时,输出和分压器关闭。

输出频率(f 外 )与输入时钟的频率成正比(f 在 ).反馈分频器、输出分频器和VCO频率集f外关于 f 在 .有关常见有线和数据通信应用程序的配置设置,请参阅。对于其他应用,用于计算所需输出所需的精确晶体振荡器频率。

通过使用控制引脚,可以从 1、2、3、4、6 或 8 中选择输出分压器。反馈分频器和预分频器分频器组合可以分别从 25 和 3、24 和 3、20 和 4 或 15 和 5 中进行选择,也可以使用控制引脚。显示了CDCM61001的高级框图。

该器件在3.3 V电源环境中工作,工作温度范围为–40°C至+85°C。

特性

- 一个晶体/LVCMOS基准输入,包括24.8832 MHz、25 MHz和

26.5625 MHz - 输入频率范围:21.875 MHz 至

28.47 MHz - 片上VCO工作频率范围为1.75 GHz至2.05 GHz

- 1x 可用输出:

- 引脚可在 LVPECL、LVDS 或 2-LVCMOS 之间选择;工作电压为 3.3 V

- 提供LVCMOS旁路输出

- 输出频率可通过输出分频器的 /1、/2、/3、/4、/6、/8

选择 - 支持常见的 LVPECL/LVDS 输出频率:

- 62.5 兆赫、74.25 兆赫、75 兆赫、77.76 兆赫、100 兆赫、106.25 兆赫、125 兆赫、

150 兆赫、155.52 兆赫、156.25 兆赫、159.375 兆赫、187.5 兆赫、200 兆赫、212.5 兆赫、

250 兆赫、311.04 兆赫、312.5 兆赫、622.08 兆赫、625 兆赫

- 62.5 兆赫、74.25 兆赫、75 兆赫、77.76 兆赫、100 兆赫、106.25 兆赫、125 兆赫、

- 支持常见的LVCMOS输出频率:

- 62.5 兆赫、74.25 兆赫、75 兆赫、77.76 兆赫、100 兆赫、106.25 兆赫、125 兆赫、

150 兆赫、155.52 兆赫、156.25 兆赫、159.375 兆赫、187.5 兆赫、200 兆赫、

212.5 兆赫、250 兆赫

- 62.5 兆赫、74.25 兆赫、75 兆赫、77.76 兆赫、100 兆赫、106.25 兆赫、125 兆赫、

- 输出频率范围:43.75 MHz 至 683.264 MHz

- 内部PLL环路带宽:400 kHz

- 高性能 PLL 内核:

- 相位噪声通常为–146 dBc/Hz,5 MHz失调

,625 MHz LVPECL输出 - 随机抖动通常为 0.509 ps,RMS(10 kHz 至 20 MHz),

适用于 625 MHz LVPECL 输出

- 相位噪声通常为–146 dBc/Hz,5 MHz失调

- 输出占空比校正至 50% (± 5%)

- 使用控制引脚进行分频器编程:

- 两个引脚,用于预分频器/反馈分频器

- 三个用于输出分压器的引脚

- 两个用于输出选择的引脚

- 提供芯片使能和器件复位控制引脚

- 3.3V 内核和 I/O 电源

- 工业温度范围:–40°C 至 +85°C

- 5mm × 5mm、32引脚、QFN (RHB) 封装

- ESD 保护超过 2 kV (HBM)

参数

方框图

1. 产品概述

CDCM61001是德州仪器(TI)推出的高性能、低相位噪声时钟发生器,集成电压控制振荡器(VCO),支持多种输出类型(LVPECL/LVDS/LVCMOS)。其核心特性包括:

- 输入频率范围:21.875 MHz至28.47 MHz,兼容晶体或LVCMOS参考输入。

- VCO频率范围:1.75 GHz至2.05 GHz,支持分频输出(/1至/8)。

- 输出频率范围:43.75 MHz至683.264 MHz,覆盖常见通信标准(如SONET、以太网、SATA等)。

- 低抖动性能:随机抖动典型值0.509 ps(RMS,10 kHz–20 MHz),相位噪声低至-146 dBc/Hz(625 MHz LVPECL输出)。

2. 关键特性

- 灵活配置:通过控制引脚设置分频器(反馈/输出)、输出类型及使能状态。

- 多输出模式:支持LVPECL、LVDS或2路LVCMOS输出,并集成LVCMOS旁路输出。

- 高集成度:内置PLL、LDO稳压器及ESD保护(>2 kV HBM),采用5 mm × 5 mm QFN-32封装。

3. 应用场景

- 高端数据通信(SONET、10G以太网、光纤通道)。

- 替代高频晶体振荡器,降低成本。

- 高清视频(HDTV)、存储网络(SAN)等时序敏感系统。

4. 电气特性

- 电源要求:3.3 V ±10%,工业温度范围(-40°C至+85°C)。

- 功耗:典型值339.9 mW(LVPECL输出@312.5 MHz)。

- 启动时间:约2.25 ms(含VCO校准和PLL锁定)。

5. 设计注意事项

- 热管理:需焊接裸露焊盘至PCB地平面以优化散热。

- 电源滤波:建议使用铁氧体磁珠隔离模拟与数字电源,并就近放置去耦电容。

- 输出端接:提供LVPECL/LVDS/LVCMOS的推荐端接电路(如150 Ω电阻网络)。

6. 文档结构

- 包含特性说明、引脚定义、电气参数、典型应用电路及封装信息。

- 提供配置表(如分频比、输出类型选择)和热阻数据。

-

CDCM6208:多功能时钟发生器与抖动清理器的深度解析2026-02-09 232

-

CDCM6208V1F:多功能低抖动时钟发生器的深度剖析2026-02-08 1184

-

CDCM61002 低抖动时钟发生器技术文档总结2025-09-18 1003

-

CDCM9102低噪声双通道100MHz时钟发生器技术文档总结2025-09-15 1083

-

CDCM61002两路输出、集成VCO、低抖动时钟发生器数据表2024-08-22 944

-

AD9540:655 MHz低抖动时钟发生器数据表2021-03-22 805

-

AD9525: 8路LVPECL输出低抖动时钟发生器2021-03-21 860

-

cdcm61001一个输出集成压控振荡器低抖动时钟发生器2017-09-25 946

-

评估低抖动PLL时钟发生器的电源噪声抑制性能2009-09-18 1913

全部0条评论

快来发表一下你的评论吧 !