CDCE62005 时钟发生器芯片技术文档总结

描述

CDCE62005是一款高性能时钟发生器和分配器,具有低输出 抖动、通过SPI接口实现高度可配置以及可编程启动模式 由片上EEPROM确定。专为时钟数据转换器和高速定制 数字信号,该CDCE62005的抖动性能远低于 1 ps RMS(10 kHz 至 20 MHz 集成带宽)。

*附件:cdce62005.pdf

该CDCE62005集成了一个带有部分集成环路滤波器的合成器模块,一个 时钟分配模块,包括可编程输出格式,以及具有 创新的智能多路复用器。时钟分配块包括五个可单独编程的 可配置为提供不同输出格式组合的输出(LVPECL、LVDS、 LVCMOS)。每个输出还可以编程为唯一的输出频率(高达 1.5 GHz)和偏斜 通过可编程延迟模块建立关系(请注意,频率范围取决于工作模式 并选择输出格式)。如果所有输出都配置为单端模式(例如, LVCMOS),该CDCE62005支持多达十个输出。每个输出可以选择四个时钟源之一 调节和分配,包括三个时钟输入中的任何一个或频率的输出 合成器。输入模块包括两个支持频率的通用差分输入 在 40 kHz 至 500 MHz 范围内,以及可配置为连接到 通过片上振荡器模块进行外部晶体。

智能输入多路复用器有手动和自动两种作模式。在手册中 模式下,用户通过SPI接口选择合成器基准电压源。在自动模式下, 输入多路复用器将自动在最高优先级输入时钟之间进行选择 可用。

特性

- 卓越的性能:

- 低噪声时钟发生器:550 fs rms(典型值)(10 kHz至20 MHz积分带宽),F

C= 100兆赫 - 低噪声抖动清除器:2.6 ps rms(典型值)(10 kHz至20 MHz积分带宽),F

C= 100兆赫

- 低噪声时钟发生器:550 fs rms(典型值)(10 kHz至20 MHz积分带宽),F

- 灵活的频率规划:

- 5 个完全可配置的输出:LVPECL、LVDS、LVCMOS 和特殊的高摆幅输出模式

- 独特的双VCO架构支持宽调谐范围:1.750 GHz至2.356 GHz

- 频率范围为4.25 MHz至1.175 GHz(合成器模式)

- 扇出模式下输出频率高达 1.5 GHz

- 所有输出的独立粗偏控制

- 高灵活性:

- 集成EEPROM在上电时确定器件配置

- 智能输入多路复用器可在三个基准输入之一之间自动切换

- 7mm × 7mm 48引脚VQFN封装(RGZ)

- –40°C 至 +85°C 温度范围

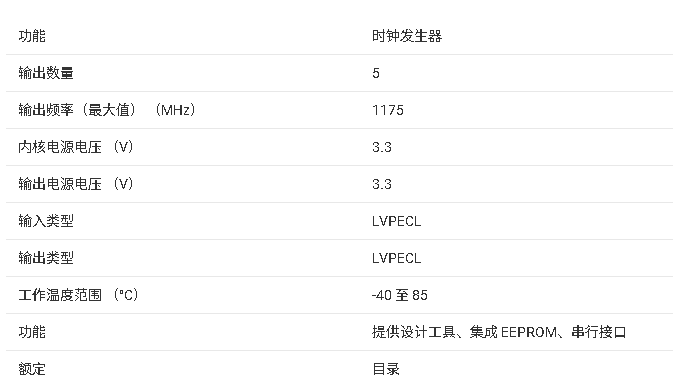

参数

方框图

1. 核心功能

- 高性能时钟生成与抖动清理:集成双VCO架构,支持合成器模式(4.25 MHz至1.175 GHz)和扇出模式(最高1.5 GHz),典型抖动性能低至550 fs RMS(时钟生成模式)和2.6 ps RMS(抖动清理模式)。

- 灵活输出配置:5个可编程输出端口,支持LVPECL、LVDS、LVCMOS等多种电平格式,每个输出可独立设置频率、延迟和格式。

- 智能输入多路复用器:自动或手动切换3个参考时钟输入,支持40 kHz至500 MHz频率范围。

2. 关键特性

- 双VCO架构:宽调谐范围1.750 GHz至2.356 GHz,适应复杂频率规划需求。

- 集成EEPROM:上电时自动加载配置,支持SPI接口实时编程。

- 低功耗设计:3.3V供电,48引脚VQFN封装(7mm×7mm),工作温度-40°C至+85°C。

3. 应用场景

- 无线基础设施、网络交换机/路由器

- 医疗电子、航空航天及工业设备

- 高速数据转换器(ADC/DAC)时钟同步

4. 技术细节

- 输入接口:支持差分输入、外部晶体振荡器(通过AUX_IN引脚)。

- 输出控制:每个输出可独立选择时钟源(输入或合成器),支持粗调延迟(coarse skew)。

- SPI控制:通过寄存器映射配置频率、输出模式及系统状态。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

深度剖析CDCE62002:高性能时钟发生器的卓越之选2026-02-09 461

-

CDCE62002 四输出时钟发生器/抖动清除器技术文档总结2025-09-17 923

-

CDCE6214 超低功耗时钟发生器技术文档总结2025-09-12 907

-

CDCE62005作为PLL需要外部输入时钟多少MHz?2025-01-10 746

-

DAC3482用CDCE62005做时钟发生器,产生的FIFO-OSTR又经过了时钟缓冲器CDCP1803,CDCP1803的作用是什么?2024-12-20 510

-

板子上没有主控芯片给CDCE62005发送命令,如何设置它的时钟输出呢?2024-11-12 794

-

CDCE62005高性能时钟发生器和分配器数据表2024-08-21 476

-

CDCE62005 具有集成双路 VCO 的 5/10 路输出时钟发生器/抖动消除器2019-04-18 568

-

请问6678开发板TMDXEVM6678上CDCE62005的寄存器配置的数据是什么2018-08-06 2402

-

CDCE62005第0通道没有时钟输出2018-06-21 1990

全部0条评论

快来发表一下你的评论吧 !