LMK1D1216EVM缓冲器评估模块技术解析与应用指南

描述

Texas Instruments LMK1D1216EVM缓冲器评估模块 (EVM) 设计用于演示LMK1D1216的电气性能。LMK1D1216是一款高性能、低附加抖动LVDS时钟缓冲器,具有两路差分输入和八路LVDS输出。该评估模块还可以用于评估LMK1Dxxxx系列中的其他48引脚器件。Texas Instruments LMK1D1216EVM配备50Ω SMA连接器和阻抗控制的50Ω微带传输线路,从而获得出色的性能。

数据手册:*附件:Texas Instruments LMK1D1216EVM缓冲器评估模块 (EVM)数据手册.pdf

特性

- 简单易用的评估板,用于扇出低相位噪声时钟

- 支持高达2GHz的输出频率

- 简单、快速的器件配置和设置

- 控制引脚可通过跳线进行配置

- 单电源输入:1.8V、2.5V或3.3V

- 接受差分或单端输入时钟

- 评估模块支持所有16路差分LVDS输出

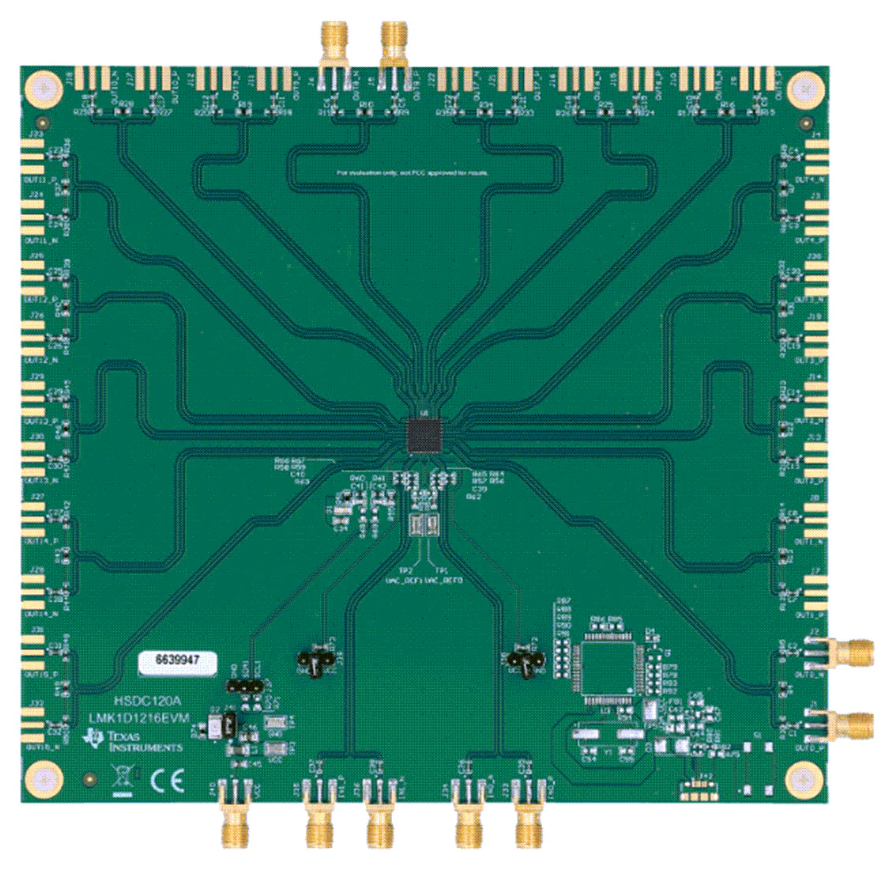

板布局

LMK1D1216EVM缓冲器评估模块技术解析与应用指南

一、产品概述

LMK1D1216EVM是德州仪器(TI)推出的一款高性能低附加抖动LVDS时钟缓冲器评估模块,具有以下核心特性:

- 高性能缓冲:支持最高2GHz输出频率的低附加抖动时钟分配

- 灵活输入配置:支持2路通用输入(差分或单端)和1路输入选择控制

- 丰富输出:提供16路LVDS时钟输出

- 宽电压支持:单电源供电(1.71V至3.465V)

- 汽车级认证:符合AEC-Q100 Grade 1标准(-40°C至+150°C)

该模块采用LMK1D1216RGZ芯片,具有优异的抖动性能和灵活的配置选项,适用于高速时钟分配应用。

二、关键性能参数

1. 电气特性

输入特性:

- 输入频率范围:

- 单端输入:最高250MHz

- 差分输入:最高2GHz

- 输入类型:支持LVDS、LVPECL、HCSL、CML、LVCMOS等

输出特性:

- 输出类型:16路LVDS

- 输出阻抗:100Ω(板上已集成终端电阻)

- 输出抖动:极低附加抖动(<100fs RMS典型值)

电源特性:

- 供电电压范围:1.71V至3.465V

- 典型功耗:<100mW(3.3V供电时)

三、模块设计与应用

1. 快速启动指南

- 将电源连接到J40(VDD)或TP3(VCC)/TP4(GND)测试点

- 选择输入时钟源:

- 差分输入:通过J33/J34(IN0)或J35/J36(IN1)

- 单端输入:需修改板上配置(详见单端输入配置部分)

- 使用J39跳线选择输入源(IN0或IN1)

- 输出时钟可通过J1/J2(OUT0)和J5/J6(OUT8)获取

2. 关键功能模块

- 输入选择:通过J39跳线选择IN0或IN1作为输入源

- 电源滤波:板上集成多级电源滤波网络

- 输出终端:每对LVDS输出已集成100Ω终端电阻

- 配置接口:支持通过I2C接口进行高级配置(LMK1D1216I版本)

3. 安全注意事项

- 操作时需遵循TI高压评估用户安全指南

- 仅限专业人员在实验室环境使用

- 禁止在无人值守时保持模块供电

- 注意静电防护(ESD),避免直接触摸器件引脚

四、设计实现细节

1. 输入配置选项

模块支持多种输入配置方式:

差分输入(默认配置) :

- 通过J33/J34(IN0)或J35/J36(IN1)接入

- 输入AC耦合,共模电压由芯片内部偏置提供

单端输入配置:

需修改板上元件配置,典型配置包括:

- 移除偏置电阻(R56/R58)和共模电阻(R38/R39)

- 根据输入电压替换相应电阻(0.9V/1.25V/1.65V偏置)

- 详细配置参见数据手册表6-1

2. PCB布局特点

- 4层板设计(顶层/底层+2个中间层)

- 50Ω阻抗控制微带传输线

- 优化电源分配网络

- 关键信号远离噪声源

- 充分的接地设计

五、典型应用场景

- 高速数据采集系统:

- 为ADC/DAC提供低抖动时钟

- 多通道时钟同步

- 通信设备:

- 基站时钟分配

- 光纤通信时钟缓冲

- 汽车电子:

- 车载信息娱乐系统

- 高级驾驶辅助系统(ADAS)

- 测试测量设备:

- 仪器时钟分配

- 多设备时钟同步

六、设计建议

- 电源设计:

- 使用低噪声LDO供电

- 增加适当去耦电容

- 注意电源序列要求

- 信号完整性:

- 保持50Ω阻抗匹配

- 最小化传输线长度

- 避免锐利拐角

- 热管理:

- 确保充分散热

- 监控工作温度

- 避免长时间满负荷工作

- EMI考虑:

- 适当屏蔽

- 滤波设计

- 良好的接地实践

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

CDCLVP1216:高性能时钟缓冲器的技术解析与应用指南2026-02-09 267

-

低附加抖动LVDS缓冲器LMK1D120x的技术解析与应用指南2026-02-08 314

-

低抖动高性能之选:LMK1D210xL LVDS时钟缓冲器深度解析2026-02-06 300

-

低附加抖动LVDS缓冲器LMK1D210x技术解析与应用指南2025-09-23 1013

-

LMK1D2106/LMK1D2108 LVDS时钟缓冲器技术解析与应用指南2025-09-18 964

-

德州仪器LMK1D1212EVM缓冲器评估模块技术解析2025-09-17 993

-

LMK1D1216EVM用户指南2024-11-26 465

全部0条评论

快来发表一下你的评论吧 !