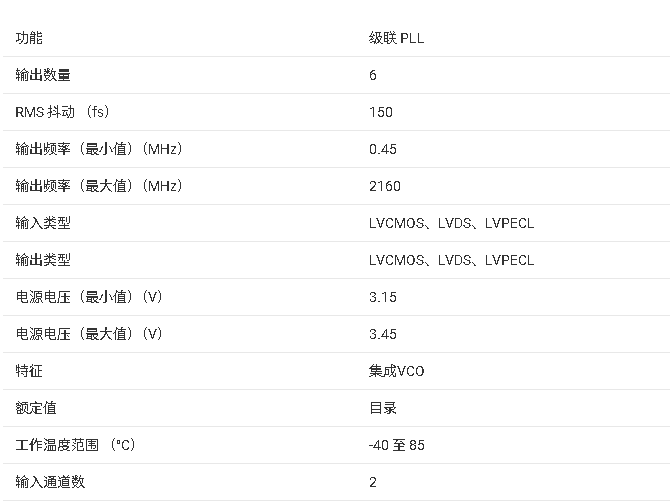

LMK04033 低噪声抖动清除器技术手册

描述

LMK04000系列精密时钟调理器提供低噪声抖动清除、时钟倍增和分配,无需高性能压控晶体振荡器 (VCXO) 模块。LMK04000 系列采用级联 PLLatinum 架构,结合外部晶体和变容二极管,提供低于 200 飞秒 (fs) 的均方根 (RMS) 抖动性能。

*附件:lmk04033.pdf

级联架构由两个高性能锁相环 (PLL)、一个低噪声晶体振荡器电路和一个高性能压控振荡器 (VCO) 组成。第一个PLL (PLL1)提供低噪声抖动清除器功能,而第二个PLL (PLL2)执行时钟生成。PLL1 可以配置为与外部 VCXO 模块配合使用,也可以使用带有外部晶体和变容二极管的集成晶体振荡器。当与非常窄的环路带宽一起使用时,PLL1 使用 VCXO 模块或晶体的卓越近相位噪声(偏移低于 50 kHz)来清洁输入时钟。PLL1的输出用作PLL2的干净输入基准电压源,锁定集成VCO。PLL2的环路带宽可以优化,以清除远相位噪声(偏移量高于50 kHz),其中集成VCO的性能优于PLL1中使用的VCXO模块或晶体。

LMK04000系列具有双冗余输入、五个差分输出和可选的上电默认时钟。输入模块配备了信号丢失检测和参考时钟的自动或手动选择。每个时钟输出由一个可编程分频器、一个相位同步电路、一个可编程延迟和一个LVDS、LVPECL或LVCMOS输出缓冲器组成。CLKout2 上提供默认启动时钟,可用于为现场可编程门阵列 (FPGA) 或微控制器提供初始时钟,在系统上电过程中对抖动清除器进行编程。

特性

- 级联 PLLatinum PLL 架构

- PLL1

- 相位检测器速率高达 40 MHz

- 集成低噪声晶体振荡器电路

- 带LOS的双冗余输入参考时钟

- PLL2

- 归一化 [1 Hz] PLL 本底噪声为 -224 dBc/Hz

- 鉴相器速率高达 100 MHz

- 输入倍频器

- 集成低噪声VCO

- 超低RMS抖动性能

- 150 fs RMS 抖动 (12 kHz – 20 MHz)

- 200 fs RMS 抖动 (100 Hz – 20 MHz)

- LVPECL/2VPECL、LVDS和LVCMOS输出

- 支持高达 1080 MHz 的时钟速率

- 上电时默认时钟输出 (CLKout2)

- 五个专用通道分频器和延迟模块

- 引脚兼容系列时钟设备

- 工业温度范围:-40 至 85 °C

- 3.15 V 至 3.45 V 工作电压

- 封装:48 引脚 LLP (7.0 x 7.0 x 0.8 mm)

参数

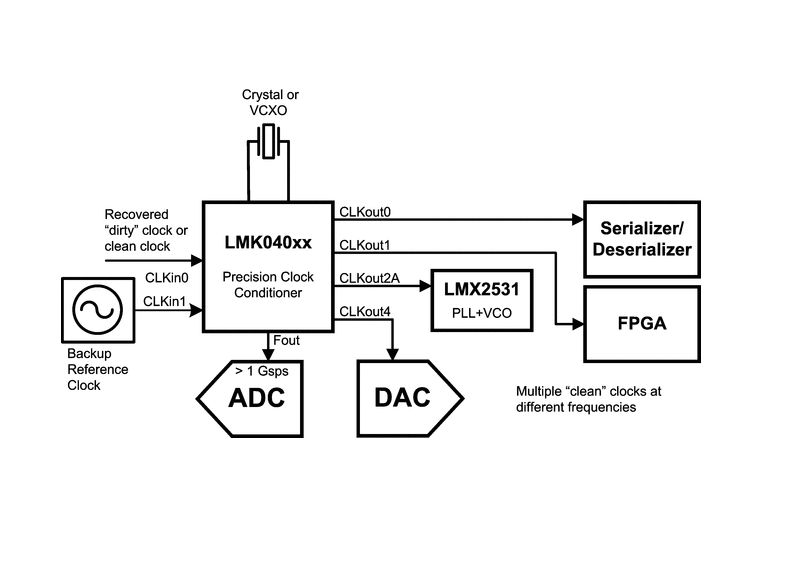

方框图

1. 产品概述

LMK04000系列是德州仪器(TI)推出的精密时钟调理器家族,包含LMK04000/01/02/10/11/31/33等型号。该系列采用级联PLLatinum™架构,集成低噪声晶体振荡电路和电压控制振荡器(VCO),提供超低RMS抖动性能(150 fs @12kHz-20MHz),支持LVPECL/2VPECL/LVDS/LVCMOS输出,适用于数据转换器时钟、无线基础设施、医疗、军事等高频低噪声应用场景。

2. 核心特性

- 双级PLL架构

- PLL1:最高40MHz相位检测率,支持外部VCXO或晶体振荡器,冗余输入参考时钟(CLKin0/1)带丢失信号检测(LOS)。

- PLL2:224 dBc/Hz归一化噪声基底,100MHz相位检测率,集成低噪声VCO,支持频率倍增模式。

- 性能指标

- 支持1080MHz时钟输出,默认上电时钟(CLKout2)可配置。

- 5个独立可编程分频/延时通道,支持皮秒级延迟调整(0-2250ps,步进150ps)。

- 封装与工作条件

- 48引脚WQFN封装(7x7x0.8mm),工业级温度范围(-40°C至85°C),3.15-3.45V供电。

3. 功能模块详解

- 时钟分配系统

- 每个输出通道含分频器(2-510偶数分频)、同步电路、可编程延迟和输出缓冲器。

- 支持全局输出同步(SYNC*引脚)和使能控制(GOE引脚)。

- 集成VCO

- 覆盖1185-2160MHz频段,分频输出支持2-8分频,Fout引脚提供原始VCO输出。

- 编程接口

- 通过Microwire串行接口(CLKuWire/DATAuWire/LEuWire)配置32位寄存器,需严格遵循上电初始化序列。

4. 典型应用设计

- 环路滤波器设计

- PLL1采用窄带宽(10-200Hz)滤除参考时钟噪声,PLL2带宽50-200kHz优化VCO相位噪声。

- 内置可编程3/4阶环路滤波器组件(R3/R4/C3/C4)。

- 晶体振荡器方案

- OSCin端口支持外部晶体+变容二极管实现VCXO,提供参考设计电路(如12.288MHz晶体+SMV1249-074变容二极管)。

- 输出端接方案

- 提供LVDS/LVPECL/LVCMOS的AC/DC耦合端接指南,包括差分/单端配置及终端电阻选择。

5. 性能优化建议

- 优先选用低相位噪声VCXO(如Wenzel XO)以改善输出抖动。

- 高频输出(>1GHz)时,延迟配置需小于半个周期(0.5/FCLKoutX)。

- 热管理需通过PCB散热焊盘+过孔设计控制结温≤125°C。

6. 文档结构

- 包含电气特性表、寄存器映射(R0-R15)、时序图、封装热阻数据及典型性能曲线,提供完整的参数化设计支持。

-

深度剖析LMK0480x:低噪声时钟抖动清除器的卓越性能与应用实践2026-02-09 342

-

解读LMK04832 - SP:空间级超低噪声时钟抖动清除器的卓越性能与应用2026-02-08 393

-

LMK04011 低噪声时钟抖动清除器技术文档总结2025-09-18 975

-

LMK04001 低噪声抖动清除器技术手册2025-09-17 957

-

具有双环路PLL的LMK04228超低噪声且符合JESD204B标准的时钟抖动清除器数据表2024-08-21 498

-

LMK04832-SP符合JESD204B标准的航天级、超低噪声、双环路时钟抖动清除器数据表2024-08-20 570

全部0条评论

快来发表一下你的评论吧 !