LMK01010 1.6 GHz 高性能时钟缓冲器、分频器和分配器技术手册

描述

LMK01000系列提供了一种在整个系统中划分和分配高性能时钟信号的简单方法。这些器件提供一流的噪声性能,并设计为引脚对引脚和封装与 LMK03000/LMK02000 系列精密时钟调理器兼容。

LMK01000 系列具有两个可编程时钟输入(CLKin0 和 CLKin1),允许用户在不同的时钟域之间动态切换。

*附件:lmk01010.pdf

每个器件具有 8 个时钟输出,具有独立可编程的分频器和延迟调整。器件的输出可以通过外部引脚 (SYNC*) 轻松同步。

特性

- 30 fs 附加抖动(100 Hz 至 20 MHz)

- 双时钟输入

- 可编程输出通道(0 至 1600 MHz)

- 外部同步

- 引脚兼容系列时钟设备

- 3.15 至 3.45 V 工作电压

- 封装:48 引脚 LLP (7.0 x 7.0 x 0.8 mm)

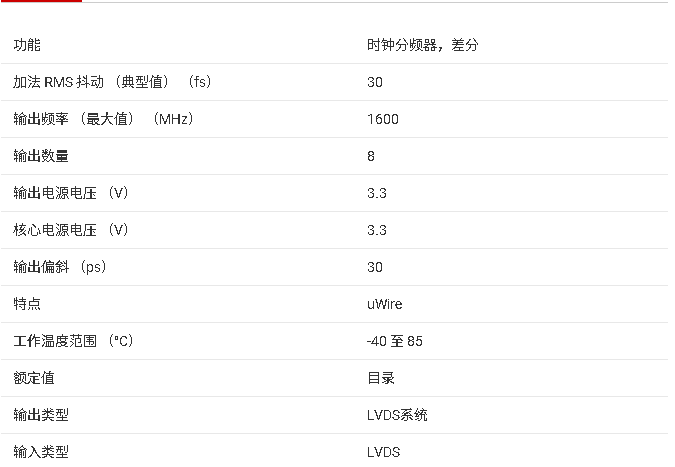

参数

方框图

1. 产品概述

LMK01000系列是德州仪器(TI)推出的高性能时钟管理芯片,包含LMK01000/01010/01020三款型号,专为1.6 GHz以下时钟信号的分配、分频和同步设计。主要特点包括:

- 低抖动性能:30 fs(100 Hz至20 MHz带宽)

- 双时钟输入:支持CLKin0和CLKin1动态切换

- 8路可编程输出:每通道独立配置分频(1

510偶数分频)、延迟(02250 ps,步进150 ps)和输出类型(LVDS/LVPECL) - 同步功能:通过SYNC*引脚实现多通道相位对齐

- 工作电压:3.15~3.45 V,48引脚LLP封装(7×7×0.8 mm)

2. 关键应用领域

- 无线基础设施

- 医疗成像设备

- 有线通信系统

- 测试测量仪器

- 军事/航空航天电子

3. 功能模块详解

- 输入端口:CLKin0/CLKin1需AC耦合,支持差分或单端输入(互补端需AC接地)。

- 输出配置:

- LVDS:默认100 Ω差分终端,支持AC/DC耦合

- LVPECL:需50 Ω终端至Vcc-2 V,内置120 Ω发射极电阻

- 延迟与分频:

- 分频路径固定延迟100 ps,延迟模块固定400 ps

- 分频值=2×编程值(如0x01对应分频2)

- 同步机制:SYNC*低电平触发同步,需保持>1个输入时钟周期。

4. 寄存器编程

- 核心寄存器:R0~R7分别控制8路输出的MUX模式、使能、分频和延迟。

- 全局控制:R14配置电源模式(POWERDOWN)和全局输出使能(EN_CLKout_Global)。

- 编程流程:需先通过R0复位(RESET=1),再配置各通道参数,最后写入R14。

5. 电气特性

- 功耗:

- 全输出使能时,LMK01000典型电流271 mA(LVPECL输出占主要功耗)。

- LVDS单通道功耗17.8 mA,LVPECL单通道40 mA(含发射极电阻)。

- 抖动性能:

- LVDS输出:30 fs(200 MHz)至25 fs(1.6 GHz)

- LVPECL输出:25 fs(200 MHz)至25 fs(1.6 GHz)

6. 热管理与布局建议

- 散热设计:裸露焊盘(DAP)需焊接至PCB地平面,建议使用16个热过孔连接至内层铜箔。

- 热阻参数:θJA=27.4°C/W(4层板设计)。

7. 封装与订购信息

- 封装型号:48引脚WQFN(RHS),符合RoHS标准。

- 工作温度:-40°C至85°C。

8. 设计注意事项

- 终端匹配:LVDS需100 Ω差分终端,LVPECL需50 Ω终端至Vcc-2 V。

- 电源去耦:Bias引脚(Pin 36)需接1 μF低泄漏电容。

- ESD防护:存储时需短路引脚或使用导电泡沫。

该系列器件通过灵活的配置和优异的性能,适用于高精度时钟分配系统,其引脚兼容性(如LMK03000/02000系列)简化了升级设计。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

HMC7043:高性能时钟分配器的技术解析与应用指南2026-03-26 562

-

解析CDCL1810:高性能时钟分配器的技术剖析与应用指南2026-02-10 501

-

深入解析LMK00301:高性能时钟缓冲器的技术探秘2026-02-09 343

-

LMK1D120x低附加抖动LVDS缓冲器:高性能时钟分配的理想选择2026-02-08 358

-

LMK1D1208I:高性能LVDS时钟缓冲器的深度剖析与应用指南2026-02-06 1206

-

LMK01020 1.6 GHz 高性能时钟缓冲器、分频器和分配器技术手册2025-09-18 838

-

CDCLVD1213 1:4低附加抖动LVDS缓冲器带分频器 技术文档摘要2025-09-16 1000

-

LMK01000高性能时钟缓冲器、分频器和分配器数据表2024-08-21 530

-

AD9515 1.6 GHz时钟分配IC,分频器,延迟调整,双输出数据表2021-06-16 863

-

AD9515:1.6 GHz时钟分配IC、分频器、延迟调整、双输出数据表2021-04-13 850

-

AD9512:1.2 GHz时钟分配IC,1.6 GHz输入,分频器,延迟调整,五输出数据表2021-03-22 937

-

AD9508:1.65 GHz时钟扇出缓冲器,集成输出分频器和延迟调整2021-03-21 1067

全部0条评论

快来发表一下你的评论吧 !