高精度、高性能运算放大器TLV936x系列技术解析

描述

Texas Instruments TLV936x/TLV936x-Q1 40V通用运算放大器具有强大的直流和交流规格参数。这些器件还具有轨至轨输出、低失调(±400µV,典型值)、低失调漂移(±1.25µV/°C,典型值)和10.6MHz带宽。EMIRR滤波、高输出电流 (±60mA) 和高压摆率 (25V/µs) 等特性使TLV936x/TLV936x-Q1成为适合高电压、成本敏感型应用的一款强劲的运算放大器。TLV936x/TLV936x-Q1采用标准封装,标定的温度范围为 –40°C至+125°C。Texas Instruments TLV9361/TLV6361-Q1是单运算放大器,TLV9362/TLV9362-Q1是双运算放大器,TLV9364是四运算放大器。TLV936x-Q1器件通过了汽车应用类AEC-Q100认证。

数据手册:

特性

- 低失调电压:±400µV

- 低失调电压漂移:±1.25µV/°C L

- 低噪声(1kHz时为8.5nV/Hz 、6nV/√Hz宽带)

- 高共模抑制:110dB

- 低偏置电流:±10pA

- 轨到轨输出

- 宽带宽(10.6MHz GBW,单位增益稳定)

- 高压摆率 (25V/µs)

- 低静态电流:每个放大器 2.6mA

- 宽电源范围(±2.25V至±20V、4.5V至40V)

- 强大的EMIRR性能

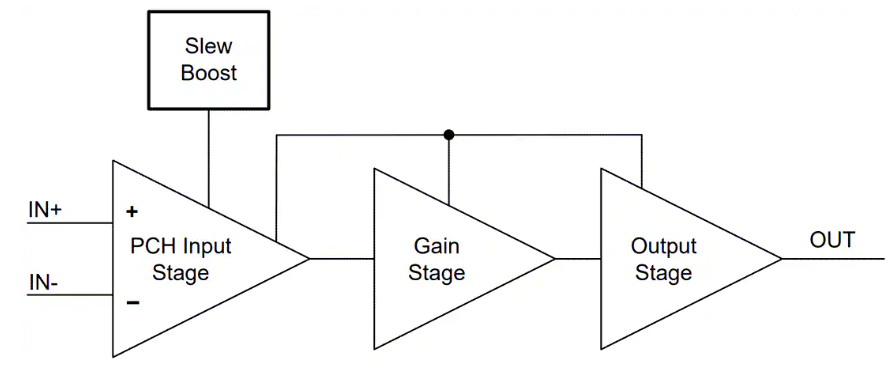

功能框图

高精度、高性能运算放大器TLV936x系列技术解析

一、TLV936x系列概述

TLV936x系列(包括TLV9361单通道、TLV9362双通道和TLV9364四通道)是德州仪器(TI)推出的40V成本优化型运算放大器,专为高电压、成本敏感型应用设计。该系列器件在4.5V至40V(±2.25V至±20V)的宽电源电压范围内工作,具有出色的DC精度和AC性能表现。

关键特性亮点:

- 精密DC性能:低偏移电压(±400μV典型值)和超低偏移电压漂移(±1.25μV/°C典型值)

- 宽带宽:10.6MHz增益带宽积,25V/µs高摆率

- 轨到轨输出:最大化动态范围

- 低噪声:8.5nV/√Hz @1kHz

- 高共模抑制比:110dB(典型值)

- 低静态电流:仅2.6mA/放大器

- 强化EMI抗扰度:集成EMI滤波功能

二、关键性能参数分析

1. 直流特性

- 输入偏移电压:在-40°C至125°C全温度范围内最大仅±1.7mV

- 输入偏置电流:极低的±10pA(典型值),适合高阻抗传感器接口

- 电源抑制比(PSRR) :±1.5μV/V(典型值),有效抑制电源噪声

- 开环增益:130dB(VS=40V时),确保高精度信号处理

2. 交流特性

- 建立时间:0.3μs达到0.1%精度(VS=40V,2V阶跃)

- THD+N性能:在1kHz下仅0.0001%(VS=40V,RL=10kΩ)

- 电容负载驱动:通过添加隔离电阻可稳定驱动高达560pF容性负载

- 过载恢复时间:约170ns,快速从饱和状态恢复

3. 电源特性

- 工作电压范围:单电源4.5V至40V或双电源±2.25V至±20V

- 静态电流:仅2.6mA/放大器(典型值),适合功耗敏感应用

- UVLO保护:当VDD低于3.8V(典型值)时保持输出低电平

三、独特设计特性

1. EMI抗扰设计

TLV936x集成了EMI滤波功能,实测在400MHz至5GHz频段表现出色:

- 400MHz:50dB抑制

- 1.8GHz:65.6dB抑制

- 2.4GHz:70dB抑制

这种特性使其能有效抵抗无线通信和密集数字电路带来的干扰。

2. 热保护机制

当结温超过170°C时,器件会自动关闭输出驱动。以TLV9362为例,在55°C环境温度下,若功耗达到0.954W(如一个通道驱动30mA负载),结温将达到180°C触发保护,输出进入高阻状态直到温度恢复正常。

3. 容性负载驱动优化

通过外接隔离电阻(RISO)可显著改善稳定性:

- 无RISO时:20mV阶跃下对560pF负载可能产生60%过冲

- 添加50Ω RISO后:过冲可降至约10%,相位裕度提升至45°

四、典型应用电路

1. 带RISO补偿的unity-gain缓冲器

设计要点:

- 选择RISO使开环增益(AOL)与1/β曲线的闭合速率为20dB/十倍频

- 对于CL=100pF,推荐RISO≈50Ω可获得45°相位裕度

- 传递函数:T(s) = (1 + CLOAD × RISO × s) / (1 + (Ro + RISO) × CLOAD × s)

2. 高侧电流检测电路

利用TLV936x的宽共模范围(V-到V+-2V),可直接测量高侧电流而无需专用电流检测放大器,典型误差<1%。

五、PCB布局建议

- 电源去耦:每个电源引脚就近放置0.1μF陶瓷电容,建议同时并联≥1μF电容

- 地平面设计:采用独立模拟地平面,单点连接数字地

- 信号走线:

- 输入走线尽量短,远离电源和输出线

- 必要时采用保护环减少漏电流

- 热管理:对于高功耗应用,充分利用接地焊盘和铜箔散热

六、选型指南

| 型号 | 通道数 | 封装选项 | 特点 |

|---|---|---|---|

| TLV9361 | 1 | SOT-23(5),SC70(5) | 最小封装,空间受限应用 |

| TLV9362 | 2 | SOIC(8),VSSOP(8) | 平衡性能与尺寸 |

| TLV9364 | 4 | SOIC(14),TSSOP(14) | 高密度设计 |

-

OPAx317系列运算放大器:高精度与低功耗的完美结合2026-05-14 372

-

德州仪器TLV262x系列单电源运算放大器:高性能与低功耗的完美结合2026-04-23 222

-

TLV916x系列16V轨到轨运算放大器技术解析与应用指南2025-09-18 1174

-

TLV9361 单路、40V、10.6MHz轨到轨输出运算放大器技术手册2025-04-01 1304

-

TLV9364 四路、40V、10.6MHz、轨到轨输出运算放大器技术手册2025-03-31 1347

-

TLV2361/TLV2362高性能低压运算放大器数据表2024-06-06 470

-

适用于成本敏感型系统的TLV936x 10MHz、40V、RRO运算放大器数据表2024-06-04 584

-

如何使用运算放大器来驱动高精度ADC?2021-04-14 2270

-

高精度、低噪声的opax2x系列运算放大器介绍2020-09-25 3298

-

转向特定应用的运算放大器2018-10-22 2263

-

高精度运算放大器,高精度运算放大器是什么意思2010-03-09 7217

-

高性能运算放大器2009-03-20 724

全部0条评论

快来发表一下你的评论吧 !