CDCE925 可编程 2-PLL VCXO 时钟合成器技术手册

描述

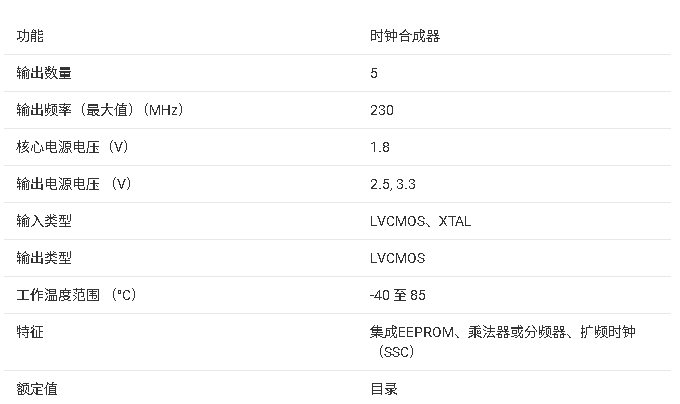

CDCE925和CDCEL925是基于模块化PLL的低成本、高性能、可编程时钟合成器、乘法器和分频器。CDCE925和CDCEL925从单个输入频率生成多达五个输出时钟。每个输出都可以在系统内编程,以达到230MHz的任何时钟频率,使用多达两个独立的可配置PLL。

CDCEx925 有一个单独的输出电源引脚 VDDOUT,CDCEL925为 1.8V,CDCE925为 2.5V 至 3.3V。

*附件:cdce925.pdf

输入接受外部晶体或LVCMOS时钟信号。在晶体输入的情况下,片内负载电容器足以满足大多数应用。负载电容器的值可在 0 至 20pF 范围内进行编程。此外,片上VCXO是可选的,允许将输出频率与外部控制信号(即PWM信号)同步。

例如,较深的M/N分频比允许从27MHz基准输入频率生成零ppm音频/视频、网络(WLAN、蓝牙、以太网、GPS)或接口(USB、IEEE1394、记忆棒)时钟。

所有 PLL 都支持 SSC(扩频时钟)。SSC 可以是中心扩展或下扩展时钟,这是减少电磁干扰 (EMI) 的常用技术。

根据PLL频率和分频器设置,自动调整内部环路滤波器组件,以实现每个PLL的高稳定性和优化的抖动传输特性。

该器件支持非易失性EEPROM编程,以便在应用中轻松定制器件。它预设为出厂默认配置,可以在进入PCB之前重新编程为不同的应用配置,或通过系统内编程重新编程。所有器件设置都可通过SDA/SCL总线(2线串行接口)进行编程。

三个自由可编程控制输入S0、S1和S2可用于选择不同的频率,或更改SSC设置以降低EMI,或其他控制功能,如输出禁用至低电平、输出处于高阻抗状态、断电、PLL旁路等。

CDCx925 在 1.8V 环境中工作,温度范围为 –40°C 至 85°C。

特性

- 可编程时钟发生器系列成员

- CDCEx913:1PLL,3 个输出

- CDCEx925:2PLL,5 个输出

- CDCEx925:3PLL,7 个输出

- CDCEx949:4PLL,9 个输出

- 系统内可编程性和EEPROM

- 串行可编程易失性寄存器

- 用于存储客户设置的非易失性EEPROM

- 灵活的输入时钟概念

- 外部晶体:8MHz至32MHz

- 片上VCXO:拉动范围±150ppm

- 单端LVCMOS,频率高达160MHz

- 自由选择高达 230MHz 的输出频率

- 低噪声PLL内核

- 集成 PLL 回路滤波器组件

- 低周期抖动(典型值 60ps)

- 独立的输出电源引脚

- CDCE925:3.3V 和 2.5V

- CDCEL925:1.8V

- 灵活的时钟驱动器

- 三个用户可定义的控制输入 [S0/S1/S2],例如 SSC 选择、频率切换、输出使能或断电

- 为视频、音频、USB、IEEE1394、RFID、蓝牙、WLAN、以太网™和 GPS 生成高精度时钟

- 生成与 TI DaVinci™、OMAP™ 和 DSP 一起使用的通用时钟频率

- 可编程 SSC 调制

- 实现 0PPM 时钟生成

- 1.8V器件电源

- 宽温度范围:–40°C 至 85°C

- 采用 TSSOP 封装

- 用于轻松进行 PLL 设计和编程的开发和编程套件TI (Pro-Clock™)

参数

1. 产品概述

- 型号:CDCE925(3.3V/2.5V输出)与CDCEL925(1.8V输出),为可编程时钟发生器,支持扩频时钟(SSC)以降低电磁干扰(EMI)。

- 核心特性:

- 2个独立PLL,5路输出,频率范围高达230MHz。

- 支持中心扩频(±0.25%~±2%)和下扩频(-0.25%~-2%)调制。

- 集成EEPROM存储用户配置,支持在线编程(SDA/SCL接口)。

- 低周期抖动(典型值60ps),适用于视频、音频、USB、以太网等应用。

2. 关键功能

- 输入灵活性:支持外部晶体(8MHz~32MHz)、LVCMOS时钟(≤160MHz)或VCXO控制(±150ppm调节范围)。

- 输出配置:每路输出可独立编程分频比(Pdiv1~5),支持高阻态、低电平或使能状态切换。

- 控制接口:3个可编程引脚(S0/S1/S2)实现频率切换、SSC模式选择或电源管理。

3. 应用场景

- 典型应用:数字电视(D-TV)、机顶盒(STB)、DVD播放器/录像机、打印机、WiFi/蓝牙模块、FPGA时钟生成。

- EMI优化:通过SSC技术降低时钟谐波辐射,满足视频(如74.25MHz)、USB(48MHz)等接口需求。

4. 电气特性

- 电源要求:VDD=1.8V,VDDOUT分1.8V(CDCEL925)或2.5V~3.3V(CDCE925)。

- 功耗:典型值20mA(全输出使能),待机电流1μA。

- 温度范围:-40°C至85°C。

5. 封装与开发支持

- 封装:16引脚TSSOP(5.0mm×4.4mm)。

- 开发工具:TI Pro-Clock™软件简化PLL配置与编程。

6. 设计注意事项

- 布局建议:晶体需靠近芯片,避免底层走线;电源引脚需就近放置去耦电容。

- 未使用引脚处理:VCtrl悬空,其他输入接地,禁用未用输出。

7. 文档结构

- 包含特性、引脚定义、寄存器映射、应用电路及热性能数据,完整覆盖硬件设计到软件配置。

-

CDCE906:高性能可编程时钟合成器的深度解析2026-02-10 304

-

CDCE937-Q1 和 CDCEL937-Q1:可编程 3-PLL VCXO 时钟合成器的技术解析2026-02-09 391

-

CDCEL824可编程2 - PLL时钟合成器:设计与应用指南2026-02-08 1150

-

CDCE937 可编程 3-PLL VCXO 时钟合成器技术手册2025-09-18 964

-

CDCE949-Q1 可编程时钟合成器技术文档总结2025-09-17 797

-

CDCE813-Q1可编程1-PLL时钟合成器和抖动消除器数据表2024-08-23 416

-

CDCE706可编程3-PLL时钟合成器/乘法器/分频器数据表2024-08-22 470

-

CDCE925 具有 2.5V 或 3.3V LVCMOS 输出的可编程 2-PLL VCXO 时钟合成器2019-04-18 875

-

时钟芯片_cdce925数据手册2016-01-25 790

全部0条评论

快来发表一下你的评论吧 !