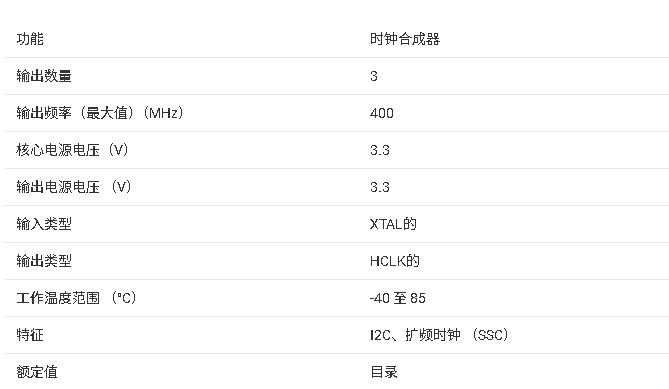

CDCDLP223 时钟合成器技术文档总结

描述

CDCDLP223是一款基于PLL的高性能时钟合成器,针对DLP™系统进行了优化。它使用20 MHz晶体生成基频,并导出100 MHz HCLK和300 MHz HCLK输出的频率。此外,该CDCDLP223在20 MHz输出端生成20 MHz晶体振荡器频率的缓冲副本。

100 MHz HCLK输出为XDR时钟发生器(CDCD5704)提供参考时钟。默认配置中应用了下扩频 0.5% 的扩频时钟,可减少电磁干扰 (EMI)。扩频时钟 (SSC) 通过串行控制接口打开和关闭。

*附件:cdcdlp223.pdf

300 MHz HCLK输出为DLP™控制ASIC的DMD控制逻辑提供200-400 MHz时钟信号。可以通过串行控制接口以 20 MHz 为步长进行频率选择。应用中心扩频±1.0%或±1.5%的扩频时钟,可通过串行控制接口禁用

该CDCDLP223具有故障安全启动电路,只有在施加足够的电源电压并且晶体振荡器提供稳定振荡时,该电路才能启用 PLL。在晶体启动时间和PLL稳定时间之后,所有输出都可以使用。

该CDCDLP223采用3.3 V单电源供电,工作温度范围为-40°C至85°C。

特性

- 高性能时钟合成器

- 使用 20 MHz 晶体输入产生多个输出频率

- 用于 20 MHz 振荡器的集成负载电容,降低系统成本

- 所有 PLL 环路滤波器组件均集成

- 生成以下时钟:

- REF CLK 20 MHz(缓冲)

- XCG CLK 100 MHz 带 SSC

- DMD CLK 200-400 MHz,带可选 SSC

- 极低周期抖动特性:

- 20 MHz输出时±100 ps

- 100 MHz 和 200-400 MHz 输出时为 ±75 ps

- 包括扩频时钟 (SSC),100 MHz 的下扩频和 200-400 MHz 的中心扩频

- HCLK 差分输出,用于 100 MHz 和 200-400 MHz 时钟

- 采用3.3V单电源供电

- TSSOP20包装

- 工业温度范围 -40°C 至 85°C 的表征

- ESD保护超过JESD22

- 2000-V 人体模型 (A114-C) - MIL-STD-883,方法 3015

- 典型应用

- 用于 DLP™ 系统的中央时钟发生器

参数

1. 产品概述

CDCDLP223是德州仪器(TI)推出的高性能PLL时钟合成器,专为DLP™投影系统设计。该器件采用20MHz晶体输入,可生成多种输出频率,并集成振荡器负载电容以降低系统成本。主要特性包括:

- 单3.3V供电,工业级温度范围(-40°C至85°C)

- 集成PLL环路滤波器组件

- 支持扩频时钟(SSC)技术以降低EMI

- TSSOP20封装,符合ESD防护标准(2000V人体模型)

2. 关键功能

- 输出时钟:

- 20MHz REF CLK(缓冲输出)

- 100MHz XCG CLK(带0.5%下扩频SSC)

- 200-400MHz DMD CLK(可编程步进20MHz,支持±1.0%/±1.5%中心扩频SSC)

- 性能参数:

- 极低周期抖动:±100ps(20MHz)、±75ps(100/200-400MHz)

- 差分HCLK输出(100MHz和200-400MHz)

3. 控制接口

- 2线串行接口(兼容I2C/SMBus):

- 支持标准模式(100kHz)和快速模式(400kHz)

- 可编程频率选择、SSC启停及输出配置

- 硬件使能引脚(EN)直接控制所有输出启停

4. 典型应用

- DLP™系统的核心时钟发生器

- 为XDR时钟分配芯片(CDCD5704)提供参考时钟

- 驱动DLP™控制ASIC的DMD逻辑模块

5. 其他信息

- 内置安全启动电路,确保电源稳定后输出有效时钟

- 提供完整的热阻参数(θJA=83°C/W)和绝对最大额定值

- 配套20MHz晶体规格要求:ESR≤100Ω,负载电容20pF

- 生产数据截至2025年9月,符合TI标准保修条款

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

TI CDCDLP223:DLP™ 系统的高性能时钟合成器2026-02-10 479

-

探索RC22312/RC22308:低相位噪声时钟合成器的卓越之选2025-12-29 621

-

CDCEL824 可编程双PLL时钟合成器技术文档总结2025-09-14 1169

-

敏捷合成器的技术原理和应用场景2025-02-20 775

-

CDCDLP223高性能时钟频率合成器数据表2024-08-22 361

-

时钟合成器和时钟发生器的区别2023-11-09 1902

-

锁相环频率合成器是什么原理?2021-04-22 2649

-

什么是频率合成器2019-08-19 5767

-

如何利用FPGA设计PLL频率合成器?2019-07-30 4559

-

用于仪表的500MHz时钟合成器评估板AD9911 PCB2019-07-10 1832

-

基于DDS的频率合成器设计介绍2019-07-08 3033

-

能有效降低高速网络误码率的超低抖动时钟合成器2018-10-31 4864

-

合成器2017-12-06 3602

-

频率合成器,频率合成器原理及作用是什么?2010-03-23 15337

全部0条评论

快来发表一下你的评论吧 !