CDCL1810高性能时钟分配器技术文档总结

描述

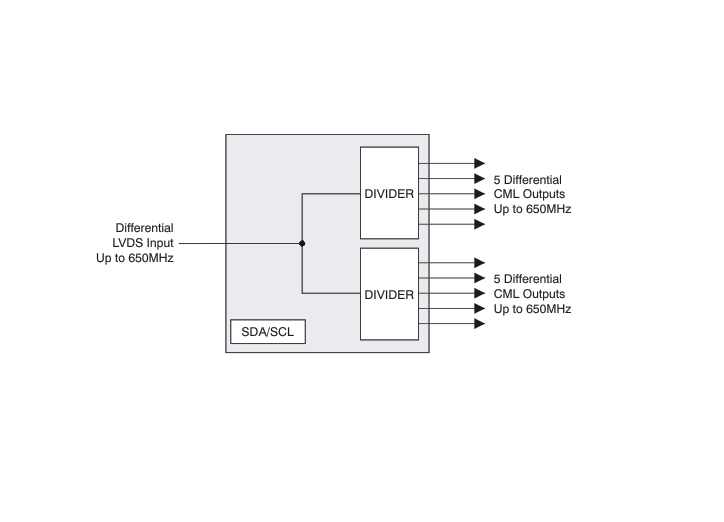

CDCL1810 是一款高性能时钟分配器。可编程分频器 P0 和 P1,对输出频率与输入频率的比值具有很高的灵活性: F 外 = F 在 /P,其中:P (P0,P1) = 1, 2, 4, 5, 8, 10, 16, 20, 32, 40, 80.

该CDCL1810支持一个差分LVDS时钟输入和总共10个差分 CML 输出。如果 CML 输出是交流耦合的,则与 LVDS 接收器兼容。

*附件:cdcl1810.pdf

通过仔细观察输入电压摆幅和共模电压限制,该 CDCL1810可以支持单端时钟输入,如引脚配置和功能中所述。

所有器件设置均可通过SDA/SCL串行双线接口进行编程。 串行接口仅容限为 1.8V。

一个输出组相对于另一个输出组的相位可以通过 SDA/SCL 进行调整 接口。对于 5 的倍数的分频后比 (P0、P1),相位总数 调整步骤 (η) 等于除以 5。为 后除比(P0、P1)不是5的倍数,则总步数(η)与后除比相同。相位调整步长 (ΔΦ) 时间单位为: ΔΦ = 1/(n × F 外 ),其中 F外是相应的输出频率。

该器件在 1.8V 电源环境中工作,其特性是工作温度范围为 –40°C 至 +85°C。 该CDCL1810采用 48 引脚 VQFN (RGZ) 封装。

特性

- 1.8V 单电源

- 具有 10 个输出的

高性能时钟分配器 - 低输入输出附加抖动:

低至 10fs RMS - 输出组相位调整

- 低压差分信号 (LVDS)

输入,100 Ω差分片上

终端,频率高达 650 MHz - 差分电流模式逻辑 (CML)

输出,50 Ω单端片上

端接,频率高达 650 MHz - 两组,每组五个输出,每个

输出具有独立的频分比 - 输出频率以 1、2、4、5、8、10、16、20、

32、40 和 80 的分压

比导出 - 符合 ANSI TIA/EIA-644-A-2001 LVDS

标准要求 - 功耗:410 mW(典型值)

- 每个输出

的输出使能控制和自动输出同步 - SDA/SCL 设备管理接口

- 48引脚VQFN (RGZ)封装

- 工业温度范围:

–40°C 至 +85°C

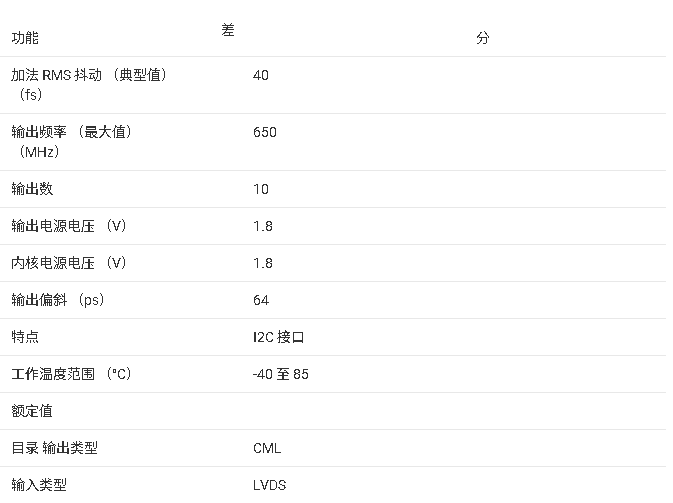

参数

方框图

1. 核心功能

CDCL1810是德州仪器(TI)推出的1.8V供电、10路输出的高性能时钟分配器,主要特点包括:

- 低抖动性能:输入至输出附加抖动低至10fs RMS。

- 灵活分频:支持11种分频比(1/2/4/5/8/10/16/20/32/40/80),输出频率公式为FOUT = FIN/P。

- 相位调整:两组输出(每组5路)支持独立相位调整,步长ΔΦ=1/(n×FOUT)。

- 接口兼容性:

- 输入:LVDS(带100Ω片上终端,支持650MHz)。

- 输出:CML(兼容LVDS接收器,需AC耦合)。

2. 关键参数

- 电气特性:

- 工作电压:1.7V–1.9V(模拟/数字电源)。

- 功耗:典型值410mW(全输出启用)。

- 温度范围:-40°C至+85°C。

- 时序性能:

- 输出偏移(Skew):64ps(30.72MHz下)。

- 上升/下降时间:20%-80%范围≤280ps。

3. 应用场景

- 高速串行接口(SERDES)时钟分配。

- 1G/10G以太网、PCIe、SATA、SONET等协议的参考时钟分发。

- 多DSP系统的时钟同步(如TI Keystone系列)。

4. 编程与控制

- SDA/SCL接口:支持400kbps I²C协议,通过7位地址(11010XX)配置分频比、相位及输出使能。

- 寄存器映射:6个字节控制输出分组、分频比、相位及电源模式。

5. 封装与布局

- 封装:48引脚VQFN(7mm×7mm),需将散热焊盘接地以优化性能。

- 布局建议:

- 缩短电源去耦电容路径,优先使用0201封装电容。

- 差分信号走线需保持对称,减少串扰。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

HMC7043:高性能时钟分配器的技术解析与应用指南2026-03-26 427

-

深入解析CDCL6010:高性能时钟管理芯片的卓越之选2026-02-10 457

-

深入解析CDCL1810A:高性能时钟分配器的卓越之选2026-02-09 197

-

CDCL1810A 高性能时钟分配器技术文档总结2025-09-14 1241

-

CDCL1810A 1.8V、10 输出高性能时钟分配器数据表2024-08-23 437

-

CDCL1810 1.8V 10路输出高性能时钟分配器数据表2024-08-22 509

-

LMK01000高性能时钟缓冲器、分频器和分配器数据表2024-08-21 487

-

分配器,什么是分配器2010-04-02 4012

-

VGA分配器,VGA分配器是什么意思2010-03-26 2826

全部0条评论

快来发表一下你的评论吧 !