CDCE706 可编程3-PLL时钟合成器/乘法器/分频器技术文档总结

描述

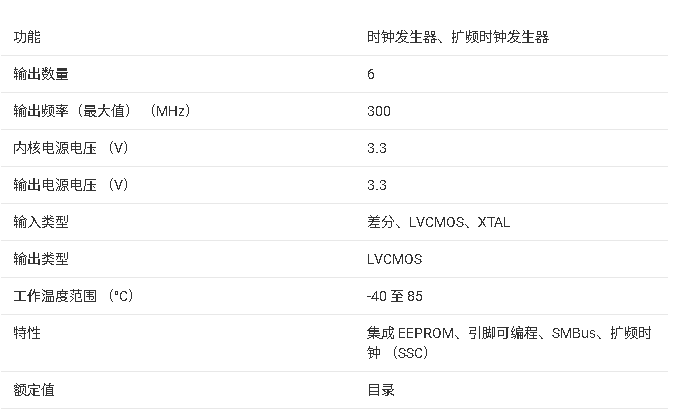

CDCE706是当今最小、功能最强大的PLL合成器/乘法器/分频器之一。尽管它的物理轮廓很小,但CDCE706非常灵活。它能够从给定的输入频率产生几乎独立的输出频率。

输入频率可以来自LVCMOS、差分输入时钟或单晶。可以通过SMBus数据接口控制器选择合适的输入波形。

为了实现独立的输出频率,每个PLL的基准分压器M和反馈分压器N可以设置为M分频器的1至511,N分频器的值为1至4095。PLL-VCO(压控振荡器)频率被路由到自由可编程输出开关矩阵,到六个输出中的任何一个。开关矩阵包括一个额外的7位后分频器(1至127)和每个输出的反相逻辑。

*附件:cdce706.pdf

较深的M/N分频比允许从任何基准输入频率(例如,27 MHz)生成零ppm时钟。

该CDCE706包括三个 PLL,其中一个支持 SSC(扩频时钟)。PLL1、PLL2 和 PLL3 设计用于高达 300 MHz 的频率,并针对具有宽分频因子的零 ppm 应用进行了优化。

PLL2还支持中心扩频和下扩频时钟(SSC)。这是减少电磁干扰的常用技术。此外,压摆率可控 (SRC) 输出边沿可最大限度地降低 EMI 噪声。

根据PLL频率和分频器设置,内部环路滤波器组件将自动调整,以实现PLL的高稳定性和优化的抖动传输特性。

该器件支持非易失性EEPROM编程,便于定制应用。它采用出厂默认配置进行预编程(见图 13),可以在进入 PCB 之前重新编程为不同的应用配置,或通过系统内编程重新编程。通过串行 SMBus 接口对不同的设备设置进行编程。

两个自由可编程输入 S0 和 S1 可用于控制每个应用要求最苛刻的逻辑控制设置(输出禁用至低电平、输出 3 态、断电、PLL 旁路等)。

CDCE706有三个电源引脚,V CC , VCCOUT1和 V CCOUT2 .VCC是设备的电源。它采用 3.3V 单电源电压供电。VCCOUT1和 VCCOUT2是输出的电源引脚。VCCOUT1为输出 Y0、Y1 和 V 供电CCOUT2提供输出 Y2、Y3、Y4 和 Y5。两种输出电源的电压均为 2.3 V 至 3.6 V。在输出电压低于3.3 V时,输出驱动电流受到限制。

该CDCE706的特点是在 -40°C 至 85°C 范围内工作。

特性

- 基于高性能 3:6 PLL 的时钟合成器/乘法器/分频器

- 用户可编程PLL频率

- EEPROM编程,无需施加高编程电压

- 通过SMBus数据接口轻松进行在线编程

- 宽 PLL 分压比允许 0 ppm 输出时钟误差

- 时钟输入接受晶体或单端LVCMOS或差分输入信号

- 接受 8 MHz 至 54 MHz 的晶体频率

- 接受高达 200 MHz 的 LVCMOS 或差分输入频率

- 两个可编程控制输入 [S0/S1、A0/A1],用于用户定义的控制信号

- 六个LVCMOS输出,输出频率高达300 MHz

- LVCMOS 输出可针对互补信号进行编程

- 通过可编程输出开关矩阵 [6x6] 自由选择输出频率,包括每个输出的 7 位后分频器

- 集成 PLL 回路滤波器组件

- 低周期抖动(典型值 60 ps)

- 具有用于降低系统 EMI 的扩频时钟 (SSC) 功能

- 可编程输出压摆率控制 (SRC),用于降低系统 EMI

- 3.3V 器件电源

- 工业温度范围 -40°C 至 85°C

- 用于轻松进行 PLL 设计和编程的开发和编程套件 (TI Pro-Clock™)

- 采用 20 引脚 TSSOP 封装

参数

1. 产品概述

CDCE706是德州仪器(TI)推出的高性能3-PLL时钟合成器/乘法器/分频器,具有以下核心特性:

- 灵活编程:支持通过SMBus接口进行电路内编程,无需高压编程电压,内置EEPROM存储配置。

- 多输入支持:兼容晶体(8 MHz至54 MHz)、单端LVCMOS或差分输入信号(最高200 MHz)。

- 输出能力:6路LVCMOS输出(最高300 MHz),可编程为互补信号,支持可调输出摆率控制(SRC)以降低EMI。

- 低抖动性能:典型周期抖动60 ps,支持扩频时钟(SSC)功能进一步降低系统EMI。

- 宽工作范围:3.3 V供电,工业级温度范围(-40°C至85°C),20引脚TSSOP封装。

2. 关键功能模块

- PLL架构:集成3个独立PLL,支持宽分频比(M:1-511,N:1-4095),实现零ppm时钟误差。

- PLL2支持扩频时钟(SSC),可选中心/下扩频模式。

- 输出矩阵:6×6可编程开关矩阵,每路输出含7位后分频器(1-127)和反相逻辑。

- 控制接口:

- 2个可编程控制输入(S0/S1或A0/A1),支持用户自定义功能(如电源管理、输出使能)。

- SMBus接口(兼容I2C)实现寄存器配置,支持字节/块读写操作。

3. 电气特性

- 电源管理:

- 工作电流:典型90 mA(全输出激活时),待机电流50 µA。

- 输出电源独立(VCCOUT1/2:2.3 V至3.6 V),支持低电压驱动。

- 时序性能:

- 输出延迟:3.3 V模式下典型1.7 ns,2.5 V模式下2.2 ns。

- 周期抖动:50 MHz输出时典型60 ps(单PLL)。

4. 应用设计

- 默认配置:出厂预编程为27 MHz晶体输入,6路27 MHz输出(分频比8:1)。

- SMBus配置:提供24字节寄存器映射,控制分频比、PLL选择、输出使能等参数。

- 热管理:θJA热阻66.3°C/W(无气流),需注意功耗限制(TSSOP封装最大600 mW)。

5. 文档结构

- 功能框图:详述PLL、开关矩阵、控制逻辑的互联关系。

- 寄存器说明:包括分频器设置、输出配置、SSC控制等位域定义。

- 时序图与参数表:涵盖SMBus通信协议、抖动特性、绝对最大额定值等。

6. 典型应用场景

适用于需高精度时钟生成的通信设备、嵌入式系统及测试仪器,尤其适合EMI敏感环境。开发工具链包含TI ClockPro软件,简化PLL设计与编程。

注意:具体参数需结合实际配置(如VCO频率模式、分频比)计算,文档提供了详细公式(如输出频率fout = fin × N/(M×P))及示例。

-

深入解析CDCE937-Q1与CDCEL937-Q1可编程时钟合成器2026-05-17 286

-

CDCE706:高性能3 - PLL时钟合成器的深度解析2026-02-10 451

-

CDCE937-Q1 和 CDCEL937-Q1:可编程 3-PLL VCXO 时钟合成器的技术解析2026-02-09 462

-

CDCEL949 具有1.8V LVCMOS输出的可编程4-PLL VCXO时钟合成器技术手册2025-09-18 969

-

CDCE949-Q1 可编程时钟合成器技术文档总结2025-09-17 856

-

CDCEL824 可编程双PLL时钟合成器技术文档总结2025-09-14 1244

-

CDC906可编程3-PLL时钟合成器/乘法器/分频器数据表2024-08-23 488

-

CDCE706可编程3-PLL时钟合成器/乘法器/分频器数据表2024-08-22 506

-

有源乘法器和分频器简化合成器2019-09-29 1573

-

TI发布可定制编程的3-PLL时钟合成器乘法器除法器2009-11-26 879

全部0条评论

快来发表一下你的评论吧 !