CDC5801A低抖动时钟倍频/分频器技术文档总结

描述

CDC5801A器件提供从单端参考时钟 (REFCLK) 到差分输出对 (CLKOUT/CLKOUTB) 的时钟乘法和分频。乘法和分频端子 (MULT/DIV0:1) 提供倍频比和分频比选择,生成 12.5 MHz 至 500 MHz 的 CLKOUT/CLOUTKB 频率,时钟输入基准 (REFCLK) 范围为 19 MHz 至 125 MHz。

实施的相位对齐器通过将需要对齐的时钟馈送到 DLYCTRL 和 LEADLAG 端子,提供了在 CLKOUT/CLKOUTB 和 REFCLK 或系统中的任何其他 CLK 之间进行相位对齐(零延迟)的可能性。

*附件:cdc5801a.pdf

相位对准器还允许用户以 2.6 mUI(单位间隔)的步长延迟或推进 CLKOUT/CLKOUTB。对于DLYCTRL端子上的每个上升沿,只要LEADLAG端子上存在低电平,输出时钟就会延迟2.6 mUI步长。同样,对于DLYCTRL端子上的每个上升沿,只要LEADLAG端子上存在高电平,输出时钟就会提前2.6 mUI步长。该CDC5801A具有故障安全上电初始化状态机,支持在所有上电条件下正常运行。由于REFCLK和CLKOUT/CLKOUTB之间的相位在上电后是随机的,因此应用可以在上电时实现自校准例程,以产生特定的相位起始位置,然后再使用DLYCTRL端子上的时钟对固定延迟进行编程。

根据模式端子 (P0:2) 的选择,该器件充当旁路相位对准器的乘法器(4、6 或 8),或作为具有可编程延迟和相位对准器功能的乘法器或分频器。通过选择端子 (P0:2),用户还可以绕过相位对准器和 PLL(测试模式),直接在 CLKOUT/CLKOUTB 端子上输出 REFCLK。通过 P0:2 端子,输出可以处于高阻抗状态。该器件具有另一个独特的功能,即能够通过改变 V 上的电压来在 REFCLK 端子上的宽电压带下工作DDREF 终端。

该CDC5801A具有故障安全上电初始化状态机,支持在所有上电条件下正常运行。

CDC5801A器件的特点是在 –40°C 至 85°C 的自由空气温度下运行。

特性

- 低抖动时钟乘法器乘以 x4、x6、x8。输入频率范围(19 MHz 至 125 MHz)。支持150 MHz至500 MHz的输出频率

- 故障安全上电初始化

- 低抖动时钟分频器 /2、/3、/4。输入频率范围(50 MHz 至 125 MHz)。支持12.5 MHz至62.5 MHz的输出频率范围

- 2.6 mUI 可编程双向延迟步长

- 500 MHz时典型8 ps相位抖动(12 kHz至20 MHz)

- 500 MHz时典型值为2.1 ps RMS周期抖动(整个频段)

- 一个单端输入和一个差分输出对

- 输出可驱动LVPECL、LVDS和LVTTL

- 三种电源工作模式,可最大限度地降低功耗

- 低功耗(500 MHz 时典型值为 200 mW)

- 采用收缩小外形封装 (DBQ) 封装

- PLL 无需外部元件

- 扩频时钟跟踪能力可降低 EMI

- 应用:视频图形、游戏产品、数据通信、电信

- 接受 REFCLK 端子的 LVCMOS、LVTTL 输入

- 通过对适当的 V 进行编程,在 REFCLK 端子上接受其他单端信号电平

DDREF电压电平(例如,HSTL 1.5,如果VDD参考 = 1.6 V) - 支持 -40°C 至 85°C 的工业温度范围

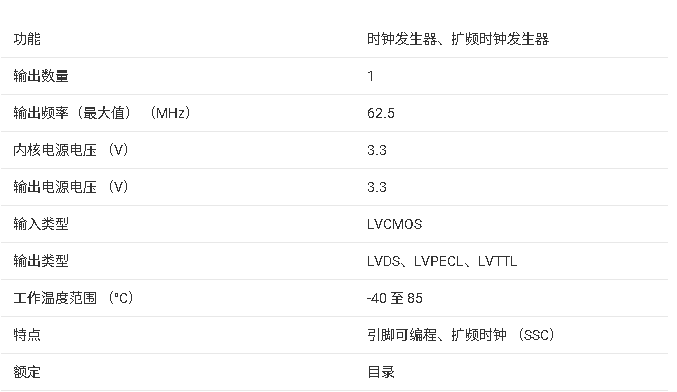

参数

1. 产品概述

CDC5801A是德州仪器(TI)推出的高性能时钟管理芯片,具备以下核心功能:

- 时钟倍频:支持×4、×6、×8倍频,输入频率19 MHz至125 MHz,输出频率150 MHz至500 MHz。

- 时钟分频:支持÷2、÷3、÷4分频,输入频率50 MHz至125 MHz,输出频率12.5 MHz至62.5 MHz。

- 可编程延迟与相位对齐:提供2.6 mUI步长的双向延迟调节,典型相位抖动低至8 ps(12 kHz–20 MHz频段)。

2. 关键特性

- 低功耗设计:典型功耗200 mW(500 MHz时),支持三种省电模式。

- 接口兼容性:支持LVCMOS、LVTTL、LVPECL、LVDS等多种电平标准。

- 工业级温度范围:-40°C至85°C,适用于严苛环境。

- 封装形式:24引脚SSOP(DBQ)封装,无需外部元件。

3. 功能模式

通过控制引脚(P0-P2)可配置以下工作模式:

- 倍频/分频模式:带相位对齐和可编程延迟(P0:2=000或001)。

- 纯倍频模式:绕过相位对齐器以降低抖动(P0:2=100)。

- 测试模式:直接输出参考时钟(P0:2=110)。

- 高阻模式:关闭输出(P0:2=01X)。

4. 电气特性

- 抖动性能:

- 倍频模式(500 MHz):典型RMS周期抖动2.1 ps。

- 分频模式(62.5 MHz):典型RMS周期抖动6.5 ps。

- 时序参数:

- 启动时间(PWRDNB↑至稳定输出):典型100 µs。

- 时钟禁用响应时间(STOPB↓):≤5 ns。

5. 应用场景

- 视频图形处理、游戏设备

- 数据通信(Datacom)与电信(Telecom)系统

- 需要低抖动时钟同步的工业设备

6. 设计支持

- 提供功能框图、时序图及典型应用电路(如多时钟相位对齐方案)。

- 详细引脚定义与真值表(如DLYCTRL/LEADLAG控制延迟方向)。

7. 生产与可靠性

- 符合TI标准质保条款,生产数据截至文档发布日有效。

- 绝对最大额定值:供电电压-0.5V至4V,工作温度-40°C至85°C。

-

CDC5801A:低抖动时钟倍频器与分频器的卓越之选2026-02-10 263

-

TI CDC421Axxx:高性能低抖动时钟发生器的深度解析2026-02-09 224

-

CDC2536 锁相环时钟驱动器技术文档总结2025-09-24 999

-

CDC7005高性能时钟合成器与抖动清除器技术文档总结2025-09-22 812

-

CDCLVD1213 1:4低附加抖动LVDS缓冲器带分频器 技术文档摘要2025-09-16 912

-

LMX1204 低噪声高频 JESD 缓冲器/乘法器/分频器技术文档总结2025-09-11 1073

-

CDC6C-Q1低功耗LVCMOS输出BAW振荡器技术文档总结2025-09-10 997

-

FPGA学习-分频器设计2023-11-03 3618

-

倍频器和分频器的主要作用2023-07-14 3233

-

将系统的时钟分频器系数以及PLL的倍频系数配置好2021-08-23 1804

-

低抖动高精度时钟发生器MAX3625B相关资料分享2021-05-18 1187

-

应用于倍频电路的预置可逆分频器设计2011-08-17 2528

全部0条评论

快来发表一下你的评论吧 !