CDCVF310 高性能时钟缓冲器技术文档总结

描述

该CDCVF310是一款高性能、低偏斜时钟缓冲器 工作频率高达 200 MHz。两组五个输出,每组提供低偏斜 CLK 的副本。上电后,输出的默认状态为低电平 无论控制引脚的状态如何。对于正常作,输出 当控制引脚 (分别为1G或2G)保持低电平,并且检测到负时钟边沿 CLK 输入。组 1Y[0:4] 或 2Y[0:4] 的输出可以切换到 缓冲模式,当控制引脚(1G和2G)保持为高电平且负极时 在CLK输入上检测到时钟边沿。该器件工作在 2.5V 和 3.3V 环境。内置输出使能毛刺抑制功能可确保 同步输出使能序列以分配全周期时钟 信号。

该CDCVF310的特点是在 -40°C 的温度下工作 至 85°C。

*附件:cdcvf310.pdf

特性

- 高性能 1:10 时钟驱动器

- 引脚到引脚偏斜< 100 ps(V)

DD3.3 伏 - V

DD范围 = 2.3 V 至 3.6 V - 输入时钟高达200 MHz(见图7)

- 工作温度范围 -40°C 至 85°C

- 输出使能毛刺抑制

- 将一个时钟输入分配到两个五个输出的组

- 采用 24 引脚 TSSOP 封装

- 引脚对引脚兼容CDCVF2310

,但 yn 处的 R = 22 串联阻尼

串联阻尼

电阻除外 - 应用

- 通用应用

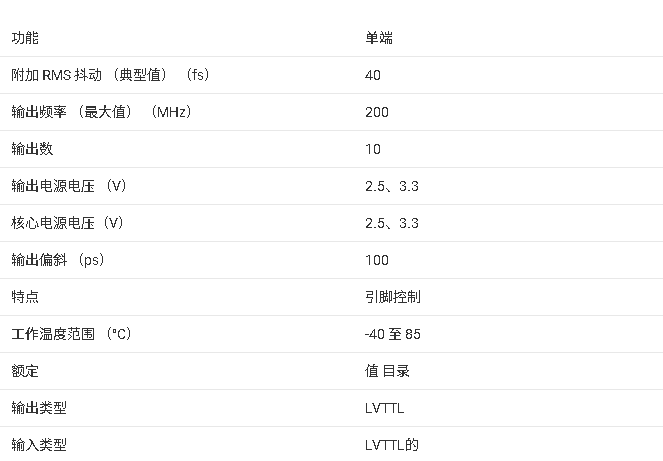

参数

1. 产品概述

CDCVF310是德州仪器(TI)推出的2.5V至3.3V高性能1:10时钟缓冲器,具有以下核心特性:

- 工作范围:电压2.3V

3.6V,温度-40°C85°C - 性能参数:支持最高200MHz时钟频率,引脚间偏移(skew)<100ps(3.3V时)

- 封装:24引脚TSSOP(PW封装),兼容CDCVF2310(除Yn端22Ω阻尼电阻)

2. 关键功能

- 双输出组:将1个输入时钟(CLK)分配至两组5路输出(1Y[0:4]和2Y[0:4])

- 输出控制:通过1G/2G引脚(高电平有效)启用/禁用对应组输出

- 抗干扰设计:内置输出使能毛刺抑制电路,确保时钟信号完整同步

3. 电气特性

- 动态功耗:随频率线性增加(见图6),典型CPD为32pF

- 时序参数:

- 传播延迟:典型值2.8ns(3.3V时)

- 输出偏移:最大150ps(同负载条件下)

- 负载能力:单引脚最大负载电容见图7(如3.6V/200MHz时约35pF)

4. 应用场景

通用时钟分配系统,适用于需低抖动、高精度时钟同步的电子设备。

5. 文档附加信息

- 版本:SCAS771B(2004年8月发布,2008年1月修订)

- 安全提示:器件需防静电处理(存储时短接引脚或使用导电泡沫)

- 订购型号:CDCVF310PW(管装)、CDCVF310PWR(卷带)等,均符合RoHS标准

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

高性能时钟缓冲器CDCVF310:特性、参数与应用解析2026-02-10 318

-

高性能时钟缓冲器CDCVF2310 - EP:设计与应用全解析2026-02-09 252

-

CDCVF2310 2.5V-3.3V高性能时钟缓冲器技术文档总结2025-09-22 892

-

CDCLVP1102高性能时钟缓冲器技术文档总结2025-09-17 894

-

CDCVF2310-EP 高性能时钟缓冲器技术文档摘要2025-09-15 922

-

CDCVF2310 2.5V至3.3V高性能时钟缓冲器数据表2024-08-23 518

-

CDCVF310时钟缓冲器数据表2024-08-22 485

全部0条评论

快来发表一下你的评论吧 !