Xilinx FPGA的同步复位和异步复位

可编程逻辑

描述

1. 普通逻辑的复位

对于xilinx 7系列的FPGA而言,flip-flop支持高有效的异步复/置位和同步复位/置位。对普通逻辑设计,同步复位和异步复位没有区别,当然由于器件内部信号均为高有效,因此推荐使用高有效的控制信号,最好使用高有效的同步复位。输入复位信号的低有效在顶层放置反相器可以被吸收到IOB中。

下面细说原因

先比较一下同步复位和异步复位的区别:

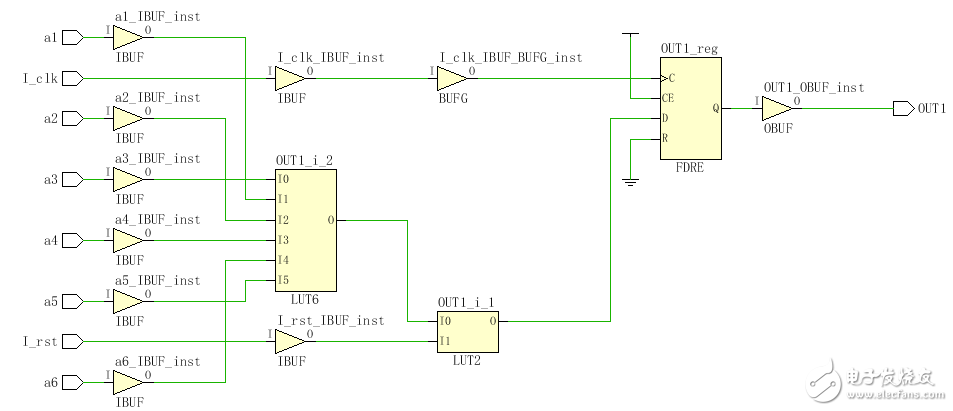

首先是同步复位,同步的控制信号包括同步置位/复位和使能,可以被吸收到LUT中,目的是为了防止控制集不同的LUT不能被综合到同一个slice中,这样虽然提高了了LUT的使用率,却降低了slice的使用率,得不偿失。

控制信号扇出不大于16的情况都可以尽可能的被吸收到同一个slice的LUT中去,在vivado中可以使用control_set_opt_threshold进行设置。

同步复位

always @(posedge I_sys_clk)

begin

if(I_rst)

begin

OUT1 《= 0;

end

else

begin

OUT1 《= &{a1,a2,a3,a4,a5,a6};

end

end

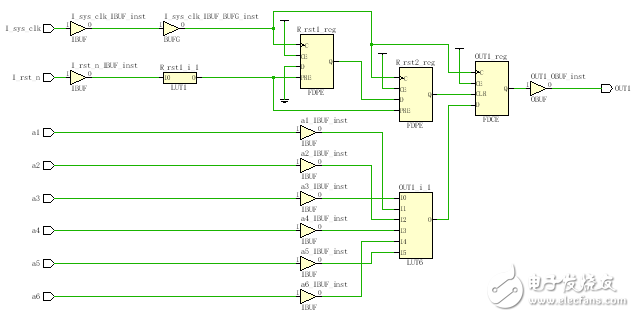

控制集优化为2时,可以看出复位信号中插入了LUT,但是由于在同一个slice中,使用造成的延时并不显著。注意对于扇出大的信号比如全局复位来说,这种控制集优化是不起作用的。

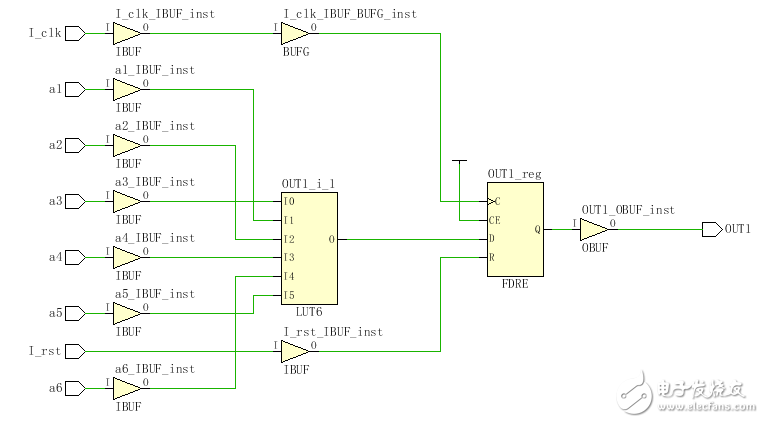

控制集合优化为0时,可以看出不会使用多于的LUT逻辑。

异步复位

always @(posedge I_sys_clk or posedge I_rst)

begin

if(I_rst)

begin

OUT1 《= 0;

end

else

begin

OUT1 《= &{a1,a2,a3,a4,a5,a6};

end

end

异步复位跟没有使用控制集综合出的结果相同,可以看出不会使用额外的LUT逻辑。

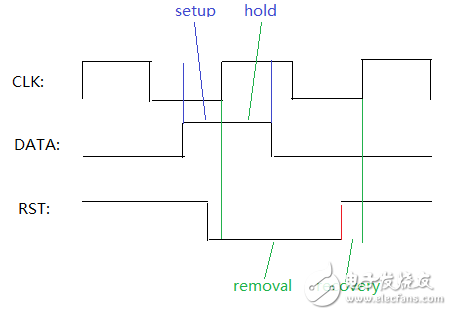

分析Recovery/Removal

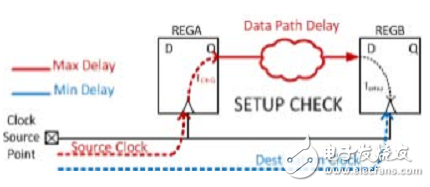

异步复位有Recover time 和Remove time 的风险,也就是说recovery time和removal time都是检查异步信号(reset或preset或set)的释放沿,释放沿必须在时钟沿前面提前recovery time释放,或者在时钟沿后removal time之后释放。

顺便简单分析一下setup/hold,对于同一个时钟,肯定满足data_path》clk_path,而hold的要求很小,所以肯定满足。当data_path过长时,setup可能不满足。

假如不作同步的复位信号,那么recovery/removal都有可能不满足。

再考虑被本地时钟同步后的recovery/removal,同理复位信号对removal的时间要求很小,同步后的复位信号的延迟就能满足removal。由于设计中的全局复位信号一般有很大的扇出,布线的延时会很严重,因此recovery的要求变得严格。最好采用全局布线资源如BUFG,尽量用局部复位或者避免使用复位。

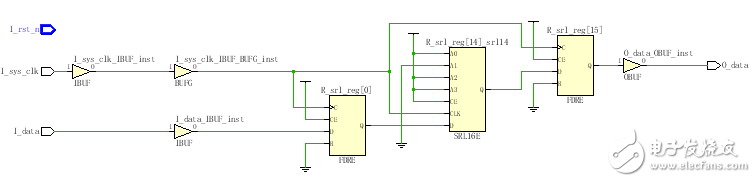

因此不管是同步复位还是异步复位,都要使用同步后的复位信号。复位信号进来后先用本地时钟打两拍。在多个时钟域的时候注意是本地时钟,不是全局时钟。并在rtl中注明是异步寄存器,使得综合工具把简单同步器综合在同一个slice中以减少延时,提高MTBF。

(* ASYNC_REG = “TRUE” *) (* keep = “true” *)reg system_reset_r;

(* ASYNC_REG = “TRUE” *) (* keep = “true” *)reg system_reset_r2;

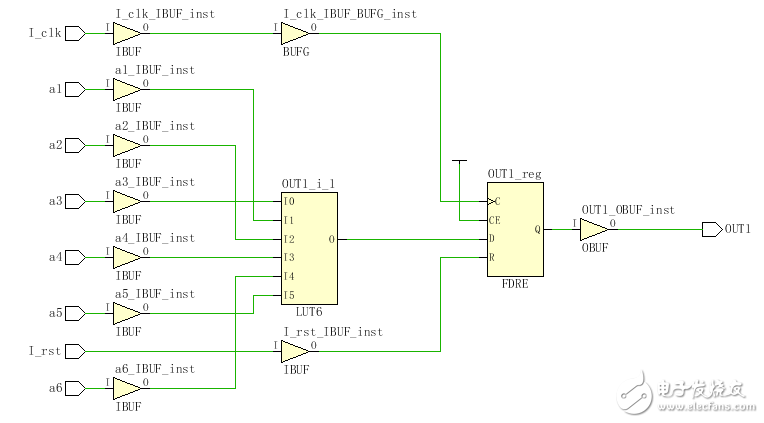

综合的结果如图,同步化的异步复位。

2. 特殊资源的复位

使用xilinx 原语SRL16、SRL32、LUTRAM

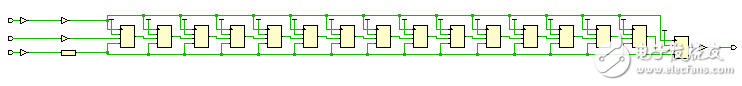

由于是利用LUT完成的上述功能,没有复位接口。只能依靠 GSR方法来完成,不能使用复位。因此,在为以上这些资源编写代码时,应注意避免在编码中使用复位,以此来保证综合工具综合出相应的电路。

使用复位信号

没有使用复位信号,可以看出综合工具自动把输入和输出寄存化,以满足更好的时序。

使用DSP48E1或BRAM

使用同步复位可以允许综合工具使用 DSP48E1或BRAM等专用资源内部的寄存器。这样能够改善设计中相应部分的器件总体使用率和性能,同时降低总体功耗。

下面以18X18的乘法器为例

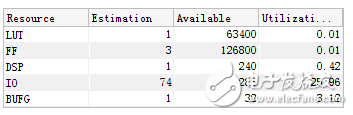

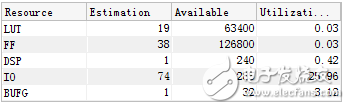

同步复位

module multi_18x18(

input I_rst ,

input I_sys_clk ,

input [17:0]I_data1 ,

input [17:0]I_data2 ,

output reg [35:0] O_data

);

reg[17:0]R_data1,R_data2;

always @(posedge I_sys_clk)

begin

if(I_rst)

begin

R_data1 《= 18‘d0;

end

else

begin

R_data1 《= I_data1;

end

end

always @(posedge I_sys_clk)

begin

if(I_rst)

begin

R_data2 《= 18’d0;

end

else

begin

R_data2 《= I_data2;

end

end

always @(posedge I_sys_clk)

begin

if(I_rst)

begin

O_data 《= 36‘d0;

end

else

begin

O_data 《= R_data1*R_data2;

end

end

endmodule

异步复位,可以看出多使用了35个FF和18个LUT

-

Xilinx FPGA异步复位同步释放—同步后的复位该当作同步复位还是异步复位?2023-06-21 2399

-

异步复位同步释放有多个时钟域时如何处理 异步复位同步释放的策略2023-07-20 2973

-

FPGA中的同步与异步复位2014-03-20 3241

-

同步复位和异步复位有什么联系与区别,优缺点!2017-11-30 100101

-

FPGA设计中的异步复位同步释放问题2018-06-07 2648

-

如何区分同步复位和异步复位?2018-06-11 7562

-

同步复位和异步复位电路简介2019-08-12 8589

-

同步复位和异步复位的优缺点和对比说明2020-09-14 2226

-

详细讲解同步后的复位是同步复位还是异步复位?2021-04-27 5976

-

【FPGA】异步复位,同步释放的理解2022-01-17 746

-

同步复位与异步复位的区别2023-08-14 8975

-

浅析异步复位同步释放与同步复位打拍模块2023-08-21 1967

-

FPGA学习-异步复位,同步释放2023-09-09 2416

-

同步复位和异步复位到底孰优孰劣呢?2024-01-16 2937

-

FPGA同步复位和异步复位2024-07-17 3721

全部0条评论

快来发表一下你的评论吧 !