Xilinx怎么定点数转浮点数

可编程逻辑

1395人已加入

描述

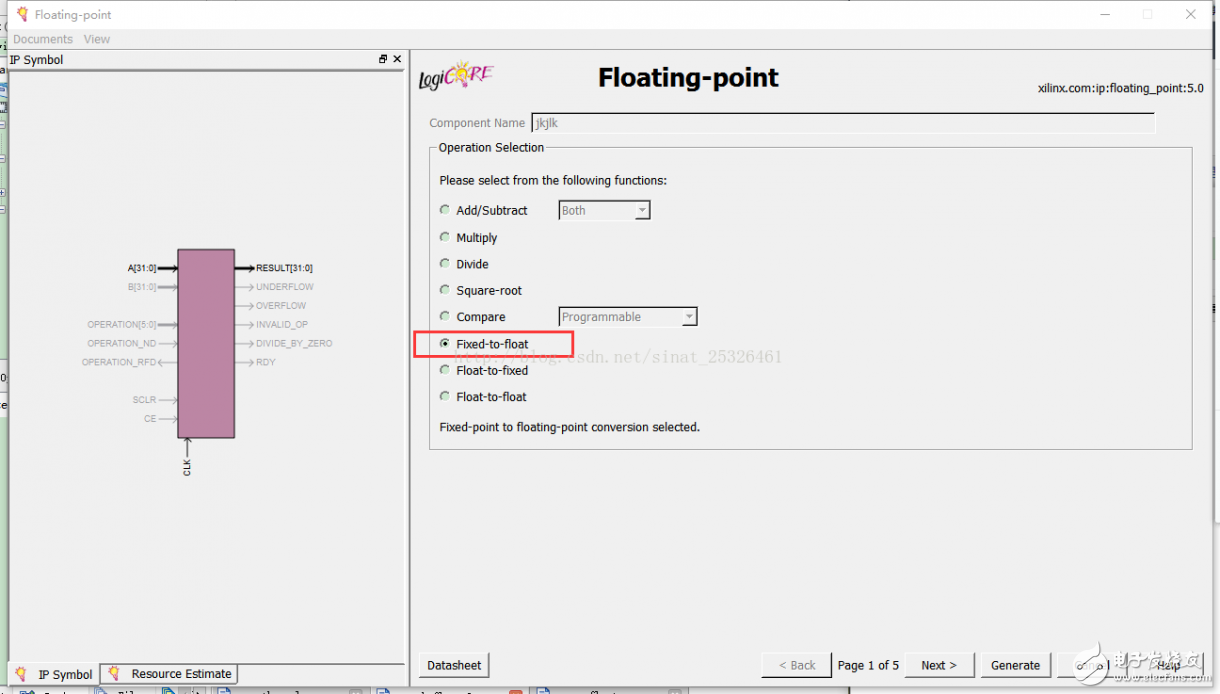

首先调用IP核

标注1:选择定点数转浮点数

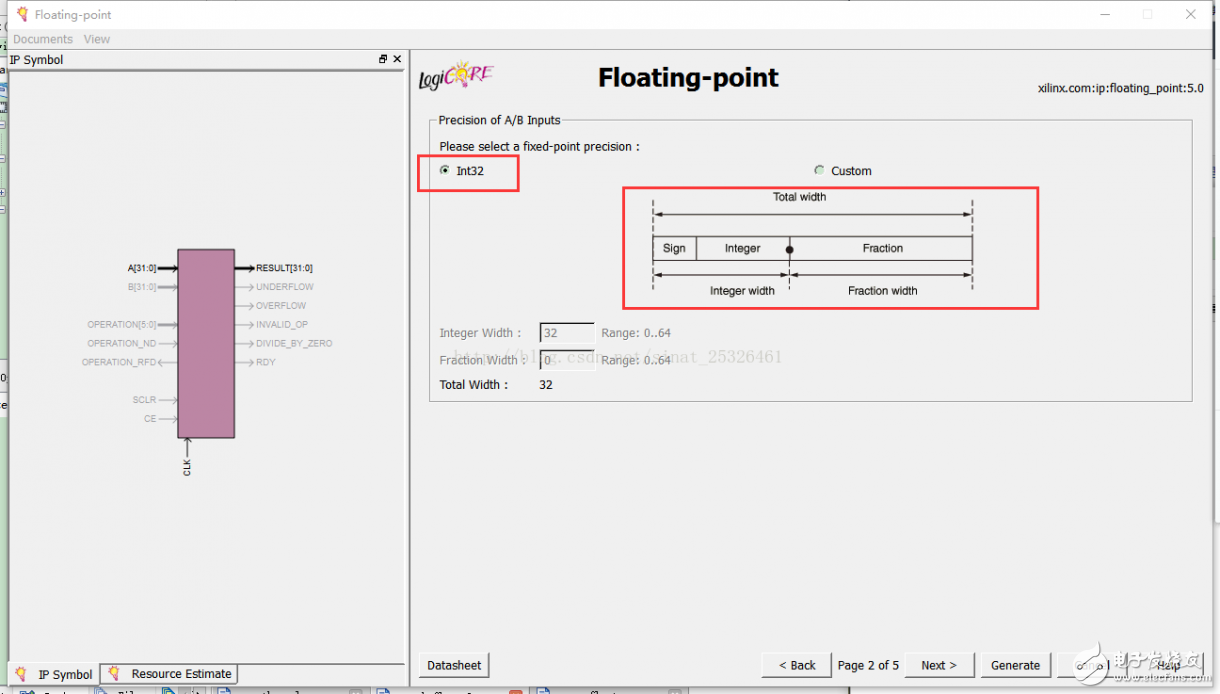

标注1:32位定点数

标注2:数字格式,符号位,整数位和小数位

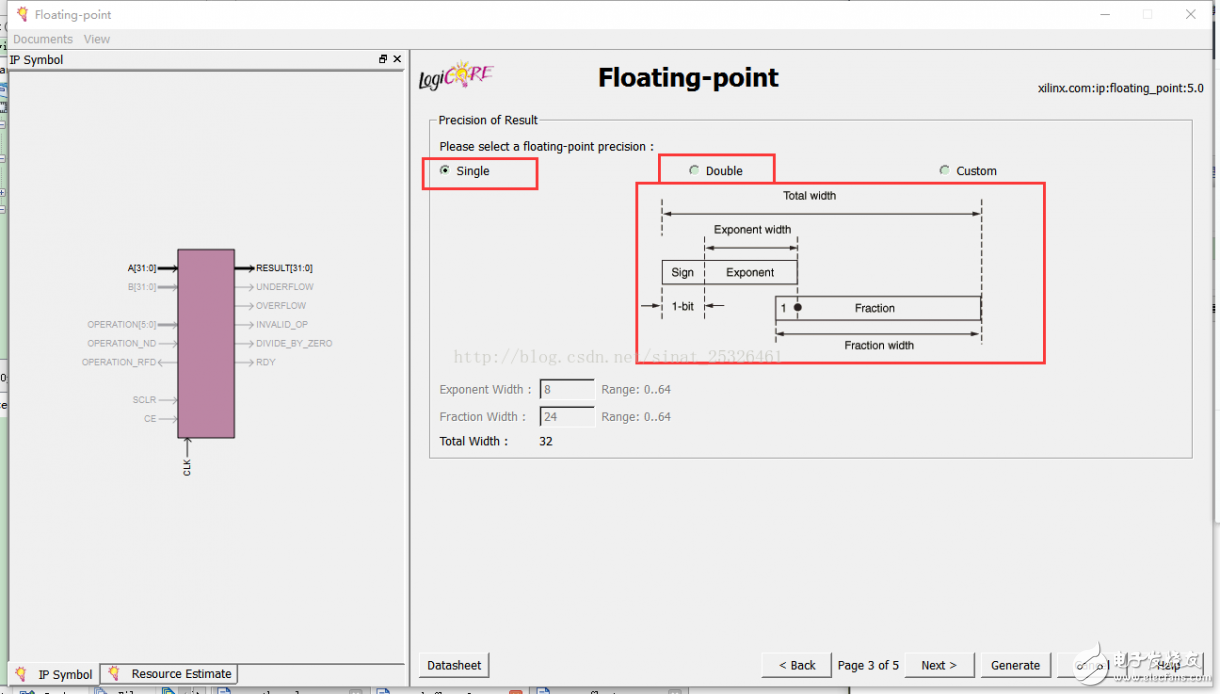

标注1,2:转化为的浮点数可以是单精度也可以是双精度。

标注3:为转化后的数据格式。

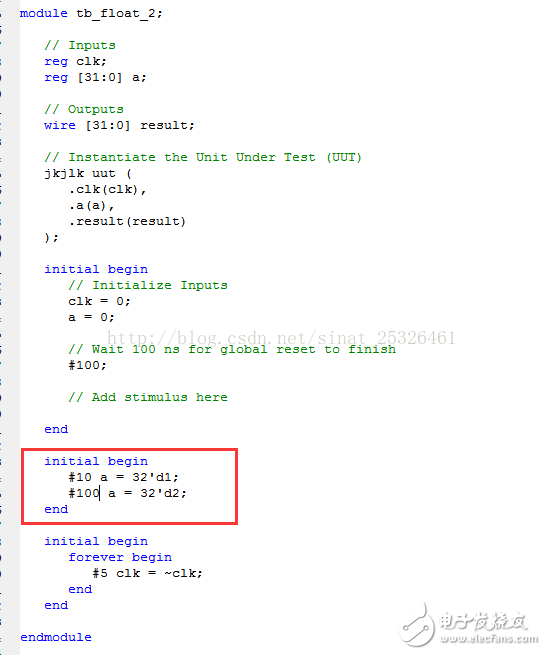

仿真如下:

假设输入数据为1和2(十进制),则输出为:

以上:单精度1的浮点数为:00111111100000000000000000000000

单精度2的浮点数为:01000000000000000000000000000000

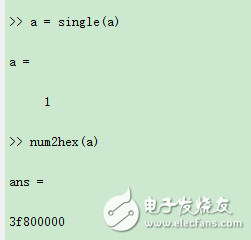

验证结果的正确性,用matlab求解:

以上:

以上同理2也正确,但是当计算连续的定点数转浮点数的时候需要注意延迟。

实验得:第一个数和第二个数之间必须保持有十倍周期以上才可以得到正确解。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

定点数表示实数的方法以及定点数在硬件上的运算验证2025-10-28 192

-

定点数和浮点数的概念 浮点数二进制序列与指数表达式之间的转化2023-08-22 10311

-

定点数和浮点数的区别是什么2022-02-21 2214

-

定点数和浮点数在STM32单片机中使用傅里叶(FFT)变换的理解2021-12-24 1958

-

功能函数中的浮点数转换为定点数2021-08-17 1729

-

verilog程序定点数的资料2019-03-27 2409

-

请问ADSP-21469的汇编指令集ISA/VISA中有没有专门用来进行浮点数和定点数转换的指令?2018-07-24 2575

-

请问28335浮点数使用IQmath转换后当定点数计算快还是用浮点数进行计算快?28335可以定点浮点混合编程吗?2018-06-14 8314

-

单片机浮点数运算的源码设计2018-03-07 11419

-

在FPGA里浮点数与定点数表示法原理展示2017-11-18 9360

-

第7章 DSP定点数和浮点数2016-09-22 4388

-

【安富莱——DSP教程】第7章 DSP定点数和浮点数(重要)2015-06-03 9043

-

浮点数与定点数2013-03-27 3345

-

功能:双字节十六进制定点数转换成格式化浮点数2009-01-19 3771

全部0条评论

快来发表一下你的评论吧 !