关于FPGA的几点问题,你了解吗?

可编程逻辑

描述

1. FPGA编程语言为何叫硬件描述语言?

硬件即FPGA硬件,硬件描述语言,也就自然地告诉我们可以通过语言来描述FPGA内部硬件。如:用y=a&b来描述一个2输入的与门,用PLL来描述类似外部时钟管理芯片。

因此,要想学好FPGA,你得用硬件的思维方式来编写代码,注重FPGA的系统结构设计,好的系统结构设计会带来质的飞跃,这就告诉我们RTL Coding其实是硬件结构设计,而非基于处理器架构的C语言程序开发,好的RTL Coding就是好的硬件结构。

2. FPGA设计是做串并操作的时序设计?

FPGA内部硬件之间的通信为多对多节点通信,不仅存在无先后顺序的并行逻辑,而且还存在先后顺序的串行逻辑,这和CPU基于指令的顺序执行逻辑完全不同,我们需要严格控制设计中各个信号之间的时间关系,以满足最终的时间上的需求,即时序要求。

因此,FPGA设计就是针对既有串行操作,又有并行操作的时序设计,即FPGA串并操作的时序设计。

3. FPGA串并操作,该如何理解?

a.执行完A后再执行B;

b.A和B之间并行执行,且没有关联;

c.A和B之间并行执行,且开始时有先后顺序,即串行逻辑;

d.FPGA的复杂系统包含上述多种灵活组合,设计时需多多琢磨思考,合理设计。

4. FPGA内部最基本硬件结构LUT,你理解吗?

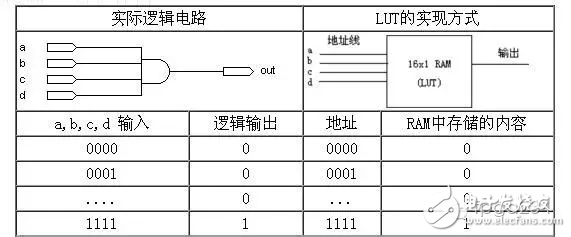

LUT的原理很简单,就是把各种可能的结果存起来标个号,每次根据输入的号来输出结果。如:一位加法器有4种可能输入对应3种结果,就只需要做一张表格,把所有的输入和输出一一对应即可。

图1 LUT实现方式

理解了LUT原理,我们可以用相同的思想来实现DDS、简单乘法、简单三角函数等,有时可以大大省资源,因为毕竟FPGA最终都是有多个LUT级联+Reg+其它 来实现各种复杂的硬件电路。

5. FPGA设计关键在于结构的设计,你同意吗?

a.首先,清楚FPGA的内部结构,基本结构为LUT;

b.然后,按照功能、时钟域、串并操作、数据流和控制流来综合考虑系统的结构;

c.最后 ,根据面积、速度和功耗来不断优化系统结构,设计出最合理的系统结构。

-

关于工厂人员定位,这几点你了解吗?2024-09-18 765

-

FPGA芯片你了解多少?2024-04-17 881

-

关于JTAG口,你了解多少?2024-01-19 1019

-

关于电机你了解多少2021-09-30 6362

-

ACTEL-FPGA独特的几点优势2021-09-28 651

-

你听过蓝牙的知识产权吗?关于蓝牙的知识产权你了解多少?2021-06-17 1913

-

关于FPGA设计的安全性你看完就懂了2021-04-30 1600

-

关于华为鸿蒙,你必须了解的几点!2020-09-07 1470

-

关于 STM32 的几点内容2020-03-08 3017

-

FPGA的几点总结,你同意吗?2017-11-22 2776

-

关于XDC约束文件,你需要知道的几点2017-02-08 5827

-

关于FPGA学习的几个问题2016-10-16 2709

-

FPGA菜鸟入门几点问题2015-12-14 3634

全部0条评论

快来发表一下你的评论吧 !