CDCM1804 1:3 LVPECL时钟缓冲器+LVCMOS输出技术文档总结

描述

CDCM1804时钟驱动器将一对差分时钟输入分配给三对LVPECL差分时钟输出Y[2:0]和Y[2:0],时钟分配的偏差最小。该CDCM1804专为驱动 50 条输电线路而设计。此外,该CDCM1804还提供单端LVCMOS输出Y3。该输出在三个LVPECL输出级上延迟1.6 ns,以最大限度地减少信号转换期间的噪声影响。

*附件:cdcm1804.pdf

CDCM1804有三个控制端子,S0、S1和S2,用于选择不同的输出模式设置。S[2:0] 端子是 3 级输入,因此最多允许 3 个 ^3^ = 27 种组合。此外,还提供了一个使能端子 (EN),用于同时禁用或使能所有输出。EN 端子也是一个 3 级输入,并将设置数量扩展到 2 × 27 = 54。

该CDCM1804的特点是在 -40°C 至 85°C 范围内工作。

为了用于单端驱动器应用,该CDCM1804还提供了一个VBB输出端子,可以直接连接到未使用的输入端作为共模基准电压源。

CDCM1804有三个控制端子,S0、S1和S2,用于选择不同的输出模式设置。S[2:0] 端子是 3 级输入,因此最多允许 3 个 ^3^ = 27 种组合。此外,还提供了一个使能端子 (EN),用于同时禁用或使能所有输出。EN 端子也是一个 3 级输入,并将设置数量扩展到 2 × 27 = 54。

该CDCM1804的特点是在 -40°C 至 85°C 范围内工作。

为了用于单端驱动器应用,该CDCM1804还提供了一个VBB输出端子,可以直接连接到未使用的输入端作为共模基准电压源。

特性

- 将一个差分时钟输入分配给三个LVPECL差分时钟输出和一个LVCMOS单端输出

- 用于两个LVPECL输出和LVCMOS输出的可编程输出分压器

- 低输出偏斜15 ps(典型值),用于LVPECL输出的时钟分配应用;LVCMOS 和 LVPECL 转换之间的 1.6 ns 输出偏移,将噪声降至最低

- V

CC范围 3 V-3.6 V - 高达 800 MHz LVPECL 和 200 MHz LVCMOS 的信号速率

- 差分输入级,宽共模范围

- 为单端输入信号提供VBB偏置电压输出

- 接收器输入阈值 ±75 mV

- 24 端子 QFN 封装(4 mm × 4 mm)

- 接受任何差分信号:LVDS、HSTL、CML、VML、SSTL-2 和单端:LVTTL/LVCMOS

参数

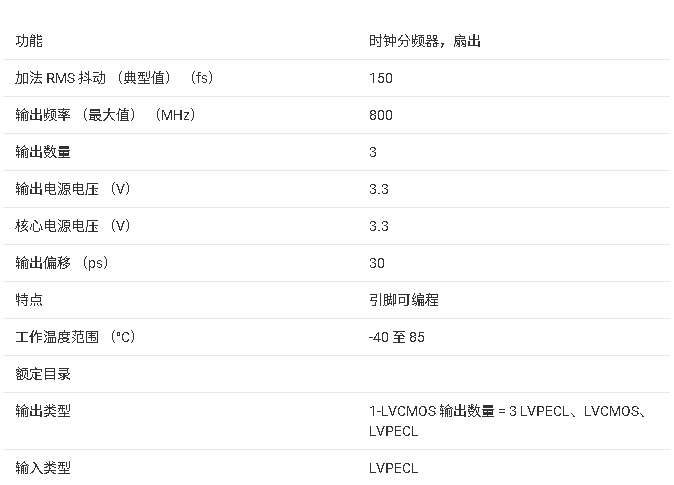

1. 核心功能

- 时钟分配:将1对差分时钟输入(IN/IN)分配至3对LVPECL差分输出(Y[2:0]/Y[2:0])和1个LVCMOS单端输出(Y3)。

- 延迟优化:LVCMOS输出设计为比LVPECL延迟1.6ns,减少信号切换时的噪声干扰。

- 分频控制:通过S[2:0]引脚编程控制LVPECL和LVCMOS输出的分频比(支持1/2/4/8/16分频)。

2. 关键特性

- 电气参数:

- 工作电压:3V–3.6V(VCC)

- 信号速率:LVPECL最高800MHz,LVCMOS最高200MHz

- 输出偏移:LVPECL间典型15ps,LVCMOS与LVPECL间1.6ns

- 兼容性:支持LVDS、HSTL、CML等差分信号及LVTTL/LVCMOS单端输入。

- 封装:24引脚QFN(4mm×4mm),含散热焊盘(需连接至VSS)。

3. 控制逻辑

- 模式选择:

- EN引脚:三态控制(接地/悬空/接VDD/2),禁用时输出高阻。

- S[2:0]引脚:三电平输入,支持27种分频组合,结合EN共54种工作模式。

- 偏置输出:VBB引脚提供VDD-1.3V参考电压,用于单端输入配置。

4. 应用设计要点

- 输入终端:推荐100Ω差分终端或AC耦合+VBB偏置方案。

- 热管理:需通过PCB散热过孔优化热阻(RθJA=55.4°C/W典型值)。

- 未使用输出:可禁用对应VDDx引脚以降低功耗。

5. 封装与版本信息

- 型号:CDCM1804(RGE/RGET封装),符合RoHS标准。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

CDCM1802时钟缓冲器:高性能与灵活性的完美结合2026-02-10 355

-

CDCM1802时钟缓冲器技术文档总结2025-09-22 759

-

CDCLVP1102高性能时钟缓冲器技术文档总结2025-09-17 856

-

CDCS503-Q1 时钟缓冲器/时钟倍频器技术文档总结2025-09-15 1045

-

CDCS504-Q1 时钟缓冲器和时钟乘法器技术文档总结2025-09-12 1238

-

HACP1208QN型低抖动LVPECL时钟缓冲器产品说明书2025-03-06 343

-

HACP1204QN型低抖动LVPECL时钟缓冲器2025-02-13 485

-

1:3 LVPECL时钟缓冲器CDCP1803数据表2024-08-21 438

全部0条评论

快来发表一下你的评论吧 !