CDC318A 1线转18线时钟驱动器技术文档总结

描述

CDC318A是一款高性能时钟缓冲器,设计用于在PC应用中分配高速时钟。该器件将一个输入 (A) 分配到 18 个输出 (Y),时钟分配的偏斜最小。该CDC318A采用3.3 V电源供电。它的特点是在 0°C 至 70°C 范围内工作。

该器件在设计时考虑了优化的 EMI 性能。根据应用布局,在大多数情况下可能不需要串联到时钟输出的阻尼电阻器(如 PC100 规范中所建议的)。

*附件:cdc318a.pdf

该器件提供标准模式(100K-bits/s)I^2^用于设备控制的 C 串行接口。实现是作为从属/接收器。设备地址在 I^2^C 设备地址表。两个我^2^C输入(SDATA和SCLOCK)具有5 V容差,并提供集成上拉电阻(典型值为140 k)。

三个 8 位 I^2^C 寄存器为每个输出提供单独的使能控制。所有输出在上电时默认启用。当低电平控制位写入控制寄存器时,每个输出都可以置于低电平输出的禁用模式。寄存器是仅写的,必须按顺序访问(即,不支持寄存器的随机访问)。

该CDC318A提供用于测试和调试目的的 3 状态输出。输出可以通过输出使能 (OE) 输入置于高阻抗状态。当OE为高电平时,所有输出都处于工作状态。当OE为低电平时,输出处于高阻抗状态。OE 提供集成上拉电阻器。

特性

- 用于同步DRAM (SDRAM)时钟缓冲应用的高速、低偏斜1-18时钟缓冲器

- 输出倾斜,t

SK(O),小于 250 ps - 脉冲偏斜,t

SK(p),小于 500 ps - 支持多达四个无缓冲 SDRAM 双列直插式内存模块 (DIMM)

- 我^2^C 串行接口为每个输出提供单独的使能控制

- 工作电压为 3.3 V

- 分布式V

CC接地引脚可降低开关噪声 - 100 MHz 工作

- ESD 保护超过 2000 V,符合 MIL-STD-883,方法 3015

- 采用48引脚收缩小外形(DL)封装

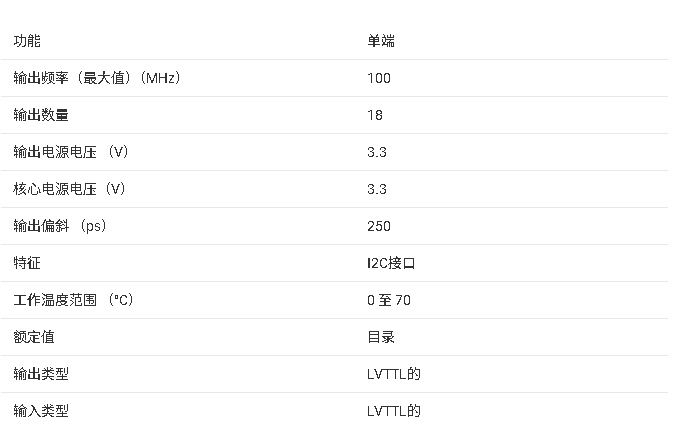

参数

1. 产品概述

CDC318A是德州仪器(TI)设计的高性能时钟缓冲器,专为PC应用中的高速时钟分配优化。核心功能包括:

- 1:18时钟分配:将单输入时钟(A)分配到18个低偏移输出端(Y0-Y17)

- 工作电压:3.3V ±10%

- 温度范围:0°C至70°C

- 封装:48引脚SSOP(DL)

2. 关键特性

- 低时钟偏移:输出偏移(tsk(o))<250ps,脉冲偏移(tsk(p))<500ps

- I²C控制接口:支持独立启用/禁用每个输出(默认全部启用)

- EMI优化设计:多数应用无需额外阻尼电阻

- 三态输出:通过OE引脚控制高阻态,集成140kΩ上拉电阻

- ESD保护:超过2000V(HBM标准)

3. 引脚功能

| 引脚类型 | 说明 |

|---|---|

| Y0-Y17 | 3.3V SDRAM时钟输出(分4组字节) |

| A (Pin11) | 主时钟输入 |

| OE (Pin38) | 输出使能(高电平有效) |

| SCLOCK/SDATA | I²C控制接口(5V兼容) |

4. I²C寄存器配置

- 3个8位寄存器控制输出使能状态(1=启用,0=强制低电平)

- 设备地址:0b1101001X(X由硬件决定)

- 写入顺序:必须按寄存器0→1→2顺序写入

5. 电气特性

- 最大频率:100MHz

- 传播延迟:1.2-4.5ns(典型值)

- 功耗:静态电流0.5mA,动态电流230mA@100MHz

6. 应用场景

- 同步DRAM(SDRAM)时钟分配

- 支持最多4个无缓冲DIMM模块

- 外部PLL反馈控制(通过5Y0/5Y1输出)

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

高性能时钟缓冲器 CDC318A:特性、参数与应用解析2026-02-10 579

-

CDC208 双路1线至4线时钟驱动器技术文档总结2025-09-24 906

-

CDC2351-EP 1线至10线时钟驱动器技术文档总结2025-09-19 1276

-

CDC318A高性能时钟缓冲器数据表2024-08-23 398

-

CDC208双通道1线至4线时钟驱动器数据表2024-08-22 380

-

CDC23511线至10线时钟驱动器数据表2024-08-21 381

全部0条评论

快来发表一下你的评论吧 !