CD74HC73/CD74HCT73双路J-K触发器技术解析与应用指南

描述

Texas Instruments CD74HC73/CD74HCT73双路J-K触发器采用硅栅极CMOS技术,实现与LSTTL零件相当的工作速度。这些器件具有低功耗标准CMOS集成电路,以及驱动10个LSTTL负载的能力。

数据手册:*附件:Texas Instruments CD74HC73,CD74HCT73双路J-K触发器数据手册.pdf

Texas Instruments CD74HC73/CD74HCT73触发器具有独立的 J、K、复位和时钟输入以及Q和Q输出。这些器件在时钟脉冲的负向转换中更改状态。R复位通过低电平输入异步完成。该器件在功能上与HC/HCT107相同,但在端子分配和某些参数极限值方面有所不同。HCT逻辑系列与标准LS逻辑系列功能和引脚兼容。

特性

- 时钟输入上的迟滞,可提高抗噪性并延长输入上升和下降时间

- 异步复位

- 互补输出

- 缓冲输入

- 典型f

MAX=60MHz(VCC=5V、CL=15pF、TA=25°C时) - 扇出(超温范围)

- 标准输出:10个LSTTL负载

- 总线驱动器输出:15个LSTTL负载

- 宽工作温度范围: –55°C至125°C

- 平衡传播延迟和转换时间

- 与LSTTL逻辑IC相比,显著降低了功耗

- HC类型

- 2 V 至 6 V 操作

- 高抗噪性:V

CC=5V时,NIL=30%,NIH=VCC的30%

- HCT类型

- 4.5 V 至 5.5 V 操作

- 直接LSTTL输入逻辑兼容性,V

IL=0.8V(最大值),VIH=2V(最小值) - CMOS输入兼容性,电压为V

OL、VOH时,II≤1µA

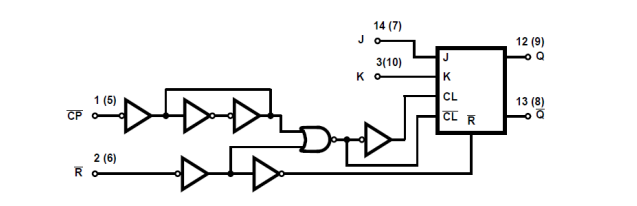

功能方框图

CD74HC73/CD74HCT73双路J-K触发器技术解析与应用指南

1. 器件概述

Texas Instruments的CD74HC73和CD74HCT73是采用硅栅CMOS工艺设计的双路J-K触发器,兼具高速操作(等效于LSTTL器件)和低功耗特性。两款器件均支持负边沿触发,并配备异步复位功能,适用于噪声敏感环境和高负载驱动场景。

- HC系列:工作电压范围2V至6V,兼容标准CMOS电平。

- HCT系列:工作电压4.5V至5.5V,直接兼容LSTTL逻辑电平(如VIL=0.8V max, VIH=2V min)。

2. 关键特性

2.1 性能参数

- 时钟抗噪能力:时钟输入内置迟滞功能,提升抗噪性并允许较慢的输入上升/下降时间(典型值tr/tf=6ns)。

- 高速操作:典型fMAX=60MHz(VCC=5V, CL=15pF, TA=25℃)。

- 驱动能力:

- 标准输出:驱动10个LSTTL负载

- 总线驱动输出:支持15个LSTTL负载

- 宽温范围:-55℃至125℃(军用级可靠性)。

2.2 低功耗设计

相比传统LSTTL逻辑器件,功耗显著降低,静态电流极低(HCT类型输入漏电流II≤1μA)。

3. 功能与工作模式

3.1 功能框图

器件包含两个独立的J-K触发器单元,每个单元具有:

- J、K输入:数据输入,上升沿锁存。

- CP(时钟)输入:负边沿触发。

- 异步复位(R) :低电平有效,直接清除输出(Q=L, Q̅=H)。

- 互补输出(Q和Q̅) :提供反相逻辑信号。

3.2 真值表

| R | CP | J | K | Q | Q̅ |

|---|---|---|---|---|---|

| L | X | X | X | L | H |

| H | ↓ | L | L | 保持 | 保持 |

| H | ↓ | H | L | H | L |

| H | ↓ | L | H | L | H |

| H | ↓ | H | H | 翻转 | 翻转 |

4. 电气规格与设计建议

4.1 电源与布局

- 电源去耦:每个VCC引脚需就近放置0.1μF旁路电容,建议并联1μF电容以抑制多频段噪声。

- 未用输入处理:必须连接至高电平或低电平,避免浮空导致逻辑状态不确定。

4.2 时序参数

- 传播延迟:CP到Q的延迟tPLH/tPHL典型值13ns(VCC=5V, CL=15pF)。

- 建立/保持时间:J/K信号需在时钟下降沿前至少16ns稳定(HCT系列)。

5. 封装与选型

| 型号 | 封装类型 | 尺寸(mm) | 适用场景 |

|---|---|---|---|

| CD74HC73M | SOIC-14 | 8.65×3.90 | 高密度PCB布局 |

| CD74HCT73E | PDIP-14 | 19.31×6.35 | 原型设计/手工焊接 |

| CD54HC73F | CDIP-14 | 19.55×6.71 | 军用/高温环境 |

6. 典型应用场景

- 时序控制电路:如分频器、状态机设计。

- 噪声敏感系统:利用迟滞时钟输入抑制工业环境干扰。

- 多负载驱动:直接驱动总线或LED阵列。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

高速CMOS逻辑双可重触发单稳态多谐振荡器:CD54/74HC123、CD54/74HCT123、CD74HC423、CD74HCT423的技术剖析2026-04-14 423

-

高速CMOS逻辑双可重触发精密单稳态多谐振荡器CD54HC4538/CD74HC4538/CD54HCT4538/CD74HCT4538深度解析2026-01-05 1190

-

高速CMOS逻辑双可重触发单稳态多谐振荡器:CD54/74HC123、CD54/74HCT123、CD74HC423、CD74HCT4232025-12-18 1300

-

高速CMOS逻辑双可重触发单稳态多谐振荡器:CD54/74HC123、CD54/74HCT123、CD74HC423、CD74HCT423深度解析2025-11-27 2817

-

CD54HC107,CD74HC107,CD74HCT107触发器数据表2024-06-03 526

-

双J-K负边三格触发器CD54AC112 CD74AC112 数据表2024-05-20 534

-

具有设置和重置正边缘触发器的双J-K触发器CD54HC109 CD74HC109 CD54HCT109 CD74HCT109数据表2024-05-17 512

-

双J-K正边三格清晰预置触发器CD54AC109 CD74AC109 数据表2024-05-08 455

-

具有复位功能的负边沿触发式双路 J-K 触发器CDx4HC73 CD74HCT73数据表2024-05-06 476

-

带复位功能的双 JK 触发器;下降沿触发-74HC732023-02-15 1030

-

MM54HC73/MM74HC73_双JK触发器与清除2016-08-24 959

-

CD54HC73, CD74HC73, CD74HCT73,2010-08-02 748

全部0条评论

快来发表一下你的评论吧 !