低附加抖动LVDS缓冲器LMK1D210x技术解析与应用指南

描述

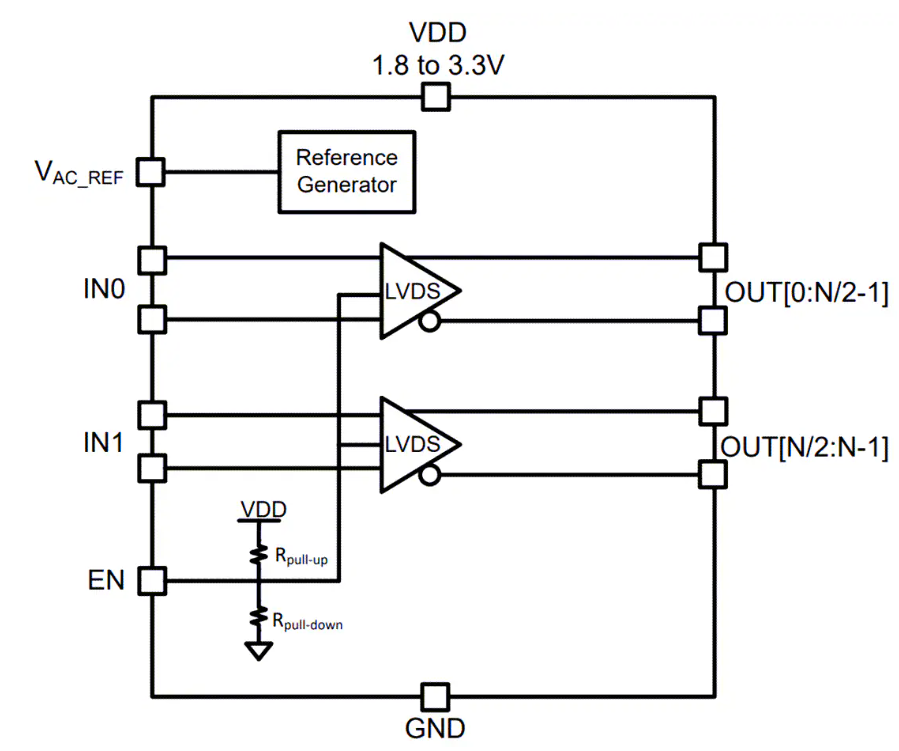

Texas Instruments LMK1D210x低附加抖动LVDS缓冲器将两个时钟输入(IN0和IN1)分配给总共多达8对差分LVDS时钟输出(OUT0、OUT7),偏移最小,用于时钟分配。每个缓冲器块包含一个输入和多达4个LVDS输出。输入可以是LVDS、LVPECL、HCSL、CML或LVCMOS。LMK1D210x专门设计用于驱动50Ω传输线路。在单端模式下驱动输入时,必须对未使用的负输入引脚施加适当的偏置电压。

数据手册:*附件:Texas Instruments LMK1D210x低附加抖动LVDS缓冲器数据手册.pdf

使用控制引脚 (EN),可以启用或禁用输出组。如果该引脚保持打开状态,则两个缓冲器及其所有输出被启用,如果切换到逻辑“0”,则两组及其所有输出均被禁用(静态逻辑“0”);如果切换到逻辑“1”,则一组及其输出被禁用,而另一组及其输出则被启用。该部件支持故障安全功能。该器件还集成了输入迟滞,可防止在没有输入信号的情况下输出随机振荡。

Texas Instruments LMK1D210x在1.8V、2.5V或3.3V电源环境下工作,具有–40°C至105°C(环境温度)特性。

特性

- 高性能LVDS时钟缓冲器系列(高达2GHz)

- 双通道1:2差分缓冲器

- 双通道1:4差分缓冲器

- 电源电压:1.71V至3.465V

- 故障安全输入操作

- 低附加抖动:(<最大60fs RMS,12kHz至20MHz,156.25MHz时)

- 超低相位噪底:-164dBc/Hz(典型值)

- 超低传播延迟:<575ps(最大值)

- 输出偏移:20ps(最大值)

- 通用输入接受LVDS、LVPECL、LVCMOS、HCSL和CML信号电平。

- LVDS基准电压V

AC_REF,可用于电容耦合输入 - -40°C 至 105°C 工业温度范围

- 封装

- LMK1D2102:3mm x 3mm、16引脚VQFN

- LMK1D2104:5mm x 5mm、28引脚VQFN

功能框图

低附加抖动LVDS缓冲器LMK1D210x技术解析与应用指南

产品概述

Texas Instruments公司的LMK1D210x系列是专为高性能时钟分配设计的高精度低附加抖动LVDS缓冲器家族,包含LMK1D2102(双1:2缓冲器)和LMK1D2104(双1:4缓冲器)两款型号。该系列产品在1.71V至3.465V的宽电源电压范围内工作,支持高达2GHz的输入频率,具有业界领先的低附加抖动性能(<60fs RMS在12kHz-20MHz带宽@156.25MHz)和极低的相位噪声基底(-164dBc/Hz典型值)。

关键特性

高性能时钟缓冲能力:

- 支持高达2GHz的时钟频率

- 超低附加抖动:<60fs RMS(12kHz-20MHz@156.25MHz)

- 极低相位噪声基底:-164dBc/Hz(典型值)

- 极低传播延迟:<575ps(最大值)

- 输出间最大偏斜仅20ps

灵活的接口兼容性:

- 通用输入接口兼容LVDS、LVPECL、LVCMOS、HCSL和CML信号电平

- 提供LVDS参考电压(VAC_REF)用于容性耦合输入

- 支持故障安全输入操作

- 内置输入迟滞功能,防止无输入信号时输出随机振荡

电源与封装:

- 工作电压范围:1.71V至3.465V

- 工业级温度范围:-40°C至105°C

- 紧凑型封装:

- LMK1D2102:3mm×3mm 16引脚VQFN

- LMK1D2104:5mm×5mm 28引脚VQFN

功能描述

LMK1D210x系列器件采用双输入架构,可将两个时钟输入(IN0和IN1)分配到最多8对差分LVDS时钟输出(OUT0-OUT7)。每个缓冲模块包含一个输入和最多4个LVDS输出,通过控制引脚(EN)可选择启用或禁用输出组。

该器件专为驱动50Ω传输线设计,在单端驱动模式下,必须在未使用的负输入引脚上施加适当的偏置电压。器件内置的故障安全功能允许在电源电压施加前驱动输入而不会损坏器件,输入迟滞特性则防止无输入信号时的随机振荡。

典型应用

LMK1D210x系列广泛应用于以下领域:

- 电信与网络设备

- 医疗成像系统

- 测试测量仪器

- 无线基础设施

- 专业音频/视频和数字标牌

JESD204B/C接口时钟分配示例:

在JESD204B/C系统中,LMK1D210x可同时分配ADC设备时钟和SYSREF时钟。第一输出组分配ADC时钟,第二输出组分配SYSREF时钟,其低输出偏斜、超低附加抖动和优异的双组间杂散抑制特性,使其成为JESD204B/C接口系统的理想时钟分配解决方案。

设计注意事项

电源管理:

高性能时钟缓冲器对电源噪声敏感,建议:

- 每个电源引脚就近放置0.1μF高频旁路电容

- 在板级电源和芯片电源间插入铁氧体磁珠

- 使用1μF和10μF电容滤除低频噪声

热管理:

- 芯片结温不得超过135°C

- 裸露焊盘是主要散热路径,必须在PCB上设计适当的热焊盘

- 建议在热焊盘下设置多个通孔连接到地平面

布局建议:

- 保持时钟走线对称和等长

- 避免直角走线以减少阻抗不连续

- 输出端终端电阻尽量靠近接收器放置

性能表现

实测数据显示,在156.25MHz时钟频率下:

- 参考源抖动:24fs RMS(12kHz-20MHz)

- LMK1D2104输出抖动:46.4fs RMS(12kHz-20MHz)

- 实际附加抖动:仅39.7fs RMS

在100MHz时钟频率下,1kHz偏移处的相位噪声低至-147dBc/Hz,表现出优异的近端相位噪声性能,非常适合雷达系统和医疗成像等对近端相位噪声要求苛刻的应用。

-

低附加抖动LVDS缓冲器LMK1D120x的技术解析与应用指南2026-02-08 381

-

LMK1D210xL:超低附加抖动LVDS缓冲器的卓越之选2026-02-06 340

-

Texas Instruments LMK1D210xL低附加LVDS缓冲器数据手册2025-07-17 945

-

LMK1D121x低附加抖动LVDS缓冲器数据表2024-08-20 359

全部0条评论

快来发表一下你的评论吧 !