SN74HCS373 Octal透明锁存器技术解析与应用指南

描述

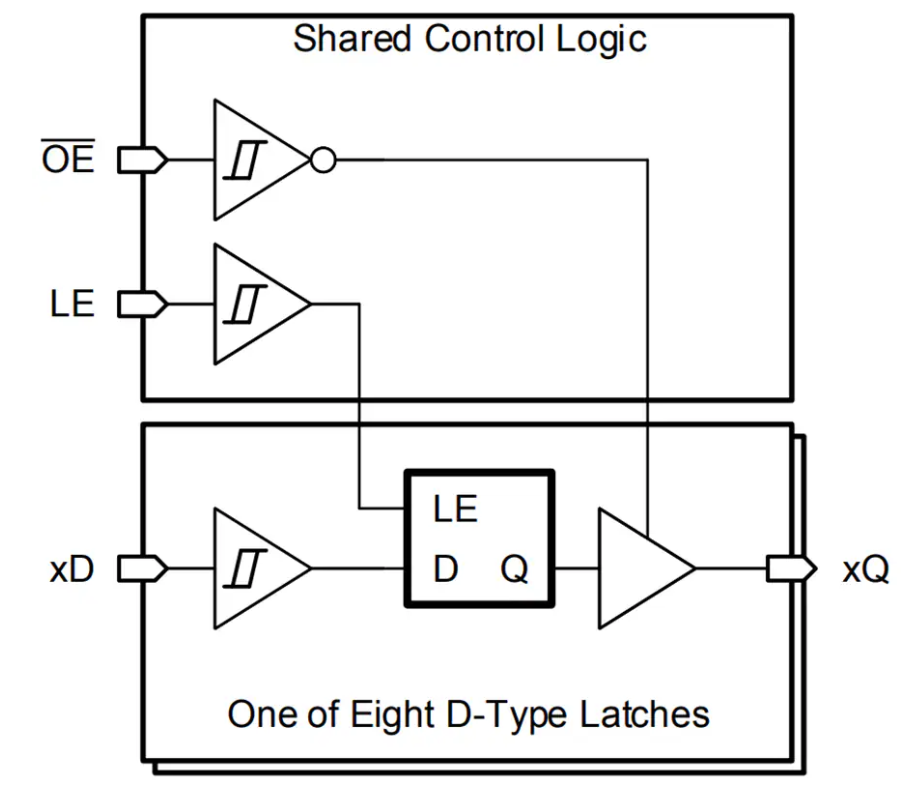

Texas Instruments SN74HCS373/SN74HCS373-Q1八路透明D类锁存器包含八个D类锁存器。所有输入均包括施密特触发器架构。Texas Instruments SN74HCS373/SN74HCS373-Q1的所有通道共享锁存使能 (LE) 输入和输出使能 (OE) 输入。

数据手册:

特性

- 符合汽车应用类AEC-Q100标准:

- 器件温度等级1:-40°C至+125°C,T

A - 器件人体模型 (HBM) 静电放电 (ESD) 分类等级2

- 器件充电器件模型 (CDM) ESD分类等级C6

- 器件温度等级1:-40°C至+125°C,T

- 低功耗

- 典型I

CC为100nA - 典型输入漏电流:±100nA

- 典型I

- 采用可湿性侧翼QFN (WBQB) 封装

- 宽工作电压范围:2V至6V

- 施密特触发器输入允许缓慢或嘈杂的输入信号

- 输出驱动:±7.8mA (6V)

TA扩展环境温度范围:–40°C至+125°C

功能框图

SN74HCS373 Octal透明锁存器技术解析与应用指南

一、器件概述

SN74HCS373是德州仪器(TI)推出的八路D型透明锁存器,采用Schmitt-Trigger输入架构和3态输出设计,适用于低功耗、高噪声抑制场景。其关键特性包括:

- 宽电压工作范围:2V至6V,兼容多种逻辑电平。

- 低功耗:典型静态电流仅100nA,输入漏电流±100nA。

- 高驱动能力:6V电压下输出驱动电流达±7.8mA。

- 工业级温度范围:-40°C至+125°C。

二、核心功能与原理

1. 功能框图

- 共享控制逻辑:所有通道共用锁存使能(LE)和输出使能(OE)信号。

- 透明锁存模式:

- LE=高电平:数据从D端透明传输至Q端。

- LE=低电平:Q端保持最后一次锁存值,无视D端变化。

- 3态输出控制:

- OE=低电平:输出有效(高/低电平)。

- OE=高电平:输出高阻态(不影响内部锁存状态)。

2. Schmitt-Trigger输入优势

- 抗噪能力强:内置迟滞(ΔVT典型值0.2V~0.6V),可容忍缓慢或噪声输入信号。

- 低动态功耗:相比传统CMOS输入,静态功耗极低,但需注意未用输入需接地或VCC。

三、典型应用场景

1. 并行数据存储

- 应用示例:微控制器扩展存储接口,通过LE信号控制数据锁存时机,OE管理总线占用。

- 时序要求:

- 数据建立时间(tsu)最小6ns(VCC=6V时)。

- 保持时间(th)为0ns,适合高速数据捕获。

2. 数字总线缓冲

- 多设备共享总线:利用3态输出隔离非活动设备,避免总线冲突。

- 布局建议:

- 总线终端加10kΩ上拉/下拉电阻,确保高阻态时电平稳定。

- 走线长度≤50mm以减少容性负载(CL≤50pF)。

四、设计注意事项

1. 电源与热管理

- 去耦电容:VCC与GND间并联0.1μF+1μF电容,贴近器件放置。

- 热阻参数:

- VQFN封装(RKS)θJA=83.2°C/W,VSSOP封装(DGS)θJA=130.6°C/W。

- 避免持续输出电流超过35mA(绝对最大值)。

2. 输入/输出处理

- 未用引脚:输入必须接VCC或GND,输出可悬空。

- 并联增强驱动:同信号驱动多通道时,可并联输出以提升电流能力。

五、性能参数速查

| 参数 | 条件(VCC=6V) | 典型值 | 单位 |

|---|---|---|---|

| 传播延迟(tpd) | D→Q | 9.6ns | ns |

| 输出上升时间(tt) | CL=50pF | 7.4ns | ns |

| 输出驱动电阻(低态) | IOL=7.8mA | 30Ω | Ω |

六、封装与选型

- 封装选项:

- RKS(VQFN-20) :4.5mm×2.5mm,适合高密度布局。

- DGS(VSSOP-20) :5.1mm×3.0mm,便于手工焊接。

- 订购型号:SN74HCS373DGSR(VSSOP)、SN74HCS373RKSR(VQFN)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

低功耗D型透明锁存器;三态-74AUP1G3732023-02-14 607

-

八路D型透明锁存器;三态-74HC_HCT3732023-02-15 576

-

八路D型透明锁存器;三态-74ALVC3732023-02-16 605

-

八路D型透明锁存器;三态-74HC_HCT373_Q1002023-02-17 573

-

八路D型透明锁存器;三态-74AHC3732023-02-20 605

-

具有施密特触发输入和三态输出的 SN74HCS373八路透明D型锁存器数据表2024-05-08 570

-

具有三态输出的八进制D型透明锁存器SN54ACT373 SN74ACT373数据表2024-05-09 636

-

具有施密特触发输入和三态输出的 SN74HCS373-Q1 汽车类八路透明D型锁存器数据表2024-05-13 396

-

具有三态输出的八进制透明D型锁存器SN54BCT373 SN74BCT373数据表2024-05-17 427

-

SN74ACT373-EP八进制D型透明锁存器数据表2024-06-03 565

-

SN74AC373-EP八路D型透明锁存器数据表2024-06-04 471

-

SN74AC573 Octal D型透明锁存器技术解析与应用指南2025-09-04 1572

-

SN74HCS573 Octal D-Type Latch技术解析2025-09-24 1125

-

74HC373:8位D型透明锁存器的详细解析2026-03-13 295

-

74LVC373A:8 位 D 型透明锁存器的详细剖析与应用指南2026-03-16 265

全部0条评论

快来发表一下你的评论吧 !