CDC204 3.3V六路反相器/时钟驱动器技术文档总结

描述

CDC204 包含六个独立的逆变器。该器件执行布尔函数 Y = A。它专为开关输出之间需要低偏斜的应用而设计。

CDC204 的特点是从 T 一个 = 25°C 至 70°C。

*附件:cdc204.pdf

特性

- CDC204 取代 74AC11204

- 时钟驱动器应用的低偏斜传播延迟规范

- CMOS兼容输入和输出

- 流通架构优化了

PCB布局 - 中心引脚 V

CCGND 引脚配置可最大限度地降低高速开关噪声 - 史诗 ^TM的^ (增强型植入式CMOS)1-um工艺

- 125°C时典型闩锁抗扰度为500 mA

- 封装选项包括塑料小外形封装 (DW))

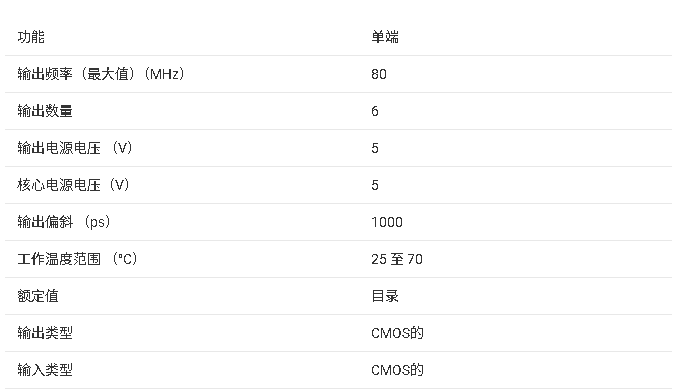

参数

1. 产品概述

CDC204是德州仪器(TI)设计的3.3V六路独立反相器/时钟驱动器,采用EPIC™(高性能植入CMOS)工艺,专为低偏移时钟分配应用优化。核心功能为布尔运算 Y = A̅(输入反相输出),适用于高速数字系统(如微处理器和同步DRAM),工作温度范围 25°C至70°C。

2. 关键特性

- 低偏移设计:确保多路输出信号的同步性,最大输出偏移(tsk(o))仅 1ns。

- 高驱动能力:支持 50Ω传输线,输出电流±24mA(5V供电)。

- 优化布局:

- 中心引脚配置(VCC/GND)减少高速开关噪声。

- 直通式架构(Flow-Through)简化PCB布线。

- 封装与可靠性:

- 20引脚SOIC(DW)封装,符合RoHS标准。

- 典型锁存免疫电流500mA(125°C)。

3. 电气参数

| 参数 | 条件 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|

| 供电电压VCC | - | 4.75 | 5.0 | 5.25 | V |

| 高电平输出VOH | IOH = -24mA | 4.19 | - | 4.68 | V |

| 低电平输出VOL | IOL = 24mA | - | - | 0.44 | V |

| 传播延迟tPLH/tPHL | CL=50pF, VCC=5V | 2.9 | - | 5.7 | ns |

| 静态功耗ICC | VI = VCC/GND, IO=0 | - | 4 | 40 | µA |

4. 功能与引脚配置

逻辑功能:输入A与输出Y反相(见下表)。

输入A 输出Y H(高) L(低) L(低) H(高) 引脚说明:

- 输入引脚:1A-6A(对应输出1Y-6Y)。

- 电源引脚:VCC(16、15)、GND(4-7)。

- NC引脚:17、14(无内部连接)。

5. 应用注意事项

- 布局建议:分散VCC/GND引脚以降低噪声。

- 绝对最大额定值:

- 输入/输出电压范围:-0.5V至VCC+0.5V。

- 最大功耗:1.6W(55°C静止空气)。

- 动态性能:

- 输入时钟频率上限:80MHz(过渡速率≤10ns/V)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

CDC509:高性能3.3V锁相环时钟驱动器2026-02-10 384

-

CDC536 3.3V锁相环时钟驱动器技术文档总结2025-09-24 2322

-

CDC509 3.3V相位锁定环时钟驱动器技术文档总结2025-09-23 1098

-

CDC2351-Q1 1:10时钟驱动器技术文档总结2025-09-22 946

-

CDC2351-EP 1线至10线时钟驱动器技术文档总结2025-09-19 1276

-

CDC203反相器/时钟驱动器数据表2024-08-23 451

-

CDC516: 3.3V锁相LOOP时钟驱动器数据表2024-08-22 496

全部0条评论

快来发表一下你的评论吧 !