CDC208 双路1线至4线时钟驱动器技术文档总结

描述

CDC208包含双时钟驱动器电路,可将一个输入信号扇出到四个输出,时钟分配的偏斜最小(见图2)。该器件还为每个电路提供两个输出使能(OE1和OE2)输入,可以强制将输出禁用到高阻抗状态或高或低逻辑电平,而与相应A输入上的信号无关。

偏斜参数是针对许多应用中常见的降低温度和电压范围指定的。

CDC208 的工作温度为 -40°C 至 85°C。

*附件:cdc208.pdf

特性

- 时钟驱动器应用的低偏斜传播延迟规范

- TTL兼容输入和CMOS兼容输出

- 流通架构优化了

PCB布局 - 中心引脚 V

CCGND 引脚配置可最大限度地降低高速开关噪声 - 史诗 ^TM的^ (增强型植入式CMOS)1-um工艺

- 125°C时典型闩锁抗扰度为500 mA

- 封装选项包括塑料小外形 (DW)

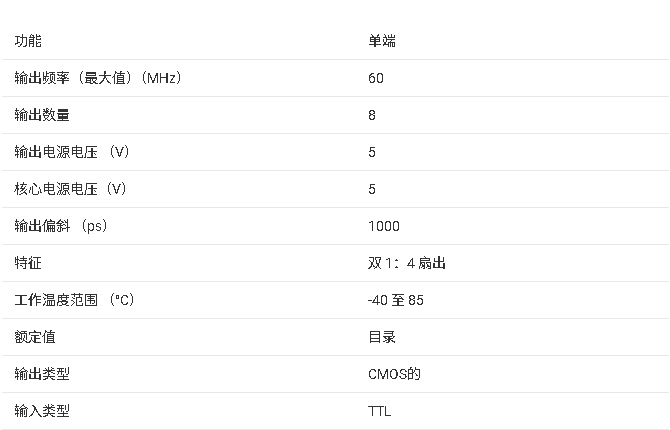

参数

1. 产品概述

CDC208是德州仪器(TI)设计的双路1线转4线时钟驱动器,采用EPIC™(高性能植入CMOS)工艺,专为低偏移时钟分配优化。核心功能包括:

- 双独立驱动通道:每路输入(1A/2A)可驱动4路输出(1Y1-1Y4/2Y1-2Y4),支持3态输出控制(通过OE1/OE2使能)。

- 低偏移设计:输出间最大偏移(tsk(o))仅 1ns,适用于同步DRAM、微处理器等高速系统。

- 工作温度:**-40°C至85°C**,工业级应用场景。

2. 关键特性

- 电气兼容性:

- TTL兼容输入,CMOS兼容输出。

- 供电范围 4.5V至5.5V(典型5V),静态功耗仅 8µA。

- 抗干扰设计:

- 中心引脚VCC/GND布局减少高速开关噪声。

- 典型锁存免疫电流 500mA(125°C)。

- 封装选项:

- 20引脚SOIC(DW)或SOP(NS)封装,符合RoHS标准。

3. 功能逻辑

使能控制真值表:

OE1 OE2 A输入 输出状态 L L L/H 反相输出(低/高) H X X 高阻态(Z) X H X 固定高电平(H) 引脚配置:

- 输入:1A(19脚)、2A(14脚)。

- 使能端:1OE1/1OE2(18/17脚)、2OE1/2OE2(13/12脚)。

- 电源:VCC(16/15脚)、GND(4-7脚)。

4. 电气参数

| 参数 | 条件 | 最小值 | 最大值 | 单位 |

|---|---|---|---|---|

| **高电平输出(VOH)** | IOH = -24mA, VCC=5V | 3.94 | 4.68 | V |

| **低电平输出(VOL)** | IOL = 24mA, VCC=5V | - | 0.44 | V |

| **传播延迟(tPLH/tPHL)** | CL=50pF, VCC=5V | 3.6 | 11.7 | ns |

| **输出使能时间(tPZH)** | - | 4.2 | 10.2 | ns |

5. 应用注意事项

- 布局建议:

- 使用短且等长的PCB走线以减少偏移。

- 避免输入信号过渡时间超过 10ns/V。

- 绝对最大额定值:

- 输入电压范围:**-0.5V至VCC+0.5V**。

- 最大功耗:1.6W(55°C静止空气)。

总结:CDC208是一款高精度时钟分配器件,适用于需严格同步的5V系统设计,其低偏移和灵活使能控制使其成为高速数字电路的理想选择。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

CDC319:高性能1线转10线时钟驱动器2026-02-10 254

-

CDC341 1线至8线时钟驱动器技术文档总结2025-09-24 891

-

CDC2351-EP 1线至10线时钟驱动器技术文档总结2025-09-19 1292

-

CDC319带I2C控制接口的1线至10线时钟驱动器数据表2024-08-22 450

-

CDC23511线至10线时钟驱动器数据表2024-08-21 386

全部0条评论

快来发表一下你的评论吧 !