如何解决NB模块时间不准问题

描述

常见问题

产品不良率非常高,发现时间偏移巨大,每天有15s之多,无法满足NB应用要求。

应用:物联网-NB模组

如何解决此类时间偏移巨大的问题呢?

简单:首先把基本信息罗列,结合实际测试,适当修改晶体的负载电容。

干货分享

主芯片:是一款低功耗应用的NB-IoT Cat-NB2 SoC通讯芯片;

时钟回路使用的晶振:32.768KHz 12.5pf +-20ppm晶振

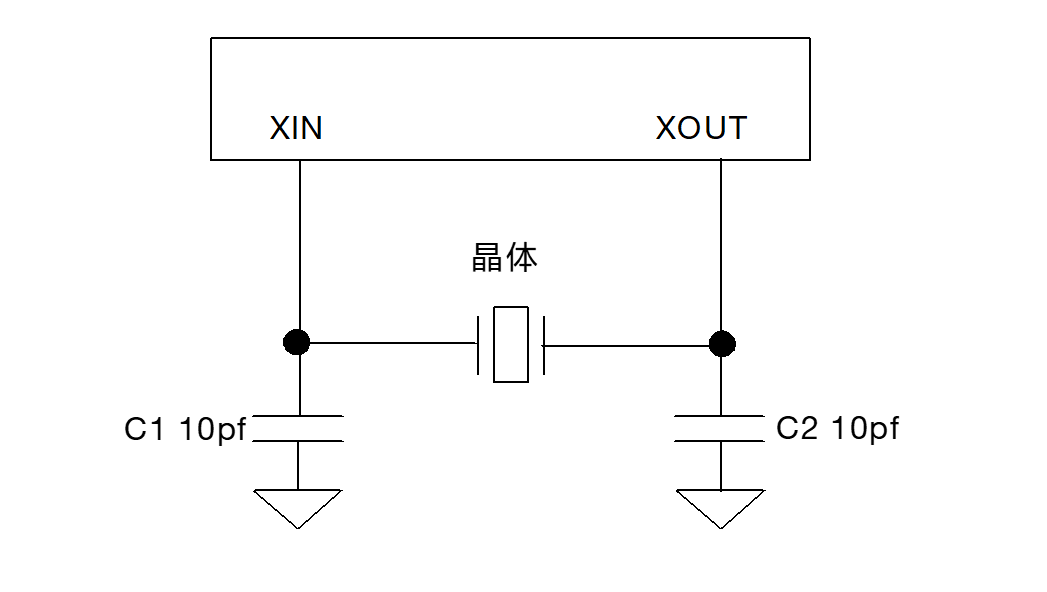

图:32KHz时钟回路原理图

原理图中,可以看到,此设计使用两个10pf外接电容,而且布线紧凑。

我们大致可以推断出,两个10pf的外接电容,其电容串联+寄生电容2pf左右,整体负载电容约为7pf,与32.768KHz的12.5pf条件不符,相差太多。

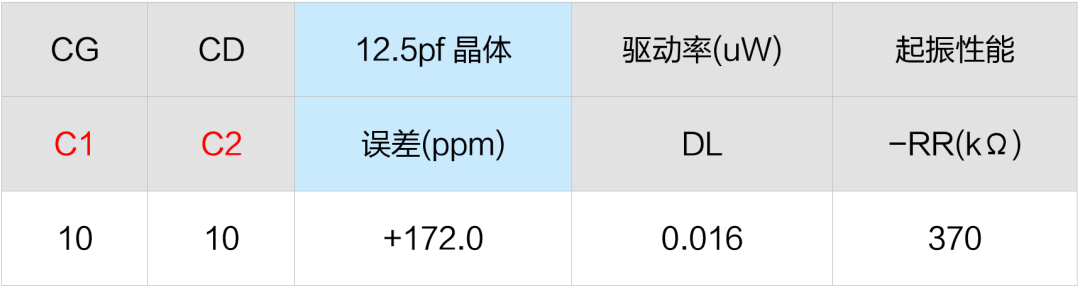

实际测试:

当前使用两个10pf,输出误差达到+170ppm之多,1ppm误差对应0.0864s/day,+170ppm约为每天偏差14s,与反馈一致,这显然是不可行的。

根据外接电容与输出频率的反比关系,此时增加C1和C2的电容值才行,但是电容的增加,会使其起振性能下降,功耗也会增加,不适合当前的模块(NB)应用。并且当前的起振能力仅有370K欧姆,如果增加大量电容值,晶体回路必然会存在不起振的风险。

此时需要更换小负载电容值,内阻更低的晶振才行。

解决思路

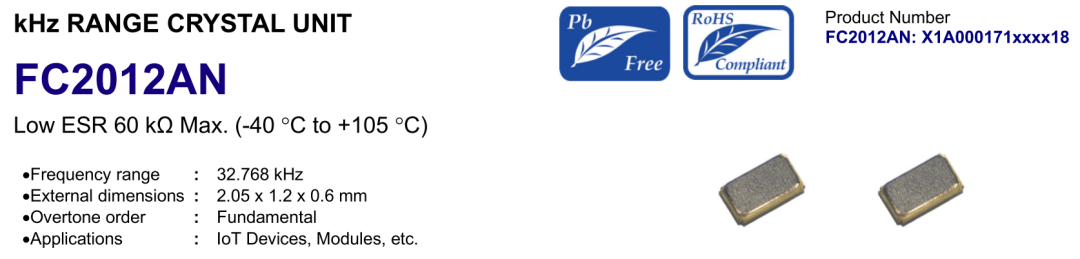

选用Epson 32.768KHz晶振:

FC2012AN 7pf +-20ppm

其特点是低内阻,仅有60K欧姆(同类型的晶振一般是90K欧姆,内阻越低,功耗越低)。

2.0*1.2mm的小封装,整体非常适合低功耗、小封装应用。

图:FC2012AN官网截图

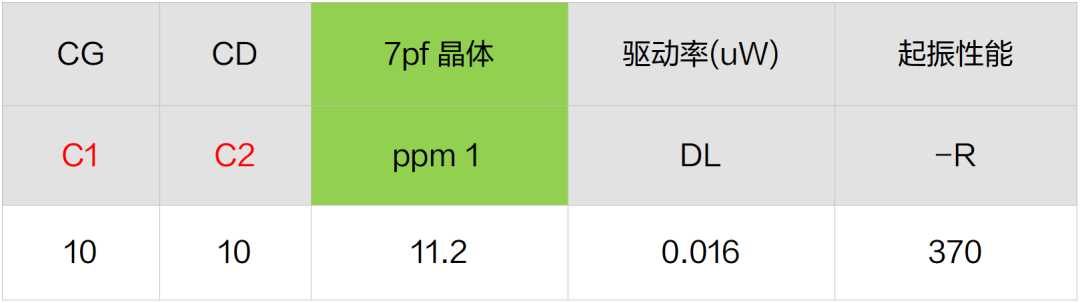

实际测试:

可以看到,如果改用FC2012AN 7pf晶体,回路的输出频率误差仅有11.2ppm,起振余量是370K欧姆,大于5倍的ESR(60K欧姆*5=300K)值。

我们看一下误差是多少:

0.0864s/day*11.2=0.96768s/day 即每天不到1s。

总结:

时间不准,需要调整外接的两个电容;

低内阻意味着功耗更低,否则有起振的风险。

-

AD5933低频率测量阻值不准确如何解决?2024-01-08 549

-

STM32G030K6T6芯片ADC采集电压,测量有的时候会不准如何解决?2024-03-07 718

-

NB模块使用其他NB上的SIM卡无法连接到网络是怎么回事?2024-06-04 12059

-

时间总是不准该怎么办?风雷仪表 2023-08-17

-

STM32F103滴答定时器定时不准的原因是什么?如何解决?2021-11-24 2602

-

NB-IoT模块介绍2022-02-24 2567

-

三大运营商纷纷宣布NB-IoT的测试和商用时间 NB-IoT将迎来一波爆发2018-05-14 2733

-

时控开关为什么时间不准确,其原因是为何2021-03-08 14259

-

如何解决BOM数据总是不准的问题2021-09-26 4381

-

51单片机怎么显示当前时间_导航显示的剩余时间是怎么来的,准不准2021-11-23 1083

-

基于STM32的NB-IoT模块驱动2022-01-12 1704

-

什么是NB模组/NB-IOT模块的选择2021-09-30 6831

-

NB-IoT模组、NB模块应用的选择与发展前景2021-09-08 3961

-

32.768khz晶振时间跑不准有偏差的原因2023-07-26 3775

-

什么是NB-IoT模块?什么是4G模块?NB-IoT模块与4G模块之间的区别2024-02-01 14129

全部0条评论

快来发表一下你的评论吧 !