PCIe 5.0高速信号中继技术解析——基于SN75LVPE5421线性转接驱动器

描述

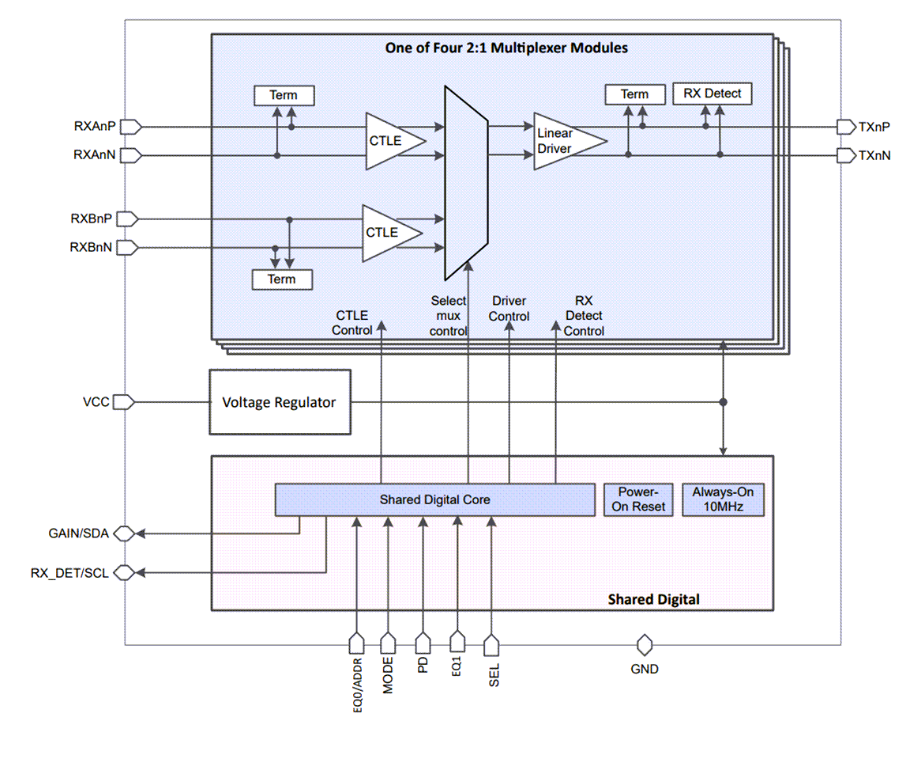

Texas Instruments SN75LVPE5421四通道线性转接驱动器是一款低功耗、高性能线性转接驱动器,设计用于支持PCIe 5.0和其他速度高达32Gbps的接口。该器件配有集成式解复用器 (demux)。SN75LVPE5421接收器采用连续时间线性均衡器 (CTLE) 提供高频升压。该均衡器可以打开输入眼,它由于PCB迹线和电缆等互连介质引起的符号间干扰 (ISI) 而完全闭合。在PCIe链路培训期间,线性转接驱动器和根复变 (RC) 和端点 (EP) 之间的无源通道经过培训,可实现出色的发射和接收均衡设置,从而实现出色的电气链路。该器件具有低通道间串扰、低附加抖动和出色的回波损耗,因此几乎成为链路中的无源元件。该器件设有内部线性稳压器,可为高速数据路径提供纯净的电源,从而对电路板上的任何电源噪声具有较高的抑制能力。

数据手册:*附件:Texas Instruments SN75LVPE5421四通道线性转接驱动器数据手册.pdf

Texas Instruments SN75LVPE5412在生产过程中进行高速测试,实现可靠的大批量制造。该器件还具有低交流和直流增益变化,在大容量平台部署中提供一致的均衡性。

特性

- 四通道PCIe 5.0线性转接驱动器或中继器,集成2:1多路复用器

- 与协议无关的线性转接驱动器,兼容PCIe、UPI、CCIX、NVLink、DisplayPort、SAS、SATA和XFI

- 3.3V单电源 – 可以使用PCIe电源轨

- 低有源功率:720mW(4通道运行)

- 无需散热片

- 提供高达24dB均衡(16GHz时)

- 出色的RX/TX差分RL:-10dB(8GHz至16GHz)

- 低附加RJ:55fs RMS,带PRBS数据

- 低延迟:90ps

- 自动接收器检测和无缝支持PCIe链路培训

- 通过引脚控制或SMBus/I^2^C进行器件配置

- 通过引脚选择多路复用器

- 内部稳压器可抑制电源噪声

- 高速生产测试,实现可靠制造

- 支持x4、x8和x16总线宽度,具有一个或多个器件

功能框图

PCIe 5.0高速信号中继技术解析——基于SN75LVPE5421线性转接驱动器

随着PCIe 5.0协议的普及,32Gbps高速信号在传输过程中面临严重的信道损耗问题。Texas Instruments推出的SN75LVPE5421四通道线性转接驱动器,以其创新的架构和性能成为解决这一挑战的关键器件。本文将结合数据手册深度解析其技术特性与应用方案。

一、核心特性与技术突破

- 协议兼容性与高性能

- 支持PCIe 5.0/4.0/3.0全协议栈,兼容UPI、CCIX等32Gbps高速接口

- 单通道24dB@16GHz均衡能力,可修复完全闭合的信号眼图

- 仅90ps超低延迟,55fs RMS附加随机抖动,满足PCIe 5.0苛刻时序要求

- 创新架构设计

- 集成2:1多路复用器,支持x4/x8/x16总线宽度扩展

- 双级连续时间线性均衡器(CTLE),支持19级可编程EQ配置

- 内置线性稳压器,电源噪声抑制比达33dB@2.5MHz

- 能效优势

- 四通道总功耗仅720mW(3.3V供电)

- 无散热片设计,工作温度范围-40°C至85°C

二、关键电路设计解析

- 接收端技术

- CTLE均衡器采用可配置双级结构:

- 第一级:0-15dB可调基础均衡

- 第二级:0-7dB精细调整

- 支持动态EQ配置文件切换,适配PCB/电缆等不同介质

- CTLE均衡器采用可配置双级结构:

- 发送端优化

- 差分回波损耗<-10dB@16GHz

- 100Ω差分阻抗,支持800mVpp发射幅度

- 集成RX检测状态机,符合PCIe链路训练规范

- 配置灵活性

- 双控制模式:

- 引脚模式:通过5级电平引脚快速配置

- SMBus/I2C模式:支持400kHz总线速率,每通道独立参数配置

- 双控制模式:

三、典型应用场景

- 服务器架构

- 解决背板布线导致的信号完整性劣化

- 实现CPU与多PCIe插槽间的信号中继

- 高性能计算

- 在GPU/FPGA加速卡中延长有效传输距离

- 配合SN75LVPE5412解复用器构建双向中继系统

- 存储系统

- SAS/SATA接口的信号调理

- 存储控制器与JBOD间的长距离传输

四、设计注意事项

- PCB布局建议

- VCC引脚需通过低阻抗路径连接电源平面

- 裸露焊盘(EP)建议采用过孔阵列接地

- 高速信号线长度匹配公差±20ps

- 电源设计

- 建议使用π型滤波器(10μF+0.1μF)

- 供电斜坡时间需控制在100ms以内

- 散热管理

- 结至环境热阻26.1°C/W(4层板)

- 建议电源层铜箔面积≥15mm²

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

详解SN65LVPE501:PCIe信号调理的得力助手2025-12-24 457

-

SN75LVPE801:8.0Gbps SATA Express均衡器和转接驱动器的卓越之选2025-12-19 463

-

SN75LVPE4410:高性能PCIe线性驱动器的设计指南2025-12-17 575

-

SN75LVPE3410:四通道PCI - Express 3.0线性转接驱动器的深度剖析2025-12-16 466

-

电子工程师的SN75LVPE3101设计指南2025-12-15 1054

-

PCIe 5.0信号调理技术解析:基于DS320PR412-421EVM评估模块的设计实践2025-09-23 1053

-

DS320PR1601 PCIe 5.0 32Gbps线性转接驱动器技术解析与应用指南2025-08-21 1129

-

SN75LVPE3410四通道PCIe线性转接驱动器技术解析与应用指南2025-08-19 1046

-

Texas Instruments SN75LVPE3101双通道PCIe 3.0线性转接驱动器数据手册2025-07-16 880

-

SN75LVPE4410四通道PCI Express 4.0线性再驱动器数据表2024-07-02 608

-

SN75LVPE3410四通道PCI-Express 3.0线性转接驱动器数据表2024-06-21 603

全部0条评论

快来发表一下你的评论吧 !