SN74LV8T541 八路缓冲器/驱动器技术文档总结

描述

输入采用降低阈值电路设计,以在电源电压大于输入电压时支持向上转换。此外,当输入电压大于电源电压时,5V 容差输入引脚可实现下平移。输出电平始终以电源电压 (VCC) 为基准,支持 1.8V、2.5V、3.3V 和 5V CMOS 电平。

*附件:sn74lv8t541.pdf

特性

- 1.65V 至 5.5V 的宽工作范围

- 5.5V 容差输入引脚

- 单电源电压转换器(参见LVxT增强型输入电压):

- 向上翻译:

- 1.2V 至 1.8V

- 1.5V至2.5V

- 1.8V 至 3.3V

- 3.3V 至 5.0V

- 下译:

- 5.0V、3.3V、2.5V 至 1.8V

- 5.0V、3.3V 至 2.5V

- 5.0V 至 3.3V

- 向上翻译:

- 高达 150Mbps(5V 或 3.3V VCC)

- 支持标准功能引脚排列

- 闩锁性能超过250mAper JESD 17

参数

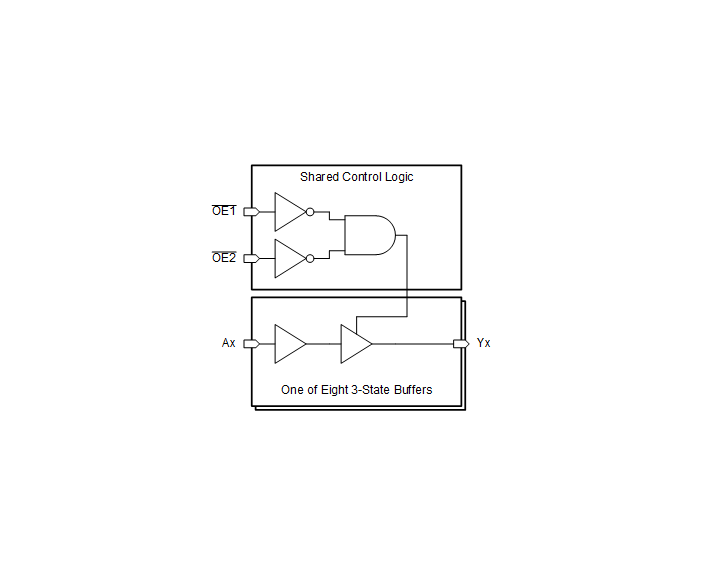

方框图

1. 核心特性

- 宽电压工作范围:1.65V至5.5V,支持多电压电平转换(上/下转换)。

- 5.5V耐压输入:兼容高压信号输入,集成电压电平平移功能。

- 高速传输:最高150Mbps(5V或3.3V供电时)。

- 3态输出:通过双低电平使能引脚(OE1、OE2)控制,增强总线兼容性。

- 低功耗设计:基于CMOS技术,静态电流极低。

2. 关键应用场景

- 数字标牌:驱动长距离信号传输。

- 微控制器扩展:增加I/O端口数量。

- LED控制:提供稳定的驱动电流。

- 电压电平转换:解决不同逻辑电平器件间的通信问题(如1.8V↔5V)。

3. 功能描述

- 8通道缓冲器:输入通过降低阈值电路支持上变频,输出电平始终参考VCC。

- 使能逻辑:仅当OE1和OE2均为低电平时,输出激活。

- 保护机制:集成钳位二极管,防止ESD损坏。

4. 电气参数

- 绝对最大额定值:供电电压≤7V,输入/输出电压≤5.5V。

- 开关特性:传输延迟典型值5.3ns(1.8V供电时),随负载电容增加而升高。

- 热性能:VQFN封装热阻θJA为90.4°C/W。

5. 封装选项

| 封装类型 | 引脚数 | 尺寸(长×宽) | 适用场景 |

|---|---|---|---|

| TSSOP (PW) | 20 | 6.5mm×4.4mm | 高密度PCB |

| VQFN (RKS) | 20 | 4.5mm×2.5mm | 空间受限设计 |

6. 设计注意事项

- 布局建议:添加0.1μF去耦电容靠近VCC引脚,避免90°走线。

- 未使用引脚处理:输入需上拉/下拉(推荐10kΩ),输出可悬空。

- 负载限制:容性负载≤50pF,阻性负载需满足RL≥VO/IO。

7. 文档支持

- 包含详细引脚配置、时序图、典型应用电路及热性能曲线。

- 提供JEDEC标准ESD防护指南(HBM 2000V,CDM 1000V)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

SN74LV8T541-Q1 汽车级八路缓冲器/驱动器技术文档摘要2025-09-28 903

-

SN74LV541A:2-5.5V八路3态缓冲器/驱动器技术解析2025-09-02 1347

-

Texas Instruments SN74LV240A八路缓冲器/驱动器数据手册2025-07-15 954

-

具有三态输出的汽车类八路缓冲器/驱动器SN74LV541A-Q1数据表2024-05-23 526

-

具有三态输出的八路缓冲器/驱动器SN74LV541A数据表2024-04-29 582

-

八路缓冲器/线路驱动器;三态-74LV541AT2023-03-03 628

-

八路缓冲器/线路驱动器;三态-74ALVC541_Q1002023-02-16 650

-

八路缓冲器/线路驱动器;三态-74LV244_Q1002023-02-15 536

全部0条评论

快来发表一下你的评论吧 !