SN74LV8T373-Q1 汽车级八路D型锁存器技术文档总结

描述

SN74LV8T373-Q1 包含八个 D 型锁存器。所有通道共享一个锁存使能 (LE) 输入和输出使能 (OE) 输入。

输入采用降低阈值电路设计,以在电源电压大于输入电压时支持向上转换。此外,当输入电压大于电源电压时,5V 容差输入引脚可实现下平移。输出电平始终以电源电压 (VCC) 为基准,支持 1.8V、2.5V、3.3V 和 5V CMOS 电平。

*附件:sn74lv8t373-q1.pdf

特性

- 符合 AEC-Q100 标准,适用于汽车应用:

- 器件温度等级 1:-40°C 至 +125°C

- 设备 HBM ESD 分类 2 级

- 设备 CDM ESD 分类级别 C4B

- 提供可润湿侧翼 QFN 封装

- 1.65V 至 5.5V 的宽工作范围

- 5.5V 容差输入引脚

- 单电源电压转换器(参见LVxT增强型输入电压):

- 向上翻译:

- 1.2V 至 1.8V

- 1.5V至2.5V

- 1.8V 至 3.3V

- 3.3V 至 5.0V

- 下译:

- 5.0V、3.3V、2.5V 至 1.8V

- 5.0V、3.3V 至 2.5V

- 5.0V 至 3.3V

- 向上翻译:

- 高达 150Mbps(5V 或 3.3V VCC)

- 支持标准功能引脚排列

- 闩锁性能超过250mAper JESD 17

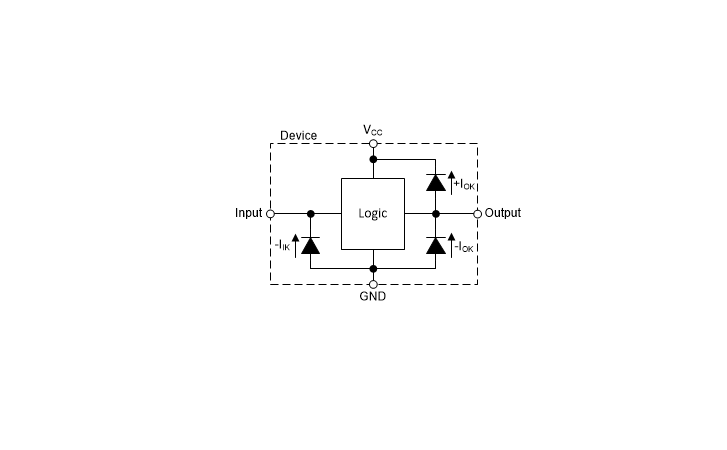

方框图

1. 产品概述

- 型号:SN74LV8T373-Q1,符合AEC-Q100汽车级认证(工作温度-40°C至125°C)。

- 功能:集成8路D型锁存器,支持电平转换,共享锁存使能(LE)和输出使能(OE)控制。

- 关键特性:

- 宽电压范围:1.65V至5.5V,支持5.5V耐压输入。

- 电平转换能力:支持上下行电压转换(如1.8V↔5V、3.3V↔5V等)。

- 高速传输:最高150Mbps(5V/3.3V供电时)。

- 封装选项:TSSOP(PW)、VSSOP(DGS)、VQFN(RKS,含可润湿侧翼)。

2. 电气特性

- 电源电流:静态电流低至0.2µA(典型值),动态电流随输入电压变化(见图5-1至5-3)。

- 输入/输出电平:

- 输入高电平(VIH)最低1.1V(1.65V供电时),支持低电压信号输入。

- 输出驱动能力:±8mA至±25mA(不同供电电压下)。

- ESD防护:HBM 2kV,CDM 1kV。

3. 功能模式

- 锁存控制:

- LE=高电平时,数据从D端透明传输至Q端。

- LE=低电平时,Q端保持最后锁存状态。

- 输出控制:

- OE=低电平时,输出有效;OE=高电平时,输出高阻态。

- 上电状态:通过内部POR电路确保上电时输出为已知低电平。

4. 典型应用

- 场景:并行数据存储、数字总线缓冲(见图8-1)。

- 设计要点:

- 电源需满足快速上升时间(6µs/V至100ms/V)。

- 未用输入需通过上拉/下拉电阻(推荐10kΩ)固定电平。

- 输出负载电容建议≤50pF以保证时序性能。

5. 封装与布局

- 封装尺寸:最小为VQFN(4.5mm×2.5mm),含可润湿侧翼便于AOI检测。

- 热性能:VQFN封装热阻θJA=90.4°C/W,需注意散热设计。

6. 安全与兼容性

- 绝对最大额定值:输入电压范围-0.5V至7V,避免超出以免损坏器件。

- 钳位二极管:输入含负向钳位二极管,输出含双向钳位二极管。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

SN74LV8T541-Q1 汽车级八路缓冲器/驱动器技术文档摘要2025-09-28 975

-

SN74HCS373 Octal透明锁存器技术解析与应用指南2025-09-24 1137

-

SN74ACT573八路D型透明锁存器技术解析与应用指南2025-09-04 1409

-

SN74AC373-EP八路D型透明锁存器数据表2024-06-04 508

-

具有三态输出的八路透明 D 类锁存器SN74LV373A-Q1数据表2024-05-23 580

-

具有施密特触发输入和三态输出的 SN74HCS373-Q1 汽车类八路透明D型锁存器数据表2024-05-13 436

-

具有三态输出的八路透明 D 类锁存器SN74LV373A数据表2024-05-11 620

-

具有施密特触发输入和三态输出的 SN74HCS373八路透明D型锁存器数据表2024-05-08 630

-

具有三态输出的汽车级八路D型透明锁存器SN74ACT573-Q1数据表2024-04-30 517

-

八路D型透明锁存器;三态-74AHC3732023-02-20 637

-

八路D型透明锁存器;三态-74HC_HCT573_Q1002023-02-17 626

-

八路D型透明锁存器;三态-74ALVC3732023-02-16 646

-

八路D型透明锁存器;三态-74HC_HCT3732023-02-15 631

全部0条评论

快来发表一下你的评论吧 !