ZL40294B:面向PCIe Gen6的超低附加抖动时钟扇出缓冲器

描述

Microchip Technology ZL40294B 1至20个扇出缓冲器是超低附加抖动、低功耗缓冲器,完全符合Intel DB2000QL标准。ZL40294B的工作电压为3.3V ±5%,支持PCIe Gen 5.0和Gen 6.0规格。

数据手册:*附件:Microchip Technology ZL40294B 1至20个扇出缓冲器数据手册.pdf

Microchip Technology ZL40294B 缓冲器提供12kHz至20MHz的附加相位抖动,抖动频率为32fs,典型频率为156.25MHz。这些设备的工作温度范围为-40°C至+85°C。ZL40294B非常适合PCI Express第1/2/3/4/5/6代时钟分配、服务器、存储器和数据中心。

特性

- 完全符合Intel DB2000QL规格

- 20个低功耗推挽HCSL PCIe输出

- 支持PCIe Gen 5.0和Gen 6.0规范

- 在DB2000QL频带中,典型值为12fs的超低附加抖动

- PCIe Gen 6典型值为4fs RMS的附加相位抖动

- 12kHz至20MHz的附加相位抖动,典型值为32fs,频率为156.25MHz

- 支持0 MHz至250 MHz的时钟频率

- 支持3.3 V电源

- 内置低压差 (LDO) 稳压器,具有出色的电源噪声抑制能力

- 最大输出至输出偏移:50ps

- SMBus接口

- 侧带接口 (SBI)

- 八个OE引脚

- 85Ω差分传输线的嵌入式系列端接电阻器

- 对扩频时钟透明

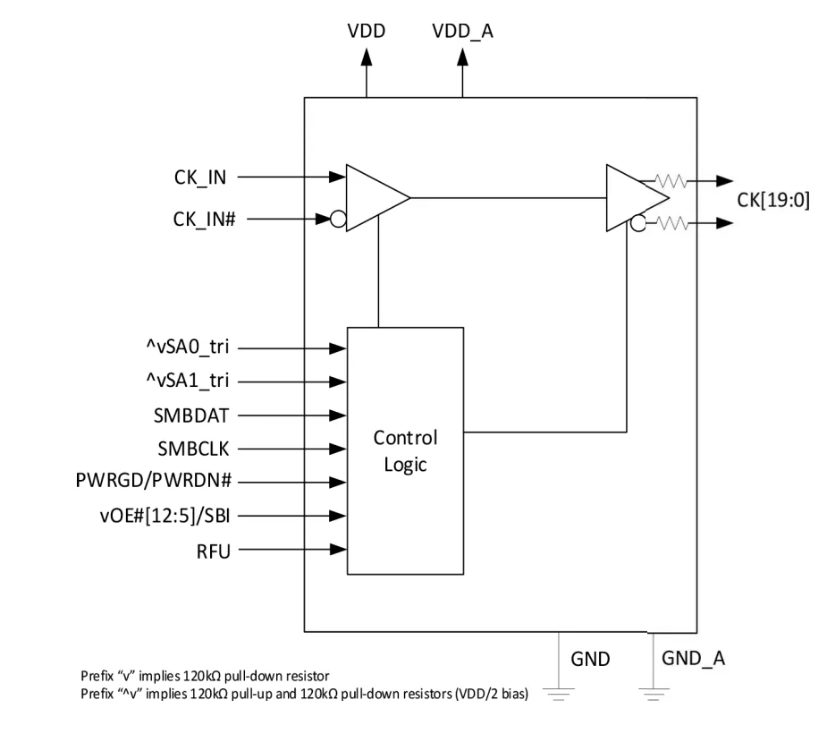

功能框图

ZL40294B:面向PCIe Gen6的超低附加抖动时钟扇出缓冲器

一、关键特性概览

ZL40294B具备以下突出特性:

- 全面兼容性 :支持PCIe Gen1至Gen6,符合Intel DB2000QL标准。

- 高扇出能力 :提供20路低功耗推挽HCSL输出,支持0 MHz至250 MHz的时钟频率。

- 超低附加抖动 :

- 典型值12 fs(DB2000QL频段)

- PCIe Gen6附加相位抖动典型值仅为4 fs RMS

- 灵活的电源设计 :支持3.3V电源,内置LDO提供优异的电源噪声抑制。

- 多种控制接口 :支持SMBus和边带接口(SBI),提供硬件和软件两种输出使能方式。

- 集成终端电阻 :每路输出均集成85Ω差分终端电阻,节省外部元件。

二、典型应用场景

ZL40294B适用于以下高性能系统:

- 多路PCIe时钟分配 (如服务器中的GPU、NVMe、网卡等)

- Intel QPI/UPI互联时钟分发

- 数据中心与存储设备

- 网络交换机与路由器

其高扇出能力和低抖动特性使其成为多CPU服务器和高速通信设备的理想时钟缓冲解决方案。

三、核心技术优势

1. 超低附加抖动性能

ZL40294B在多种频率和带宽条件下均表现出优异的抖动性能:

- 在12 kHz至20 MHz带宽内,典型附加抖动为32 fs(156.25 MHz时钟)

- 支持PCIe Gen6的严格时序要求,附加抖动低至4 fs RMS

- 即使在输入时钟质量较差(如800 mV差分电压、1.5 V/ns摆率)的情况下,仍能保持优良的抖动性能

2. 灵活的输入与输出配置

- 输入支持 :支持差分或单端输入,频率范围0–250 MHz,具备广泛的兼容性。

- 输出控制 :

- 8个硬件OE#引脚,支持异步输出使能

- SMBus寄存器控制,可独立配置每路输出

- 边带接口(SBI)支持硬件级串行控制,适用于高可靠性系统

3. 电源噪声抑制与节能设计

- 内置LDO稳压器,提供优异的电源噪声抑制能力

- 支持电源管理模式(PWRDN#),在非活动状态下功耗显著降低

- 每路电源引脚(VDD、VDDA)均推荐使用0.1 μF去耦电容,进一步提升噪声免疫力

4. 封装与热管理

ZL40294B采用80引脚VGQFN封装(6 mm × 6 mm),底部带有2.8 mm × 2.8 mm的散热焊盘,具有良好的热性能。在静止空气中,结到环境的热阻(θJA)为32.42°C/W,适合高密度板级布局。

四、控制与配置灵活性

1. SMBus接口

- 支持标准字节读写和块读写操作

- 可通过三电平地址引脚(SA0_tri、SA1_tri)配置9个不同的设备地址

- 提供实时状态回读功能,便于系统监控与诊断

2. 边带接口(SBI)

- 3线串行接口(vDATA、vCLK、vSHFT_LD#)

- 支持星型或链式拓扑,便于多设备协同控制

- 可通过SMBus屏蔽寄存器防止误关闭关键输出

3. 输出使能优先级

输出使能由以下三者共同决定:

- OE#引脚状态(低电平有效)

- SMBus输出使能位(高电平有效)

- SBI移位寄存器值(需通过SBEN引脚使能)

任一条件不满足时,输出将被禁用,确保系统安全。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

深入解析LMK00105:超低抖动LVCMOS扇出缓冲器与电平转换器2026-02-09 300

-

ZL30291B:面向PCIe Gen6与平台时序的高性能时钟发生器2025-09-28 968

-

CDCDB800/803超低附加抖动、8路输出PCIe Gen1至Gen5时钟缓冲器2024-11-26 462

-

核芯互联推出符合DB2000QL及PCIe Gen5和Gen 6标准的低抖动时钟缓冲器CLB20002023-06-08 2995

-

GRANDMICRO有容微电子GM50101:超低附加抖动时钟缓冲器2023-03-02 2001

-

如何测量扇出缓冲器中的附加抖动2022-11-21 662

-

测量扇出缓冲器中的附加抖动2022-11-04 693

-

超低附加抖动时钟缓冲器的主要技术特点2022-05-07 2239

-

瑞萨电子推符合PCIe Gen6时钟缓冲器和多路复用器2022-04-15 2397

-

瑞萨电子推出符合PCIe Gen6标准的时钟缓冲器和多路复用器2022-04-14 3180

-

测量扇出缓冲器中的附加抖动怎么计算?2021-05-06 1242

-

扇出缓冲器中的附加抖动测量2018-09-13 1599

全部0条评论

快来发表一下你的评论吧 !