SN74LVC595A 8位移位寄存器技术文档总结

描述

SN74LVC595A器件包含一个8位串行输入、并联输出移位寄存器,该寄存器为8位D型存储寄存器供电。存储寄存器具有并行的 3 态输出。为移位寄存器和存储寄存器提供了单独的时钟。移位寄存器具有直接覆盖清除 (SRCLR) 输入、串行 (SER) 输入和用于级联的串行输出。当输出使能(OE)输入为高电平时,除QH′外的所有输出均处于高阻抗状态。

*附件:sn74lvc595a.pdf

特性

- 工作范围为 1.1V 至 3.6V

- 过压容限输入支持高达 5.5V,独立于 VCC

- 支持部分断电,带反向驱动器保护 (Ioff)

- 高推挽输出驱动强度:

- 3.3V 时为 ±24mA

- 2.3V时为±8mA

- 1.65V时为±4mA

- 闩锁性能超过250mAper JESD78

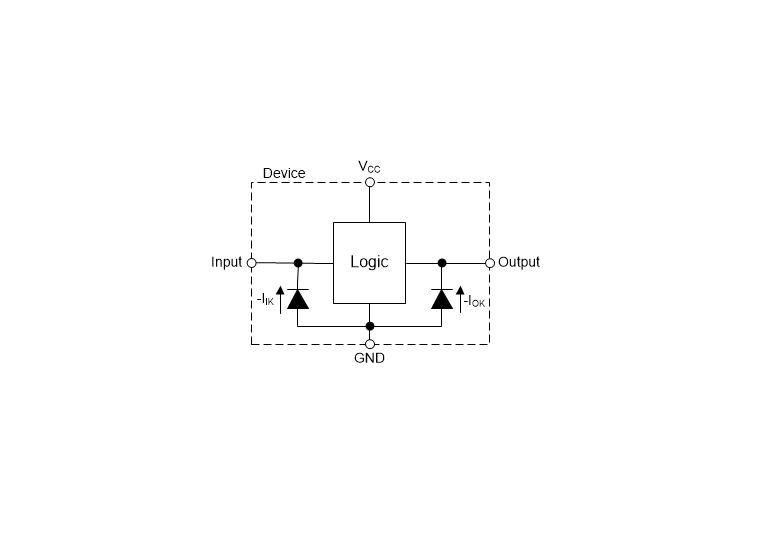

方框图

1. 核心功能

SN74LVC595A是一款8位串行输入、并行输出的移位寄存器,集成8位D型存储寄存器,具有三态输出功能。关键特性包括:

- 电压范围:1.1V至3.6V工作电压,输入支持5.5V过压容限。

- 驱动能力:高推挽输出强度(±24mA@3.3V,±8mA@2.3V,±4mA@1.65V)。

- 保护特性:支持部分断电模式(Ioff)和抗闩锁性能(>250mA)。

2. 应用场景

- 网络交换机

- 电源基础设施

- LED显示屏

- 服务器控制

3. 引脚与逻辑控制

- 关键引脚:

- SER(串行输入)、SRCLK(移位寄存器时钟)、RCLK(存储寄存器时钟)。

- OE(输出使能,低电平有效),SRCLR(移位寄存器清零,低电平有效)。

- 输出模式:QA-QH为并行输出,QH'为级联串行输出(始终有效)。

4. 电气特性

- 绝对最大额定值:电源电压6.5V,输入/输出电压6.5V,ESD防护(HBM±2kV,CDM±1kV)。

- 动态性能:

- 传播延迟(RCLK→QA-QH):3.4ns@3.3V,18.2ns@1.8V。

- 输出使能时间(OE→QA-QH):3.5ns@3.3V。

5. 封装选项

- TSSOP-16(5.0mm×4.4mm)

- WQFN-16(3.5mm×2.5mm)

6. 设计注意事项

- 输入处理:未用输入需接VCC或GND,避免浮空。

- 输出负载:电容≤50pF,电阻需满足VO/IO限制。

- 热管理:结温不超过150°C,建议布局时添加去耦电容。

7. 典型应用电路

用于驱动七段显示器,通过级联减少GPIO占用(仅需4个控制信号)。上电时需通过SRCLR初始化移位寄存器,OE可连接PWM调节亮度。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

74AHCT595F:8位移位寄存器的特性与应用解析2026-03-16 528

-

SN74HCT595 8位移位寄存器技术解析与应用指南2025-09-19 1215

-

SN74LV595B-EP低噪声8位移位寄存器技术解析与应用指南2025-08-15 1422

-

SN74HC595-EP带3态输出寄存器的8位移位寄存器数据表2024-06-04 604

-

带3态输出寄存器的8位移位寄存器SN74AHC595数据表2024-05-20 490

-

具有三态输出寄存器的 SN74HCT595 8位移位寄存器数据表2024-05-15 564

-

具有三态输出寄存器的 SN74HCT595-Q1 汽车类8位移位寄存器数据表2024-05-11 611

-

具有三态输出寄存器的SN74LV595A 8位移位寄存器数据表2024-05-07 415

-

带输出寄存器的8位移位寄存器-74LVC594A_Q1002023-02-17 631

-

74HC595的8位移位寄存器的基本知识2022-10-19 893

全部0条评论

快来发表一下你的评论吧 !