TDA4VP-Q1处理器技术文档总结

描述

TDA4VH-Q1 TDA4AH-Q1 TDA4VP-Q1 TDA4AP-Q1 处理器系列基于进化的 Jacinto™ 7 架构,面向 ADAS 和自动驾驶汽车 (AV) 应用,并建立在 TI 十多年来在 ADAS 处理器市场领导地位积累的广泛市场知识之上。TDA4VH-Q1 TDA4AH-Q1 TDA4VP-Q1 TDA4VP-Q1 TDA4AP-Q1 TDA4AP-Q1 器件的独特组合高性能计算、深度学习引擎、信号和图像处理专用加速器非常适合多种成像、视觉、雷达、传感器融合和 AI 应用,例如:机器人、移动机械、非公路车辆控制器、机器视觉、AI BOX、网关、零售自动化、 医学成像,等等。TDA4VH-Q1、TDA4AH-Q1、TDA4VP-Q1、TDA4AP-Q1 以行业领先的功率/性能比为传统和深度学习算法提供高性能计算,并具有高水平的系统集成度,可为支持集中式 ECU 或独立传感器中多种传感器模式的高级汽车平台实现可扩展性和降低成本。关键内核包括具有标量和矢量内核的下一代 DSP、专用深度学习和传统算法加速器、用于通用计算的最新 Arm 和 GPU 处理器、集成的下一代成像子系统 (ISP)、视频编解码器、以太网集线器和隔离的 MCU 岛。所有这些都受到汽车级安全和安保硬件加速器的保护。

*附件:tda4vp-q1.pdf

关键性能核心概述

“C7x”下一代 DSP 将 TI 业界领先的 DSP 和 EVE 内核组合到一个更高性能的内核中,并增加了浮点矢量计算功能,从而向后兼容遗留代码,同时简化软件编程。新型“MMAv2”深度学习加速器的单个实例可在 125°C 的典型汽车最坏结温下运行时,在业界最低的功耗范围内实现高达 8 TOPS 的性能。 专用的ADAS/AV硬件加速器提供视觉预处理以及距离和运动处理,而不会影响系统性能。

常规计算核心和集成概述

Arm Cortex-A72 的独立八核集群配置促进了多作系统应用,而对软件管理程序的需求极低。八个 Arm® Cortex-R5F® 子系统支持低级、时序关键的处理任务,使 Arm® Cortex-A72® 不受应用的阻碍。集成的 IMG BXS-4-64 GPU 提供高达 50 GFLOPS,可实现动态 3D 渲染,以增强观看应用。TI 的第 7 代 ISP 以现有的世界级 ISP 为基础,具有处理更广泛传感器套件的灵活性、对更高位深度的支持以及针对分析应用的功能。集成的诊断和安全功能支持高达 ASIL-D/SIL-3 级别的作,而集成的安全功能可保护数据免受现代攻击。为了支持需要大量数据带宽的系统,包括一个 PCIe 集线器和千兆以太网交换机以及 CSI-2 端口,以支持许多传感器输入的吞吐量。为了进一步集成,TDA4VH-Q1、TDA4AH-Q1、TDA4VP-Q1、TDA4AP-Q1 系列还包括一个 MCU 岛,无需外部系统微控制器。

特性

处理器内核:

多达 4 个 C7x 浮点、矢量 DSP、高达 1.0 GHz、320 GFLOPS、1024 GOPS

多达四个深度学习矩阵乘法加速器 (MMAv2),在 1.0 GHz 时高达 32 TOPS (8b)

两个视觉处理加速器 (VPAC),带图像信号处理器 (ISP) 和多个视觉辅助加速器

深度和运动处理加速器 (DMPAC)

8 个 Arm Cortex-A72 微处理器子系统,频率高达 2.0 GHz

- 每个四核 Cortex-A72 集群 2MB 共享 L2 缓存

- 每个 Cortex-A72 内核 32KB L1 DCache 和 48KB L1 ICache

8 个 Arm Cortex-R5F MCU,频率高达 1.0 GHz

- 16K I-Cache、16K D-Cache、64K L2 TCM

- 隔离式 MCU 子系统中的两个 Arm Cortex-R5F MCU

- 通用计算分区中的六个 Arm Cortex-R5F MCU

GPU IMG BXS-4-64,256kB 缓存,高达 800 MHz,50 GFLOPS,4 GTexels/s

定制设计的互连结构,支持接近最大处理授权内存子系统:

高达 8MB 的片上 L3 RAM,具有 ECC 和一致性

- ECC 错误保护

- 共享相干缓存

- 支持内部 DMA 引擎

多达四个带 ECC 的外部存储器接口 (EMIF) 模块

- 支持 LPDDR4 内存类型

- 支持高达 4266 MT/s 的速度

- 多达 4x32-b 总线,内联 ECC 速度高达 68 GB/s

通用内存控制器 (GPMC)

主域中的 3x512KB 片上 SRAM,受 ECC 保护功能安全:

符合功能安全标准(在特定部件号上)

- 专为功能安全应用而开发

- 提供文档,以帮助 ISO 26262 功能安全系统设计,最高可达 ASIL-D/SIL-3 目标

- 系统能力高达 ASIL-D/SIL-3 靶向

- 硬件完整性高达 ASIL-D/SIL-3,适用于 MCU 域

- 硬件完整性高达 ASIL-B/SIL-2,针对主域

- 硬件完整性高达 ASIL-D/SIL-3,适用于主域的扩展 MCU (EMCU) 部分

- 安全相关认证

- 计划通过 ISO 26262

AEC-Q100 符合以 Q1 结尾的部件号变体设备安全性(在特定部件号上):

具有安全运行时支持的安全启动

客户可编程根密钥,最高可达 RSA-4K 或 ECC-512

嵌入式硬件安全模块

加密硬件加速器 – 具有 ECC、AES、SHA、RNG、DES 和 3DES 的 PKA高速串行接口:

集成以太网交换机,支持多达 8 个 (TDA4xH) 或 4 个 (TDA4xP) 外部端口

- 两个端口支持 5Gb、10Gb USXGMII/XFI

- 所有端口均支持 1Gb、2.5Gb SGMII

- 所有端口均可支持 QSGMII。最多可以启用 2 个 (TDA4xH) 或 1 个 (TDA4xP) QSGMII,并使用所有 8 或 4 个内部通道

多达 4x2-L/2x4L (TDA4xH) 或 2x2L/1x4L (TDA4xP) PCI-Express (PCIe) Gen3 控制器

- 具有自动协商功能的 Gen1 (2.5GT/s)、Gen2 (5.0GT/s) 和 Gen3 (8.0GT/s)作

一个 USB 3.0 双角色设备 (DRD) 子系统

- 增强型 SuperSpeed Gen1 端口

- 支持Type-C切换

- 可独立配置为 USB 主机、USB 外设或 USB DRD

三个 CSI2.0 4L 接收器和两个 CSI2.0 4L TX以太网:

两个 RGMII/RMII 接口汽车接口:

20 个模块化控制器局域网 (MCAN) 模块,完全支持 CAN-FD显示子系统:

两个 DSI 4L TX(高达 2.5k)

一个 eDP/DP 接口,支持多显示器 (MST)

一个 DPI音频接口:

五个多通道音频串行端口 (MCASP) 模块视频加速:

H.264/H.265 编码/解码,高达 960MP/s (TDA4xH) 或 480MP/s (TDA4xP)闪存接口:

嵌入式多媒体卡接口 (eMMC™ 5.1)

一个安全数字 3.0 / 安全数字输入输出 3.0 接口 (SD3.0/SDIO3.0

具有两个通道的通用闪存 (UFS 2.1) 接口

两个独立的闪存接口配置为

- 一个 OSPI 或 HyperBus™ 或 QSPI 闪存接口,以及

- 一个 QSPI 闪存接口

片上系统 (SoC) 架构:

16纳米FinFET技术

31 mm × 31 mm、0.8 mm 间距、1414 引脚 FCBGA (ALY),支持 IPC 3 类 PCB 布线TPS6594-Q1配套电源管理IC (PMIC):

功能安全支持高达 ASIL-D

灵活的映射以支持不同的用例

参数

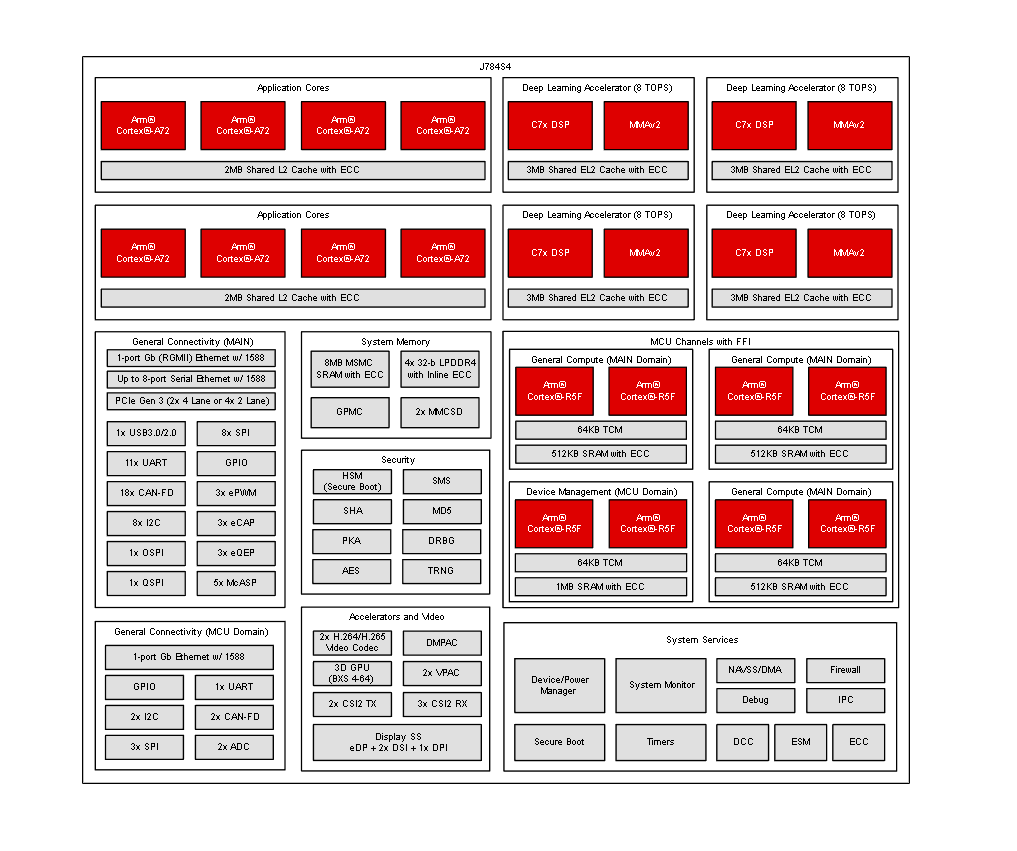

方框图

1. 产品概述

- 产品系列:TDA4VH-Q1、TDA4AH-Q1、TDA4VP-Q1、TDA4AP-Q1

- 架构:基于Jacinto™ 7架构,专为ADAS和自动驾驶车辆(AD)应用设计

- 工艺:16nm FinFET技术

- 封装:31mm × 31mm,0.8mm间距,1414引脚FCBGA(ALY)封装

2. 主要特性

处理器核心

- Cortex-A72:最多8核,最高2.0GHz

- Cortex-R5F:最多8核,最高1.0GHz

- C7x DSP:最多4核,最高1.0GHz,320GFLOPS,1024GOPS

- MMAv2加速器:最多4个,最高32TOPS(8b)@1.0GHz

专用加速器

- VPAC:2个视觉处理加速器(含ISP)

- DMPAC:深度和运动处理加速器

- GPU:IMG BXS-4-64,最高800MHz,50GFLOPS

- 视频编解码:H.264/H.265,最高960MP/s(TDA4xH)或480MP/s(TDA4xP)

内存子系统

- 片上RAM:8MB L3 RAM(带ECC)

- 外部内存:支持4个LPDDR4接口,最高4266MT/s,68GB/s带宽

功能安全

- 符合ISO 26262标准,最高支持ASIL-D/SIL-3

- AEC-Q100认证(Q1变体)

安全特性

- 安全启动

- 硬件安全模块

- 加密加速器(AES, SHA, ECC等)

3. 接口资源

高速串行接口

- 以太网:支持8(TDA4xH)或4(TDA4xP)个外部端口,最高10GbE

- PCIe:最多4x2L/2x4L Gen3控制器

- USB:1个USB 3.0 DRD

- CSI-2:3个4L RX + 2个4L TX

显示接口

- DSI:2个4L TX

- eDP/DP:1个接口

- DPI:1个接口

其他接口

- CAN-FD:20个模块

- MCASP:5个音频接口

- UART:12个

- SPI/I2C:多个

4. 应用领域

- 高级环视和泊车辅助系统

- 自动驾驶传感器融合(摄像头、雷达、LiDAR)

- 前视摄像头系统

- 下一代电子后视镜系统

- ADAS域控制器

5. 关键创新

- 结合高性能计算和深度学习引擎

- 专用视觉和信号处理加速器

- 功能安全合规架构

- 行业领先的能效比

- 高度集成的系统设计

该文档详细描述了处理器的功能特性、电气规格、引脚配置和系统架构,为汽车电子系统设计提供了全面的技术参考。

-

TDA4AL-Q1处理器的技术文档摘要2025-10-10 1918

-

TDA4VH-Q1处理器技术文档总结2025-10-08 5042

-

TDA4AP-Q1处理器技术文档的核心内容总结2025-09-29 4633

-

TDA4AH-Q1系列 用于传感器融合的汽车分析 SoC、带AI和视频编码器的L2、L3域控制器数据手册2025-04-15 1465

-

Jacinto处理器TDA4AP/TDA4VP/TDA4AH/TDA4VH EVM用户指南2024-11-15 686

-

适用于ADAS和自动驾驶汽车的TDA4VH-Q1、TDA4AH-Q1、TDA4VP-Q1、TDA4AP-Q1 Jacinto™ 处理器数据表2024-08-03 779

-

Jacinto7处理器摄像头接入和ISP的处理能力2022-11-03 1088

-

RK3399处理器与AR9201处理器有哪些不同之处呢2022-02-21 3540

-

32位处理器的开发与8位处理器的开发有哪些明显的不同?2021-04-19 2646

-

麒麟9000处理器和高通骁龙875处理器相比如何?2020-11-03 7149

-

Cortex-M4处理器的技术参考手册免费下载2019-10-08 2307

-

苹果a6处理器怎么样_a6处理器参数2012-09-13 26710

-

恩智浦获得ARM Cortex-M4处理器授权2010-03-03 1784

-

AMD Athlon 4处理器2010-01-22 1127

全部0条评论

快来发表一下你的评论吧 !