面向硅基产线:二维半导体接触电阻的性能优化

描述

随着硅基集成电路进入后摩尔时代,二维过渡金属硫化物(TMDCs,如MoS₂、WS₂)凭借原子级厚度、优异的开关特性和无悬挂键界面,成为下一代晶体管沟道材料的理想选择。然而,金属电极与二维半导体间的接触问题一直是制约其发展的核心障碍——接触电阻过高(>800 Ω·μm)、费米能级钉扎(FLP)效应严重、纳米尺度接触稳定性不足,难以满足先进工艺节点需求(IRDS标准要求总电阻≤220 Ω·μm)。本文通过结合TLM接触电阻测试仪对接触电阻的提取系统综述面向硅产线兼容的二维半导体接触工程技术,从性能指标、关键挑战到创新解决方案,为未来产业化提供路线图。

二维半导体接触性能的评价维度

/Xfilm

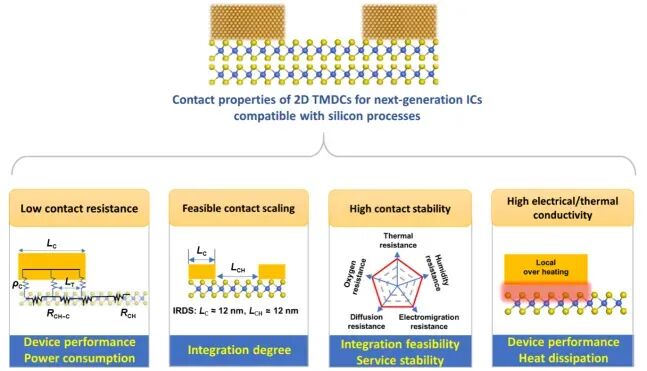

符合硅基工艺兼容性要求的二维TMDCs接触特性示意图

为匹配硅基工艺要求,论文提出多维度评价体系:

- 接触电阻(RC):衡量2D TMDCs与金属电极接触性能的关键指标,直接影响器件性能和功耗,主导器件功耗与驱动电流,需低于117 Ω·μm,常用的RC提取方法有Y函数法、四探针法和传输线法(TLM,目前最常用方法)。

- 接触尺寸微缩性:决定集成密度,需实现<12 nm接触长度(LC)且避免电流拥挤效应;

- 接触稳定性:需耐受后端工艺(BEOL)450℃退火及环境因素(氧化、湿气);

- 电/热导率:影响信号传输效率与散热;

- 工艺兼容性:支持8/12英寸晶圆级制造。

当前最优Y掺杂MoS₂总电阻235 Ω·μm,但仍高于硅基250 Ω·μm的标准,而传统Au接触MoS₂在LC缩至30nm时RC激增13倍,凸显优化必要性。

二维半导体接触的挑战

/Xfilm

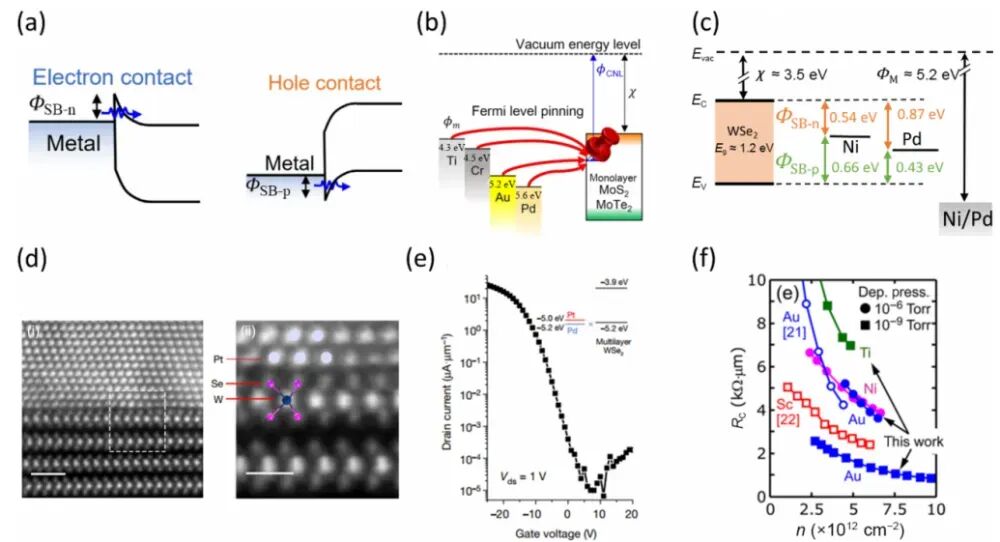

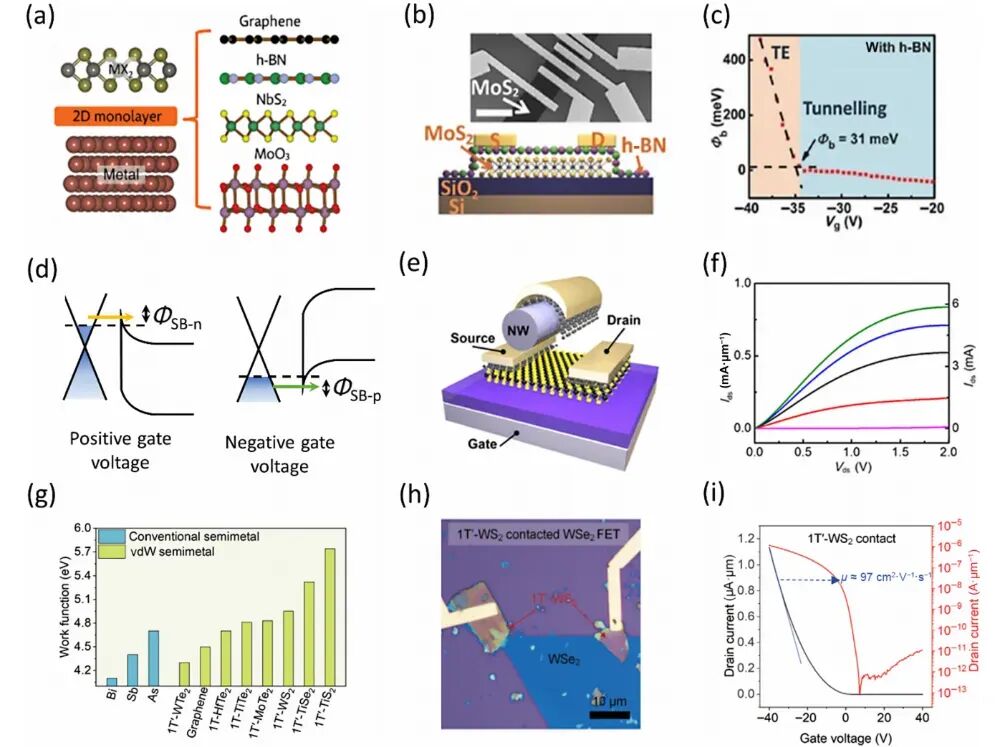

- 费米能级钉扎与非理想载流子注入

(a) 金属功函数调控载流子注入示意图;(b) FLP效应示意图;(c) Ni/Pd与WSe₂的实际能带对齐;(d) Pt/WSe₂原子分辨率图像;(e) Pt接触多层WSe₂的转移曲线;(f) 不同沉积压力下的RC对比

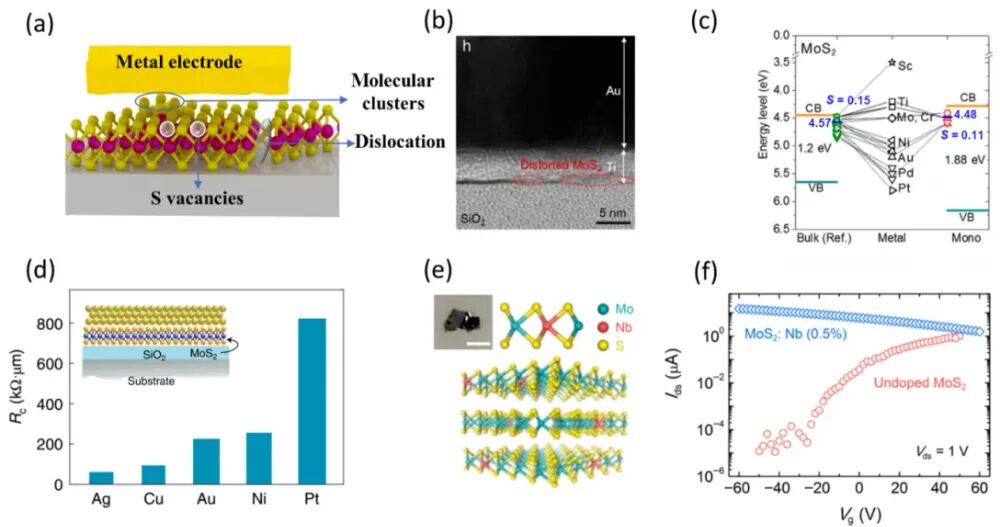

界面缺陷(硫空位、金属扩散)引发强烈FLP效应,使肖特基势垒高度(SBH)偏离理论值。例如Ti/MoS₂接触中,FLP导致实际SBH固定在0.15 eV附近,与金属功函数无关,电子注入效率降低60%。

- 超薄层掺杂困境

(a) 界面缺陷示意图;(b) Ti/Au电极沉积引起的MoS₂界面无序;(c) 不同金属电极与MoS₂的FLP效应;(d) 不同金属与MoS₂的vdW接触电阻;(e) Ni原子取代掺杂示意图;(f) Ni掺杂前后MoS₂晶体管的传输曲线

硅基重掺杂技术无法移植:离子注入破坏单层TMDCs晶格,掺杂浓度难超10¹³ cm⁻²;表面吸附掺杂(如K/NO₂)稳定性差,易在空气中失效。

- 尺寸微缩与稳定性矛盾

热稳定性:低熔点金属接触(Bi/In)RC可低至42 Ω·μm,但熔点<300℃,无法承受BEOL工艺;电化学稳定性:Ti/Ni电极易氧化,Cu扩散导致界面降解。

硅工艺兼容的接触工程突破

/Xfilm

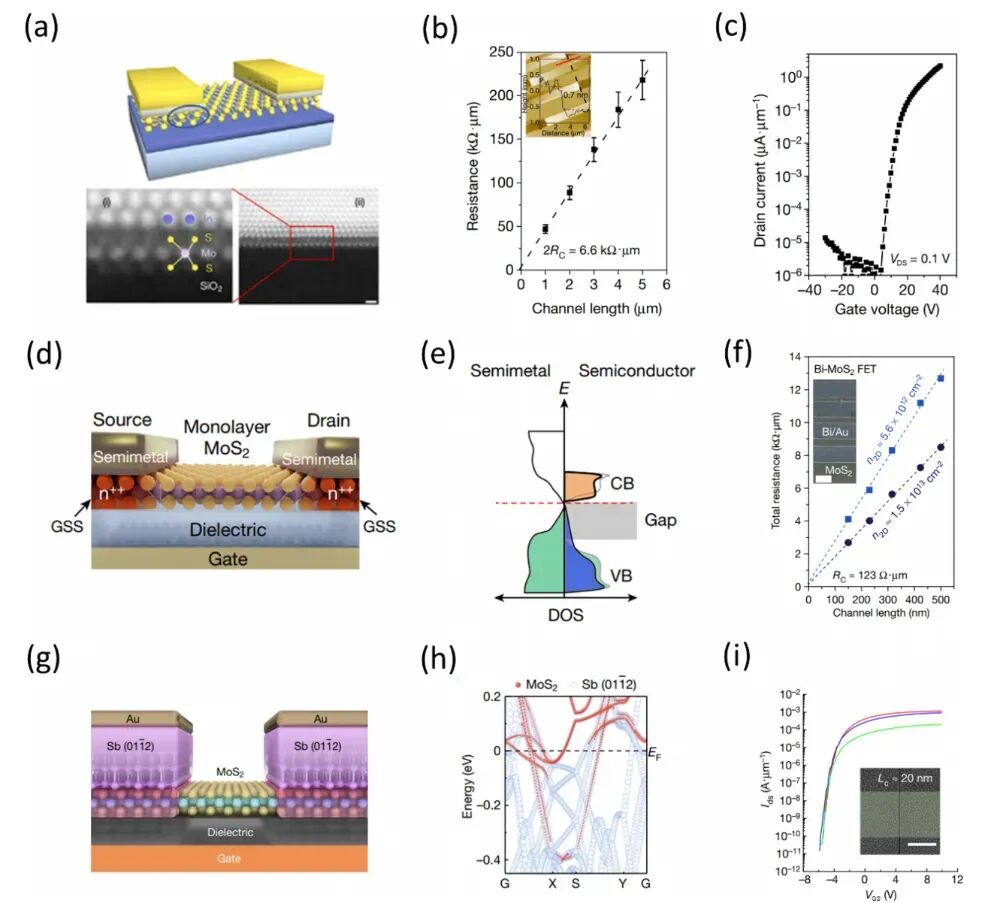

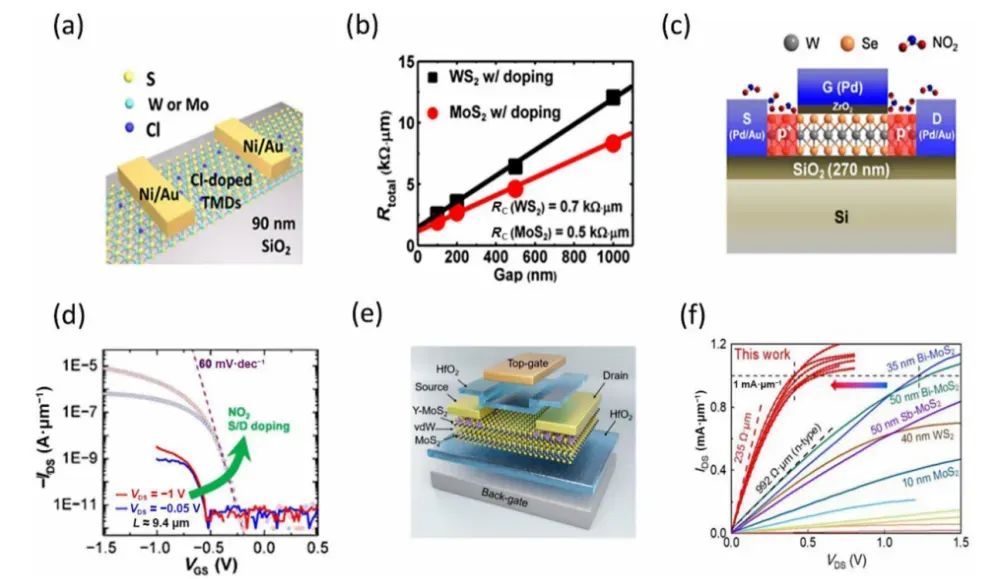

- 接触电阻优化

低熔点金属的vdW接触:(a) In/MoS₂vdW接触TEM图;(b) TLM提取RC;(c) MoS₂FET转移特性;(d) Bi接触MoS₂示意图;(e) 半金属-半导体态密度示意图;(f) Bi-MoS₂的TLM曲线;(g) Sb(01−12)接触示意图;(h) Sb-MoS₂能带结构;(i) 20nm LC器件的转移特性

范德华接触:通过转移金属电极或低温沉积低熔点金属(In、Bi),实现原子级锐利界面,避免FLP效应。Bi/MoS₂接触电阻RC仅123 Ω·μm,接近量子极限。

通过缓冲层优化RC:(a) 金属/缓冲层/MX₂结构示意图;(b) h-BN缓冲层器件SEM图;(c) h-BN厚度对SBH的调控;(d) 石墨烯接触能带对齐;(e) 石墨烯混合接触器件示意图;(f) 80nm MoS₂晶体管转移曲线;(g) 二维半金属功函数总结;(h) 1T'-WS₂接触WSe₂器件光学图;(i) 器件转移曲线

缓冲层工程:插入h-BN/石墨烯层抑制金属诱导间隙态(MIGS),使SBH从158 meV降至31 meV。

掺杂工程优化接触:(a) Cl掺杂示意图;(b) WS₂/MoS₂接触电阻;(c) NO₂掺杂示意图;(d) WSe₂掺杂前后转移曲线;(e) Y掺杂MoS₂晶体管示意图;(f) 亚50nm器件总电阻对比

相变掺杂:Y原子诱导MoS₂从半导体相(2H)向金属相(1T)转变,形成欧姆接触,总电阻235 Ω·μm且支持晶圆级加工。

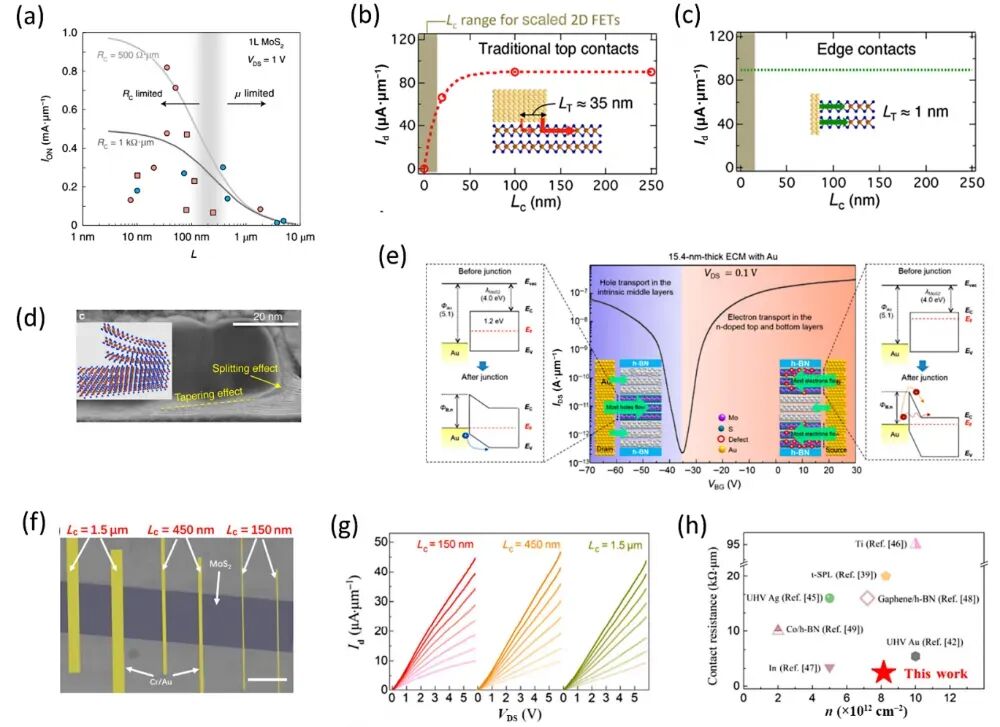

- 尺寸微缩:边缘接触的突破性进展

二维TMDCs边缘接触:(a) 接触电阻对器件性能的影响;(b,c) 边缘接触与顶部接触电流对比;(d) 二维材料分裂示意图;(e) 多层材料边缘载流子分离注入;(f) 单层MoS₂边缘接触器件;(g,h) 输出特性与RC值

传统顶接触在LC<100 nm时RC呈指数增长,而边缘接触通过侧向载流子注入规避该问题:氩等离子体刻蚀 MoS₂,Ni边缘接触实现 20 nm LC,电流密度达1.23 mA/μm( @1V );多层TMDCs边缘接触呈现双极传输特性,为互补逻辑设计提供新思路。

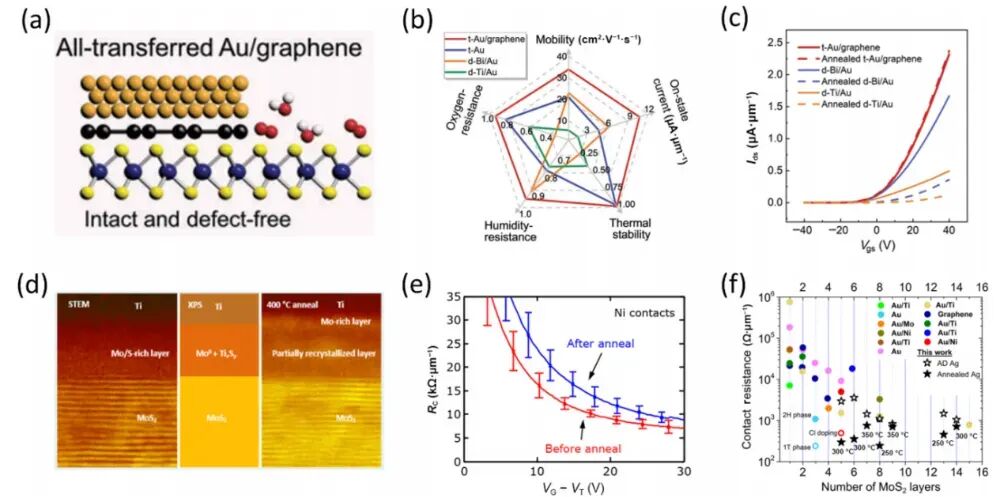

- 稳定性提升:高熔点材料与封装策略

接触界面稳定性优化:(a) 石墨烯全转移接触器件;(b) 器件综合特性;(c) 不同接触退火性能对比;(d) Ti高温扩散;(e) Ni接触退火前后RC变化;(f) Ag接触RC退火变化

合金电极:Sn/Au形成Au0.88Sn0.12(熔点521℃),将热预算提升至400℃;全范德华封装:石墨烯/Au电极在350℃退火后性能衰减<5%,远优于传统Ti/Au。接触电阻优化已逼近硅基水平:通过掺杂工程(Y/Cl)和半金属接触(Sb/Bi),成功将RC降低至42–235 Ω·μm,部分超越硅基节点标准。边缘接触技术更突破尺寸缩放极限,LC缩至5nm仍保持优异电学性能。下一步需重点解决热稳定性协同优化与晶圆级掺杂均一性问题,以满足后摩尔时代集成电路需求。

-

基于传输线模型(TLM)的特定接触电阻率测量标准化2025-10-23 2028

-

半导体欧姆接触工艺 | MoGe₂P₄实现超低接触电阻的TLM验证2025-09-29 1420

-

产线效率翻倍!二维码扫码器这样用就对了2025-04-18 813

-

中国科大实现耦合高度可调的二维硅基量子点阵列2024-12-03 1068

-

NFC和二维码扫描二合一的设备,用于产线数据采集2024-09-05 1306

-

太阳能电池接触电阻测试中的影响因素2024-01-14 2274

-

刘开辉教授课题组在12英寸二维半导体晶圆批量制备研究中取得进展2023-07-13 1542

-

二维半导体晶体管实际沟道长度的极限2022-10-17 4276

-

什么是接触电阻?怎么测试接触电阻?2021-03-17 5124

-

接触电阻是什么,接触电阻过大的原因是什么2021-01-28 14120

-

什么是接触电阻?2021-01-19 9987

-

接触电阻是什么意思_接触电阻过大的原因2019-08-01 28528

-

接触电阻原理及组成2010-04-16 5112

全部0条评论

快来发表一下你的评论吧 !