SOSET索斯特分享:无源晶振电路设计指南

描述

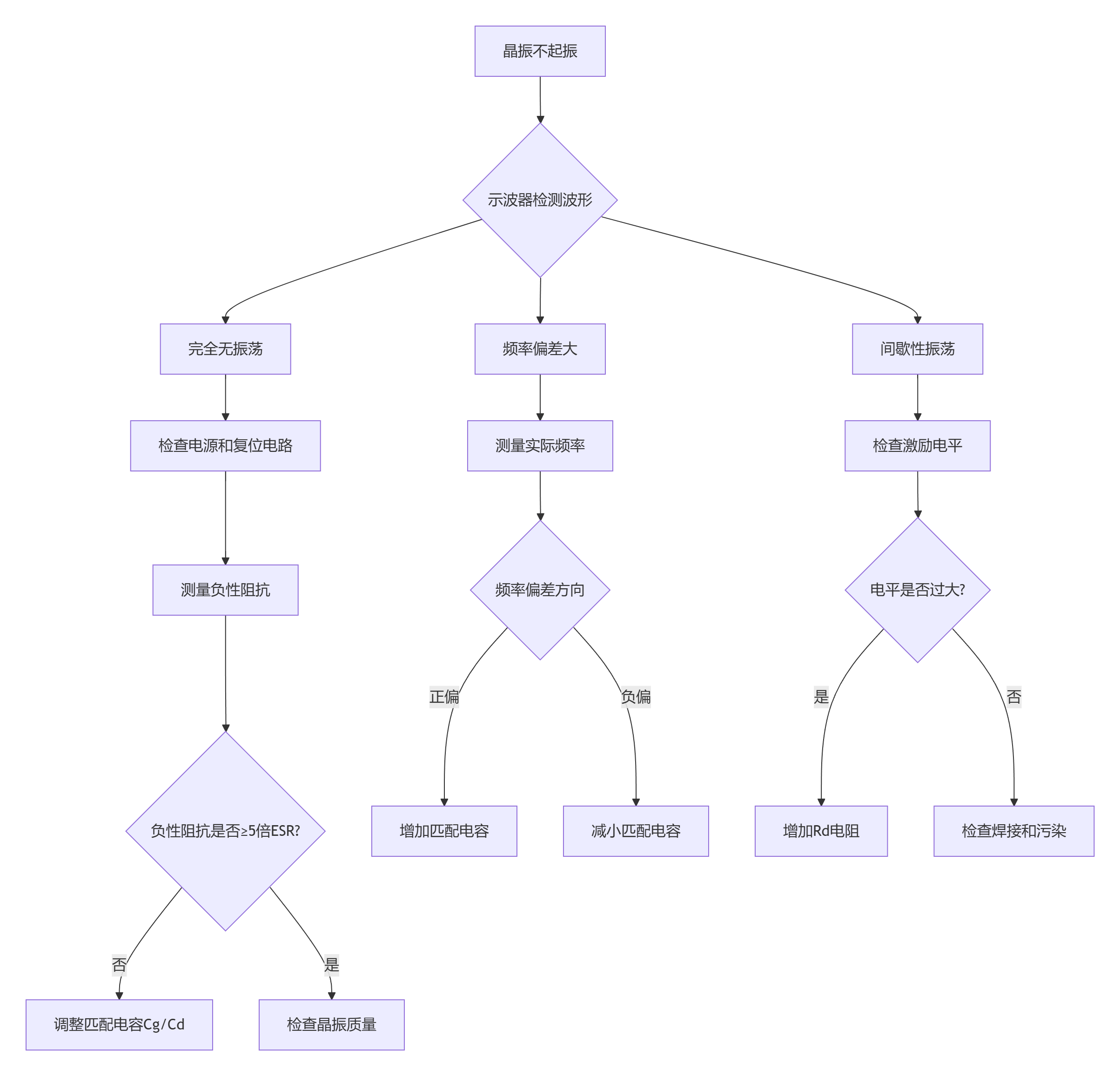

无源晶振(晶体)是数字电路的“心脏”,其设计质量直接决定系统的稳定性和可靠性。SOSET索斯特为您总结了这张检查流程图,帮你快速把握核心设计环节:

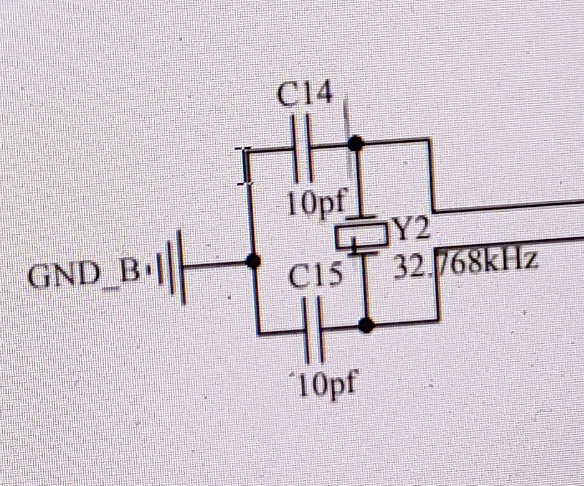

电路参考1

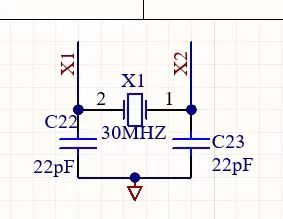

电路参考1 电路参考2

电路参考2下面我们来详细探讨每个环节的关键要点。

⚙️ 核心参数匹配

负载电容(CL)匹配是无源晶振设计的核心。晶振的标称频率是在特定负载电容下校准的。失配会导致频率偏移。计算时需考虑:

- 公式:最常用的简化公式为 CL = (C1 * C2) / (C1 + C2) + Cstray。其中 C1 和 C2 为外部匹配电容,Cstray 为PCB走线和芯片引脚的寄生电容,通常为 3pF至5pF。若 C1 = C2,则可简化为 CL = C1/2 + Cstray。

- 电容选型:优先选择 NP0/C0G 材质的电容,其温度稳定性好。容值常见于6pF至30pF之间。

- 频率微调:若实测频率偏差较大,可通过微调C1、C2容值来校正。通常负载电容每增加1pF,频率会降低约0.5ppm。

激励功率(DL) 需控制在晶振规格书限定的范围内。过驱动可能导致晶振机械损伤甚至早期失效。可通过串联一个限流电阻(Rext,通常为0-1kΩ)来调整。使用示波器观察波形,若正弦波峰峰被削平,说明可能过驱,需调整Rext。负性阻抗(-R) 是评估振荡电路稳定性的关键指标。为确保在各种条件下(如温度变化、老化)都能稳定起振,电路的负阻绝对值应至少为晶振等效串联电阻(ESR)的 5倍 以上。可通过负阻测试验证:在晶振回路中串联一个可变电阻Rtest,逐渐增大其阻值直至振荡停止,则负性阻抗 |-R| ≈ Rtest + ESR。

PCB布局布线要点

优秀的PCB布局对降低EMI和保证稳定性至关重要。

- 位置与走线:晶振务必靠近MCU的时钟引脚放置,走线长度建议小于10mm。XIN和XOUT走线应等长、并行走线,类似差分对,线宽8-12mil,间距≥3倍线宽。严禁在时钟信号路径上使用过孔。

- 隔离与包地:晶振下方及周围禁止布设其他信号线,特别是高频信号线。晶振周围用接地铜箔包围(屏蔽环),并每隔100-150mil放置接地过孔,形成法拉第笼屏蔽效应。

- 电源去耦:为MCU的振荡器电路电源引脚提供洁净的电源。通常需要在电源引脚附近放置一个0.1μF的去耦电容,有时还会并联一个更小容值的电容(如0.01μF)以滤除高频噪声。

振荡电路稳定性保障

- 反馈电阻(Rf):多数MCU内部已集成(通常1-10MΩ)。它使反相器工作在线性区,提供增益,对启动有帮助。若发现低温下起振困难,可尝试在外部并联1MΩ电阻以增强负性阻抗,改善启动特性。

- 启动特性:负载电容CL越小,负性阻抗越大,启动通常越快,但频率稳定性可能稍差;CL越大,启动可能稍慢,但振荡更稳定,远端相位噪声可能更好。需根据应用权衡。

- 温度影响:明确应用的工作温度范围,选择相应等级的晶振(如工业级-40℃至+85℃)。对于温度变化大的环境,需关注晶振的温度频差参数,或考虑选用有源晶振(如TCXO)。

测试验证与故障排查

设计完成后,必须进行实测验证。下表汇总了常见问题及对策:

常见问题 | 可能原因 | 解决思路 |

|---|---|---|

不起振 | 负载电容严重不匹配、负性阻抗裕量不足、PCB布局不良、MCU振荡器配置错误 | 检查电路配置和参数计算,优化PCB布局,验证软件配置 |

频率偏差大 | 负载电容不匹配、晶振本身精度不足、激励功率不当 | 微调匹配电容容值、检查晶振精度规格、用示波器观察波形调整Rext |

低温启动失败 | 负性阻抗裕量不足 | 尝试并联1MΩ反馈电阻、适当减小负载电容CL以增大负性阻抗 |

常温工作正常,运行一段时间后偶发死机 | 振荡裕量不足,在温度、电压波动或器件老化时临界失振 | 进行负阻测试,确保负性阻抗绝对值至少为晶振ESR的5倍以上 |

EMC辐射超标 | 晶振回路成为辐射天线、电源去耦不足 | 优化PCB布局(包地、屏蔽)、在电源线或信号线上增加磁珠滤波、确保屏蔽罩良好接地 |

测试时,建议使用高阻抗探头(如10MΩ阻抗,≤5pF电容)的示波器,带宽至少为晶振频率的5倍,以减少测量对电路的影响。

关键总结

无源晶振设计是一个系统工程,关键在于精确的参数匹配(尤其是负载电容)、严谨的PCB布局布线(最短路径、完整包地)、以及充分的振荡裕量验证(负阻测试)。设计时务必仔细查阅MCU和晶振的数据手册,理论计算与实测迭代结合,才能打造出稳定可靠的“心脏”。希望这些要点能对你的设计有所帮助!如果你在具体应用中遇到特殊挑战,欢迎进一步讨论。

-

无源晶振的参数特性 无源晶振的等效电路图2024-02-26 3298

-

无源晶振的等效电路与电路结构解析2024-09-11 5378

-

“无源晶振”真的是晶振吗?#电路设计 #PCB板 #电子工程师 #晶振 #无源晶振安泰小课堂 2025-05-23

-

晶振电路设计指南2022-07-05 9105

-

无源晶振的选型理念 无源晶振的EMC电路设计2023-08-19 7011

全部0条评论

快来发表一下你的评论吧 !