Microchip Switchtec™ PFX Gen 5 PCIe交换机技术解析与应用指南

描述

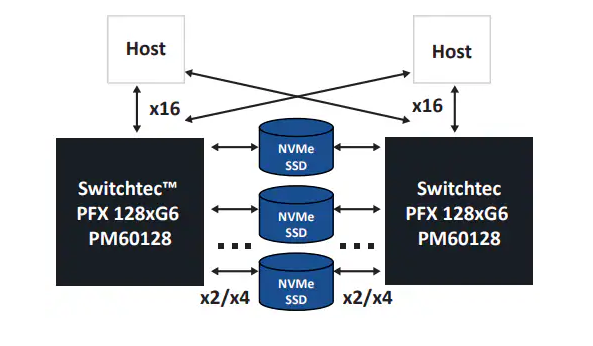

Microchip Technology Switchtec™ PFX Gen 5扇出PCIe ^®^ 交换机支持多达100个通道、52个端口、26个虚拟交换机分区和48个非透明桥接器 (NTB)。这些交换机为每个端口提供热插拔与意外插拔控制器、高级错误控制、全面诊断和调试功能以及各种I/O接口。典型应用包括数据中心设备、工业服务器、工作站、测试设备、视频制作和广播设备、蜂窝基础设施、接入网络和城域网络。

数据手册:*附件:Microchip Technology Switchtec™ PFX Gen 5扇出PCIe®交换机数据手册.pdf

特性

- 高性能无阻塞第5代交换机:

- 100通道、84通道、68通道、52通道、36通道和28通道版本

- 多达48个NTB,可分配给任何端口

- 借助逻辑非透明 (NT) 互连,可实现更大的拓扑

- 支持1+1和N+1故障转移机制

- 每栏使用直接窗口和多个子窗口进行NT地址转换

- DMA控制器:

- 高性能和超低延迟直通DMA引擎

- 多达64个DMA通道

- 错误控制:

- 所有端口上的高级错误报告 (AER)

- 所有下行端口上的下行端口控制 (DPC)

- 完成超时合成 (CTS),可防止由于未完成的非发布事务而导致上行主机出现错误状态

- 各端口的热插拔控制器和意外插拔控制器

- GPIO可配置为不同的电缆/连接器标准

- PCIe接口:

- 无源、托管和光缆

- SFF-8644、SFF-8643、SFF-8639、OCuLink及其他连接器

- 支持SHPC的插槽和边缘连接器

- 诊断和调试:

- 实时视觉捕获

- 外部环回功能

- 错误、统计数据、性能和TLP延迟计数器

- 外设I/O接口:

- 支持SMBus的两线制接口 (TWI)

- 兼容SFF-8485的SGPIO端口

- 并行GPIO引脚

- UART

- 100/GE MAC端口(RMLLL/GMLLL)

- JTAG和EJTAG接口

- 高速I/O:

- PCIe Gen 5 32GT/s

- 支持PCIe兼容链路培训和手动PHY配置

- 电源管理:

- 主动状态电源管理 (ASPM)

- 由软件控制的电源管理

- ChipLink诊断工具:

- 丰富的调试、诊断、配置和分析工具,带直观的GUI

- 可访问配置数据、管理功能和信号完整性分析工具(例如实时眼图捕获)

- 通过带内PCIe或边带信号(UART、TWI和EJTAG)连接器件

- 低功耗串行器/解串器 (SerDes)

- 安全的系统解决方案,带启动映像验证

示例应用

Microchip Switchtec™ PFX Gen 5 PCIe交换机技术解析与应用指南

一、产品概述与核心特性

Switchtec™ PFX Gen 5系列是Microchip推出的高性能PCIe®扇出交换机,专为高可靠性场景设计,支持 100条PCIe Gen 5通道(32 GT/s) 和26个虚拟分区,适用于数据中心、工业服务器及网络设备。其关键创新包括:

- 非阻塞架构:支持84/68/52/36/28通道多型号,满足不同规模拓扑需求。

- 高级容错机制:每端口独立热插拔控制器、下游端口错误隔离(DPC)及ECC内存保护。

- 灵活互联:48个非透明桥(NTB)可任意分配,支持N+1冗余和地址转换窗口。

二、硬件设计关键点

1. 接口与时序规范

- 物理层支持:兼容SFF-8644/OCuLink等接口标准,通过实时眼图捕获功能优化信号完整性。

- 电源管理:支持ASPM(活跃状态电源管理),可通过TWI(SMBus)接口动态调节功耗。

- 调试接口:集成JTAG/EJTAG和UART,结合ChipLink工具实现PHY层手动配置。

2. 错误处理与可靠性

- 错误合成:通过Completion Timeout Synthesis(CTS)防止上游主机因未完成事务锁死。

- 端到端保护:AER(高级错误报告)覆盖所有端口,配合DMA引擎的64通道低延迟传输。

三、开发资源与选型参考

- 评估套件:PM52100-KIT支持多接口原型验证,含信号分析工具包。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Microchip推出下一代Switchtec Gen 6 PCIe交换芯片2025-10-18 2019

-

Microchip PCI11400 PCIe交换机技术解析与应用指南2025-10-10 904

-

Microchip发布全新Switchtec™ PCIe 4.0交换机系列2025-01-22 1474

-

Microchip推出全新PCI100x系列Switchtec PCIe 4.0交换机2025-01-20 1764

-

PCIe Gen 2交换机带来不仅是更多的宽带2022-06-14 4170

-

Microchip第四代PCIe交换机加速自动驾驶发展2022-03-04 2232

-

microchip全新的PCIe 5.0交换芯片怎么样2022-01-04 4984

-

Microchip发布世界首款PCI Express® 5.0交换机,加速机器学习和超大规模计算基础设施发展2021-02-04 1794

-

Switchtec PAX交换机近日喜获Design World 2020飞跃奖2020-10-22 2372

-

Switchtec PAX网络互联Gen 4 PCIe交换机系列现已投产2020-06-24 3261

-

Switchtec™ PSX第三代PCIe可编程存储交换机已被纳入腾讯的某个参考设计2019-05-09 4807

-

Microchip的Switchtec PCIe可编程交换机为中国数据中心开发人员的开放式参考设计提供资源整合2019-03-29 783

-

美高森美推出Switchtec™Gen 4 PCIe交换机 构建下一代高性能、低延迟互连解决方案2018-08-07 6854

全部0条评论

快来发表一下你的评论吧 !