PCB设计时DDR线宽和阻抗是怎样确定下来的呢?全过程详细分析

电子说

1.4w人已加入

描述

PCB设计时DDR线宽和阻抗是怎样确定下来的呢?

让我们通一个具体的项目来学习一下。

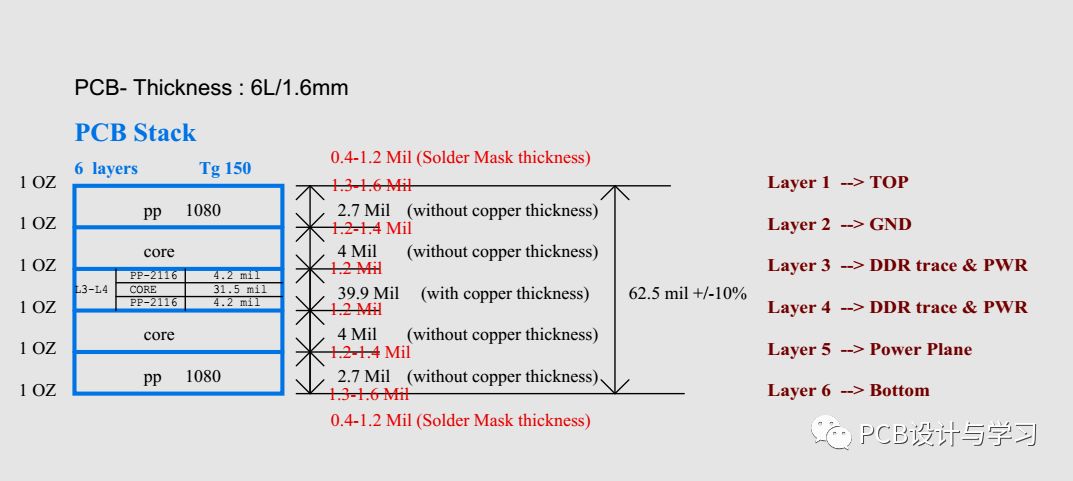

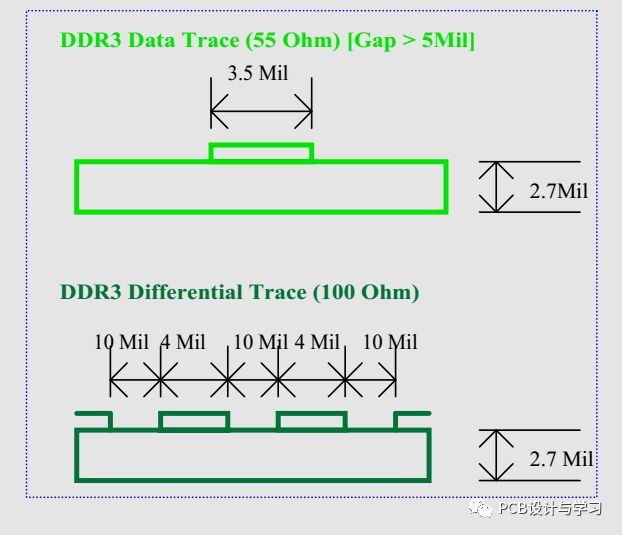

以上某个开发板原厂给出的PCB设计要求。PCB采用的是6层板的叠板设计,1.6MM的板厚。内层采用了两块4MIL含铜的芯板压合而成,芯板之间填充了一块不含铜的芯板和两块半固化片2116,主要是为了调节出1.6MM的板厚。1到2层和6到5层填充的是半固化片1080,压合后的厚度是2.7MIL。

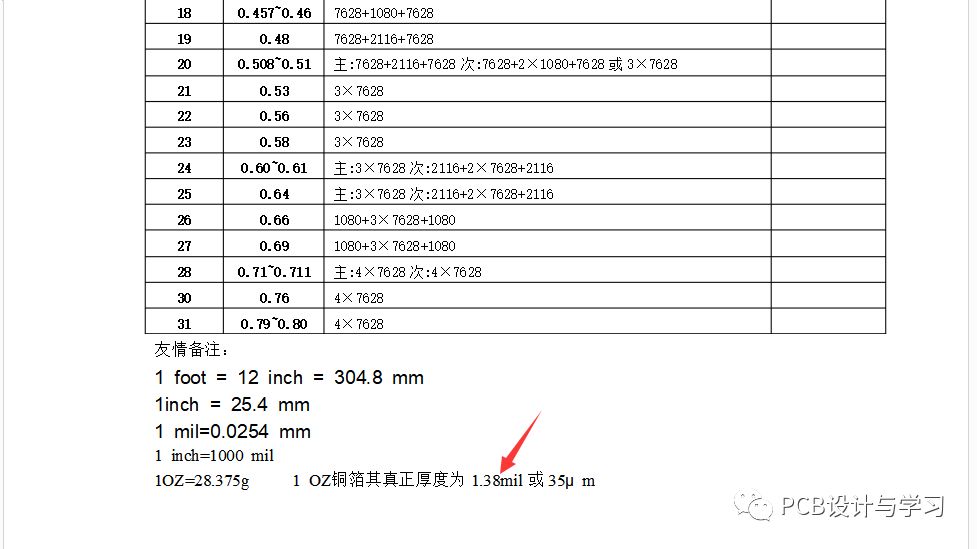

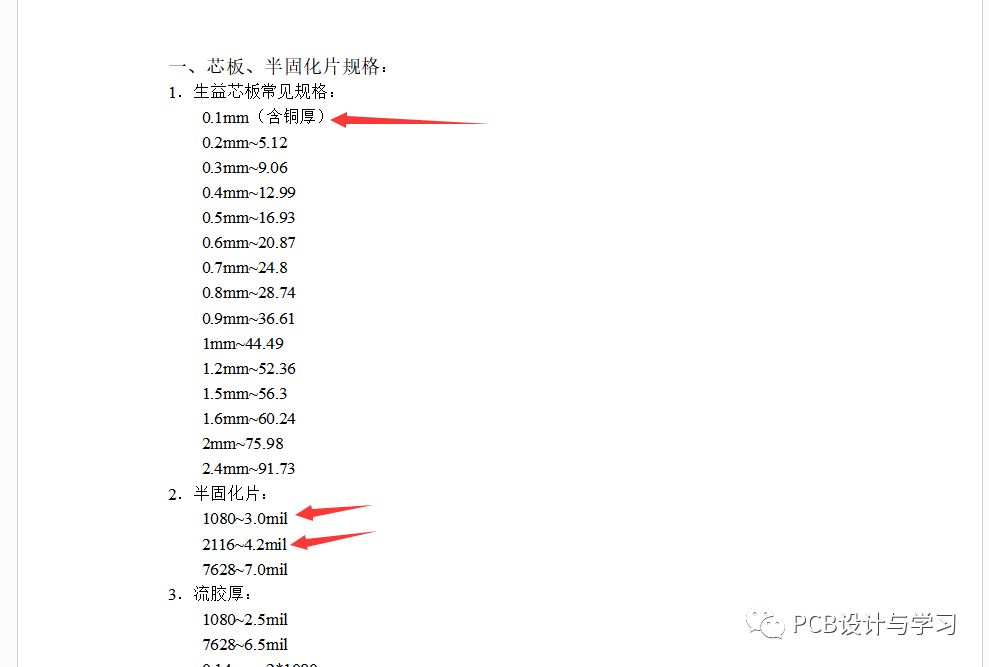

在网上找了一下芯板和半固化片的资料,和原厂给出来的参数,基本上吻合。

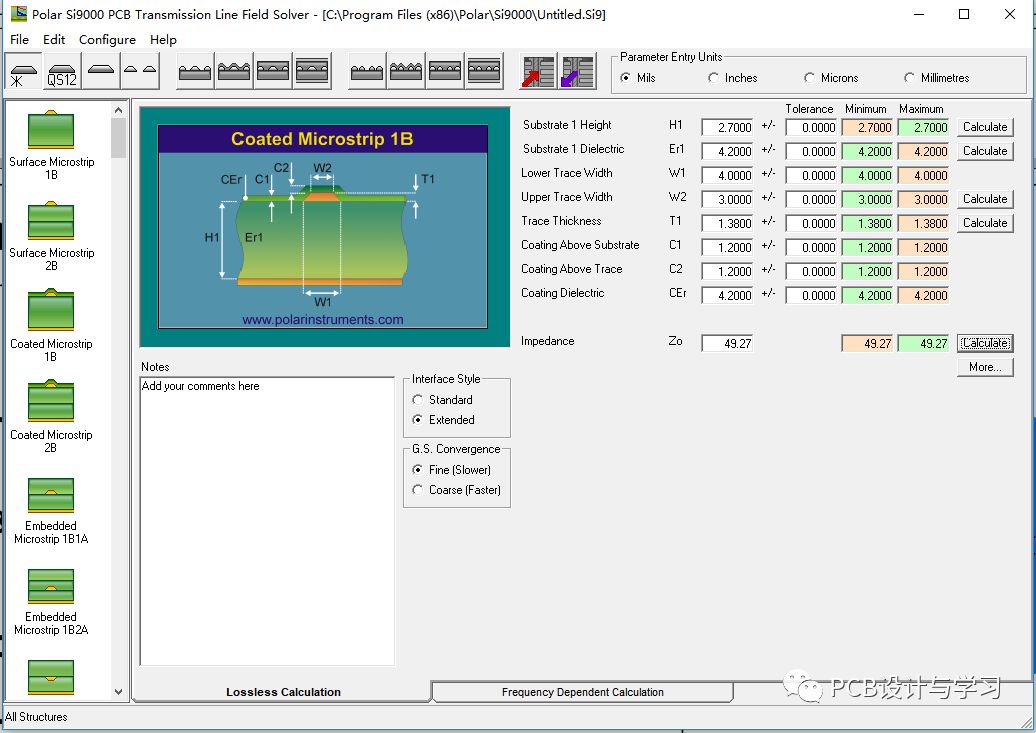

确认好原厂给出来的信息后,我们来用软件算一下,线宽和阻抗是不是都能对得上。

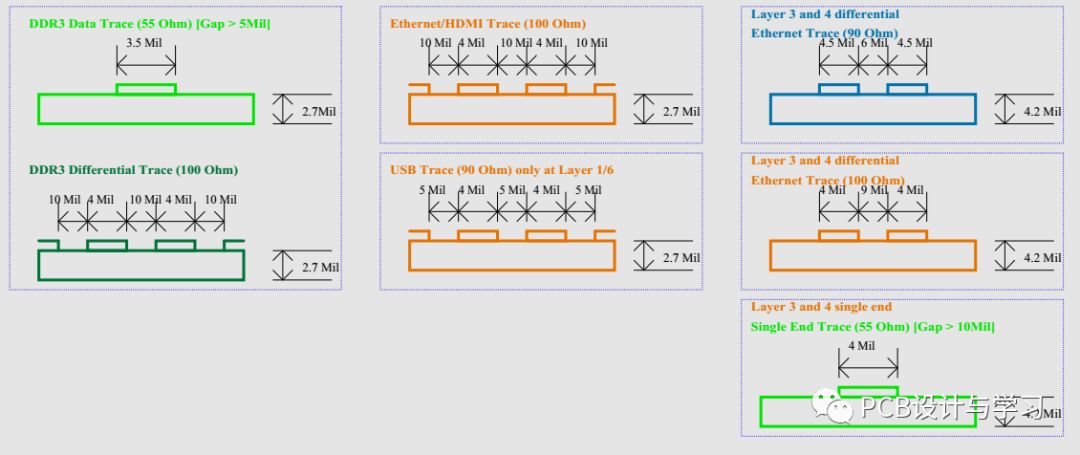

走在外层的DDR3信号传输线线宽3.5Mil,到参考平面高度是2.7Mil,构成的阻抗是55Ohm。用软件验证如下:

由软件算出来的是49.27Ohm,和原厂给出来的55Ohm有一些出入。

走在外层的DDR3差分信号传输线线宽4Mil,到参考平面高度是2.7Mil,构成的阻抗是100Ohm。用软件验证如下:

由软件算出来的是89.9Ohm,和原厂给出来的100Ohm有一些出入。

通过上面的方法,我们大概知道了DDR线宽和阻抗是怎样确定下来的。以后我们自己设计DDR的时候,就可以用这种方法来确定DDR的线宽,PCB板叠层情况,使我们设计出来的板性能更好,更稳定。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

PCB设计铜厚、线宽和电流关系表2022-10-17 2472

-

请问一下怎样对stm32的启动代码进行详细分析呢2021-11-26 1638

-

如何确定大电流导线线宽呢2021-10-09 2353

-

讲述PCB设计全过程操作2021-08-03 1414

-

stm32的最小系统PCB设计全过程操作步骤2021-07-20 1271

-

手工制作pcb全过程2021-06-19 2338

-

PCB设计时DDR线宽和阻抗是如何确定下来的呢?资料下载2021-04-11 1008

-

浅谈PCB设计的DDR线宽和阻抗2020-12-07 11381

-

Uboot启动的全过程详细资料分析2019-04-25 1223

-

物联网的产业生态是怎样的详细分析概述2018-12-08 5718

-

PCB设计教程之铜铂厚度线宽和电流的关系表资料概述2018-12-06 1248

-

cadence从原理图到PCB设计全过程(精华)2014-10-24 23053

-

PCB 制作全过程2012-08-05 76767

-

PCB设计铜铂厚度、线宽和电流关系表2008-07-17 8390

全部0条评论

快来发表一下你的评论吧 !