基于R2000的高性能多天线结构读写器方案设计

RF/无线

描述

近年来,随着信息技术的不断发展与进步,物联网技术得到了飞跃发展,并拥有广阔的应用前景。无线射频识别(RFID)作为物联网中的重要技术,其应用前景随着物联网技术的深入发展受到越来越多的关注。而随着低功耗和高性能集成射频收发芯片的不断推出,小型化、模块化、高性能的超高频RFID读写器也应运而生。

本论文主要是设计一款基于R2000的高性能多天线结构读写器,和一般UHFRFID系统产品开发流程一样,按照应用需求分析、确定指标参数、制定系统方案、硬件电路设计、_上位机软件设计、系统集成、整机性能测试、形成产品顺序进行,整个项目产品开发流程如图2-1所示。

(1)应用需求分析

在该阶段主要是通过市场调研了解市场需求。本文涉及的读写器产品是应广东省中山市一家公司的需求而设计,主要是面向仓储管理、物流供应链管理两个应用领域。这两个应用领域需要读写器能够对电子标签实现远距离无漏识别,同时要求无漏识别速度快。

(2)确定指标参数

在了解市场单位的应用需求一设计一 -款能对电子标签实现高速、无漏、远距离识别的读写器,为此需要先确定电路总体参数指标要求,并将指标细化分到各个部分,从而确定器件的选择范围, 便于总体方案设计。

(3)制定系统方案

确定了电路指标参数后,需要根据各电路模块要求选择合适的芯片器件,并将器件关键引脚标注出来,将各部分电路框图连接,构成整个系统方案。在这个过程中需要考虑系统方案的可实施性,同时尽量优化设计研发成本。

(4)设计硬件电路

在制定系统方案时只是粗略描述了电路各部分的框图,在硬件电路设计过程中需详细设计各电路原理图, 以及电路模块的接口形式,为组成电路系统做好前期准备。

(5)系统集成

在这个阶段主要是将电路整体联系起来,设计整个电路的原理图和PCB版图,逐步焊接电路并调试电路保证电路每部分都能正常工作,最后将各电路模块组合在一起构成一个电路系统。

(6)整机性能测试

待电路调试通过后,将电路模块安放在读写器磨具内,烧写和配置相应的驱动程序和控制程序,模拟实际应用环境,进行整机性能测试。

(7)形成产品

整机性能测试完成后,需要进行稳定性和高低温测试,待所有测试通过后,贴_上合格证,将产品放进包装盒内,准备出货。

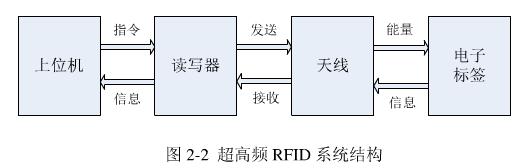

2.2、超高频RFID系统组成

超高频RFID系统有四个重要组成部分,分别为上位机系统、读写器、天线和电子标签,此系统的工作过程是0-1:。上位机发送指令给读写器, 读写器在上位机指令的控制下,开启射频模块发送高频信号,通过天线在RFID电子标签周围形成磁场,当磁场强度足够大时,标签内部的芯片电路被激活,然后将自身携带的信息加载到电磁波中返回给读写器,读写器接收并转换数据信息,再通过上位机的加工处理,完成电子标签信息的获取过程。而当标签离开射频磁场时,标签由于没有足够的能量激活芯片电路而处于休眠状态。整个系统组成如图2-2所示:

2.2.1上位机

本文中的上位机主要是指集成在整个设备内部,与射频模块通信的PC主控机。超高频RFID读写器需要上位机发出控制指令启动读写器发送射频信号,读写器接收到标签返回的信号也需要上位机处理并进行存储,实现整个超高频RFID系统的正常工作。

2.2.2读写器

超高频读写器( Reader)即射频模块, 是整个RFID系统的关键组成部分。首先射频模块决定了整个系统的工作频段;其次,读写器的发送功率和接收灵敏度直接影响整个系统的最大识别距离。射频收发电路、数字基带控制电路和电源管理模块是读写器的主要组成部分。射频发射链路主要是产生高频载波信号,完成基带信号的调制与功率放大,以便为电子标签提供足够的能量。射频接收电路则实现对电子标签返回信号的解调与低噪声放大。数字基带电路用来解析上位机控制指令,以便控制射频收发电路的工作。电源管理部分主要是给各电路模块供电,使各电路模块能够正常工作。

2.2.3天线

天线(Antenna)是一种无源装置,用来实现电磁波与电流信号的相互转换。天线在超高频RFID系统中主要用来发送与接收高频载波信号。超高频RFID系统的天线配置可以采用收发分离与收发合一一两种形式。收发分离主要是采用两个天线将射频信号分离,-一个用来发送读写器输出的射频信号,另一个用来接收标签返回的射频信号,采用这种方式射频收发信号间的相互干扰小,成本相对较高。收发合一则是用环形器或定向耦合器实现收发信号的分离,该方案中射频收发信号间的相互干扰较为严重,需要有效地抑制射频载波泄漏对接收信号的干扰。考虑到实际设计成本与简化电路结构,本设计中的读写器采用定向耦合器搭建收发分离电路结构并使用增益为8dBi的圆极化天线。

2.2.4电子标签

电子标签(Tag) 是数据信息的载体,主要由偶极子天线、谐振电容以及微型IC芯片封装而成!41。RFID读写器发送的电磁波在空间形成磁场,当标签进入磁场范围内且磁场能量足够大时,标签芯片中的电源管理电压便依靠此电磁波能量感应出电压为标签芯片供电,并将内部信息加载到电磁波中并返回读写器,完成读写器与电子标签之间的无线通信。

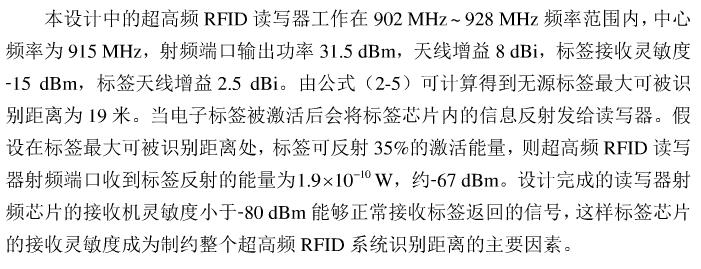

标签的灵敏度对射频识别系统读写距离有着举足轻重的影响。本设计中的超高频RFID读写器采用E4IB仓存物流标签和Monza4QT标签,两款标签接收灵敏度均在- 15dBm (30uW)左右,能够到达远距离识别的要求。

2.3、系统功能分析

考虑到常规单天线或四天线读写器盘存范围受限,本论文中提出设计多天线结构的读写器方案,让天线能够覆盖仓库的每个角落,确保仓库内所有货物上的RFID电子标签都能被读写器无漏识别。

鉴于分立电路元件搭建的射频收发系统过于复杂,电路体积庞大,在设计电路方案时,考虑采用高集成度芯片作为主射频收发芯片来实现电路方案,在保证电路性能的前提条件下,简化电路结构,并设计成了射频收发电路模块,可以独立与其他上位机使用,进一一步简化了整套设备的电路模块组成结构, 并提高整个电路系统稳定性。

当前RFID技术中的信息安全问题时常发生,导致商家或者个人的重要信息泄露,这阻碍了RFID技术的进一一步发展与普及。为了消除RFID技术中的信息安全隐患,在设计过程中结合特殊技术, 通过上位机软件实现对标签的加密处理,需要输入密码口令才能访问商家或者个人私有信息内容。结合上述功能需求与当前市面_上读写器的特点,本文设计的读写器要求的性能指标如下:

(1)工作频段: 840 MHz ~ 960 MHz;

(2)最大输出功率:≥30 dBm;

(3)接收机灵敏度:≤-80 dBm;

(4)识别标签距离:≥15米;

(5)无漏识别标签数目: 2200张(10s内);

(7)射频模块功耗:≤10W;

(8)实时显示设备的工作状态;

(9)标签信息安全。

为了实现上述功能,在设计超高频台式读写器系统过程中,从高读写性能、多天线结构、工作指示功能、读写信息安全四个方面考虑软硬件电路的设计。

2.3.1高读写性能

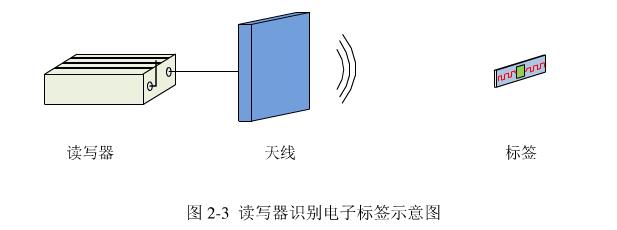

在设计超高频RFID读写器硬件电路结构时,需采用阻抗匹配网络和低插入损耗电路结构,使得射频信号功率从源端向负载端的最大化传输。设计完成的超高频RFID读写器射频端口最大输出功率需达到31 dBm,能够在10s内快速无漏

识别240张超高频RFID电子标签,整个读写器接收机灵敏度小于-80 dBm。在测试过程中采用8dBi增益的天线与接收灵敏度为-15dBm的E4IB电子物流标签,电子标签最大可被识别的距离超过15米。超高频RFID读写器识别电子标签过程如图2-3所示。

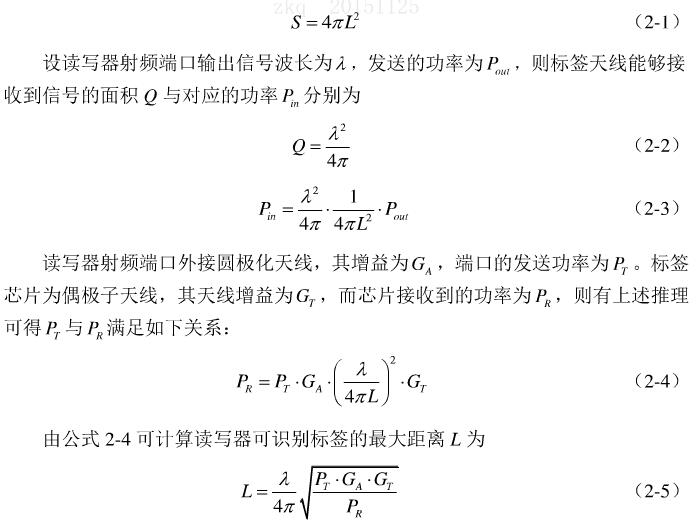

RFID读写器发射高频载波信号,此信号经过天线转化为电磁波,而电磁波在空间介质中-一般有传输损耗。整个读写器采用圆极化天线, 假设天线在方向角包围的曲面区域各方向均匀辐射能量,且能量密度在该曲面各处相同,对于此类各向同性天线,其接收功率与天线有效面积成正比。在距离天线L米远处,天线的辐射面积为s,则

2.3.2多天线结构

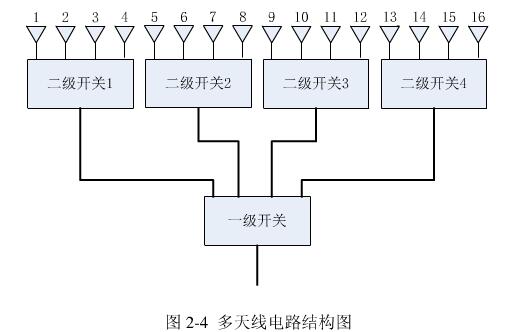

当前市面上常见的超高频RFID读写器多为单天线或者四天线结构,这两款读写器只适合应用于盘存小范围内的电子标签。对于较大范围的电子标签采用多台读写器来完成盘点任务,不仅会带来高昂的成本,而且还需要解决多台读写器同时工作时信号之间相互干扰问题。基于上述考虑,本文设计了- -款多天线结构超高频RFID读写器,不仅能够完成大范围内电子标签的盘点,而且各天线端口采用时分复用,因此也不存在读写器各天线端口信号间的相互干扰问题。读写器多天线电路结构如图2-4所示。

在设计过程中通过两级开关,共配置十六个天线端口,采用时分复用的方式,每个天线端口都可以独立工作,进行电子标签的盘存和初始化工作。多天线结构能够覆盖更大的空间区域,保证在仓存管理过程中能够识别到所有方位上标签。为实现读写器对标签的无漏识别,天线应朝不同方位均匀安放,保证天线能够覆盖到所有标签。测试过程中两种多天线读写器天线位置安放如图2-5所示。

在实际应用过程中可根据实际需要,选择超高频RFID读写器天线的数目和天线的安放位置,以保证使选择的天线的辐射范围能够覆盖所有RFID电子标签,从而保证在仓存管理过程中所有标签都能至少能被一个天线发射的信号识别到,实现仓存管理中的高速无漏识别。

2.3.3工作指示功能

常规读写器无法实时掌握每个天线端口的工作状态,当某个天线端口出现异常状况时难以及时发现, 长期这样工作会降低工作效率并影响读写器的性能,为避免这种情况的出现,在设计读写器硬件电路结构时,增加工作指示功能电路,这样可以通过指示灯的状态实时了解整个读写器的工作情况。

工作指示功能包括读写器上电指示、开机指示、射频模块供电指示和每个天线端口工作状态指示。上电指示是用来判断整个读写器是否通电; 开机指示灯则是用来指示读写器上位机系统是否启动;射频模块供电指示用来指示上位机软件是否成功发送驱动信号,让电源管理模块给射频模块供电;天线端口指示电路主要是让十六个指示灯与十六个天线端一一对应,实现指示灯实时显示每个天线端口的工作状态。

2.3.4、读写信息安全

目前超高频RFID技术处于发展阶段,相关应用领域对信息安全要求不高,导致很多厂商和用户对RFID系统中的信息安全问题不够重视。随着超高频RFID技术的不断发展与成熟,信息安全问题将变得尤为重要。

本文在考虑读写器与电子标签安全通信方面,采用IMPINJ公司的Monza4QT电子标签, 该电子标签包括私有配置与公共配置两种模式。在保密隐私性较高的场合,可以通过上位机程序将标签设置为私有配置模式,在私有配置模式下读写标签私有信息需要访问密码。当超高频RFID读写器需要识别电子标签私有信息时,需要先通过上位机程序输入访问密码,待身份验证通过后读写器才能识别标签用户区信息;如果识别到标签的读写器需要改变标签用户区的内容时,需要在上位机程序界面中输入写标签密码验证。采用这种私有配置加密方法,可以防止标签信息被其它读写器非法获取、修改甚至恶意毁坏。

2.4、硬件电路设计方案

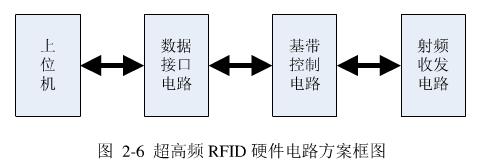

对于一般的超高频RFID读写器硬件电路而言,其电路可以分解为数据接口电路、数字基带控制电路以及射频收发电路,本文在读写器内部增加上位机主控平台,这样设计完成的读写器可以脱离其他控制平台而独立工作。基本电路方案组成如图2-6所示。

其中数据接口电路与上位机连接,主要用来向数字基带模块烧写控制程序与相关配置,以便实现读写器与上位机的通信;数字基带电路接收、解析上位机传来控制指令并发出信息给射频收发电路(201;射频收发电路收到基带控制电路发送过来的信号后产生高频载波,对基带信号进行各种变换处理,并经过放大处理向外辐射以及接收处理电子标签返回来的信号,实现读写器对电子标签的获取。

2.4.1接口电路

接口电路是超高频RFID读写器重要组成部分,一般由基带控制电路程序配置接口电路与上位机通信接口电路两大组成部分。常见的基带电路程序配置接口电路有UART、J-TAG 等,这些接口电路实现对读写器基带电路程序的配置与烧写。读写器与上位机通信接口一般有RS232、RS485、USB与RJ45等,其中RS232属于双工单端通信方式,通信距离能够达到10米左右,最大通信速率为20 kbps;

RS485是半双工平衡通信,通信距离能达到1千米,数据传输速率能达到10Mbps;而USB是一种双向同步传输的串行数据接口,最大传输速率达12 Mbps,最大特点是支持热拔插。在设计高性能多天线结构读写器过程中,为了使用方便并支持热拔插,射频模块接口采用USB与上位机通信,而程序的烧写与配置采用UART及J-TAG方式。

2.4.2数字基带电路

数字基带电路是超高频RFID读写器模块的重要组成部分。本文设计的读写器数字基带电路ARM采用Atmel公司的一款集成芯片。该ARM控制芯片是-款32位精简指令处理器,拥有256kb闪存(Flash)和64kb静态随机存储器(SRAM),其内部结构按功能可分为数据10口模块、参考时钟模块、电源模块和J-TAG与UART接口模块四个部分。

ARM芯片与射频收发电路的数据通信主要是通过数据IO口模块实现的,这些数据信息包括发送与接收过程的时钟信号(TCK)、 数据帧信号(FRM)、 数据信息(DIO), 功率检测反馈信号以及射频开关控制信号。

参考时钟模块用来为整个ARM芯片提供参考时钟信号。内部含有一个锁相环电路结构,输出时钟频率为80 MHz~200 MHz,参考时钟晶振频率为18.432 MHz;外部有一个低功耗的RC振荡器,可以提供22~42 KHz的振荡频率。

电源模块采用低通滤波和去耦合电容为芯片中的数据I0口模块和存储电路提供稳定的工作电压。

J-TAG与UART接口模块则用来向基带主控芯片烧写代码程序、实现在线编程和芯片测试。

2.4.3射频收发电路

整个超高频读写器电路中最关键部分是射频收发电路的设计,目前主要采用如下两种方式设计:

(1)采用分立元器件搭建射频收发电路,

(2)采用集成的射频收发芯片加外围电路实现收发功能。采用分立元件搭建方案设计的超高频RFID读写器拥有自主知识产权, 分立器件的采购相对容易, 但因电路结构复杂增加设计难度, 且电路性能较差。而采用集成射频收发芯片设计的读写器开发周期短、电路结构简单,整机稳定性好,不足之处是集成芯片价格偏高。从电路结构与系统稳定性出发,本文中选择采用集成芯片设计多天线读写器。

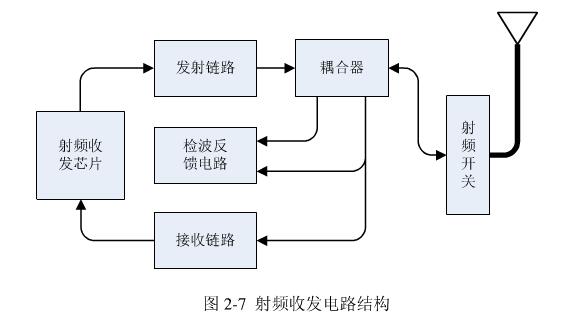

对于传统的超高频RFID而言,其读写器的收发电路由以下三部分组成,分别是发射链路、接收电路以及收发分离网络。本方案在硬件电路设计过程中增加了两极开关电路和功率检测保护电路,通过两极开关的级联, 设计出了时分复用的十六天线结构。功率检测电路能够实时检测射频链路发送和接收功率是否在规定的范围内,以保证整个射频收发电路不会因为功率异常而被烧毁。设计完成的超高频RFID读写器的射频收发电路结构如图2-7所示。

本项目是需要设计一款超高频RFID读写器, 目前市面上主流的UHF频段的集成收发芯片主要有Phychips的PR9000、奥威公司的AS3992和Impinj公司的R2000三款。这三款芯片的主要参数对比如表2-1所示。

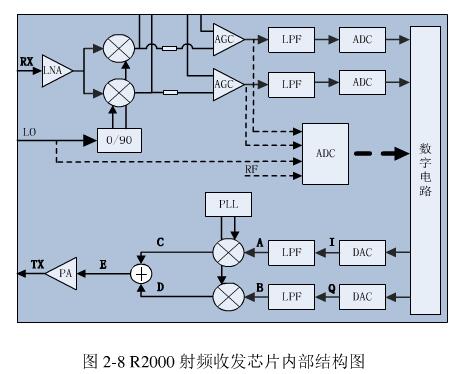

由表2-1可知,三款集成射频收发芯片适用频率、调制方式以及支持协议基本相同,主要在发射功率与接收灵敏度方面有较大差异。其中R2000芯片的接收灵敏度最小,最易于实现本项目产品识别距离远的设计指标,R2000芯片内部基本结构如图2-8所示。

(2)射频接收电路

接收电路主要实现对标签返回信号的接收变换处理。当前常见的接收电路结构主要有如下两种形式:一种是超外差式,另一种是直接下变频。

超外差式接收机经过两次下变频将高频载波信号解调为基带信号,主要有如下特点:

1)经过一次变频后的信号属于中频信号,其频率比载波信号频率低很多,信号频率越低对信道选择滤波器的要求也越低。

2)接收信号通常很微弱,为了能够正常接收到标签返回的信号,接收机需要很大的功率增益;采用超外差式结构,通过两次下变频将信号变换到中频和低频, 在低频段_上更容易对信号进行高增益放大。

3)在频率较为固定的中频。上解调和模数转换也相对容易。

直接下变频接收机中高频载波信号直接被变换为基带信号,因此也称为为零中频(ZIF) 接收机。它的优势体现在:接收机前端结构简单,只包含低噪声放大器(LNA)和混频器,且对低噪声放大器增益要求不高,容易实现动态范围大这一要求; 由于变换后输出的是基带信号,仅用电路结构简单的低通滤波器就能实现对有用信号的选择。

R2000内部接收链路只有一个混频器电路,适合采用零中频接收机结构。接收机灵敏度为-84 dBm。 从标签返回来的信号与发射机耦合过来的自校准信号叠加后,进入功率增益为7 dB的射频低噪声放大器,分为1,Q两路,与耦合过来的发射信号进行下变频,将射频信号解调为基带信号,混频器后面的可调交流电容将基带信号中的直流成分滤除,然后通过最大增益为24 dB的自动增益控制电路放大,经过带宽可调的低通滤波电路,进入模数转换电路,完成信号的接收过程。

2.5、本章小结

本章节介绍了超高频RFID读写器电路的总体方案,主要是采用集成的收发芯片R2000来搭建射频前端电路和AT9ISAM7S-256集成芯片作为基带控制电路核心部分。整个读写器电路结构得以简化、设计调试难度降低、工作性能稳定。其中高读写性能、多天线结构、实时指示工作状态和标签信息安全是本文设计的基于R2000读写器的特色之处。

-

集成式RFID读写器与非集成RFID读写器2026-03-16 213

-

ST25RU3993 UHF RAIN RFID高性能读写器芯片2023-09-13 912

-

迅远RFID高性能超高频读写模块M2216介绍2023-04-17 1111

-

迅远高性能超高频读写模块M2240满足不同覆盖需求2022-11-01 1610

-

超高频R2000嵌入式读写器的功能特点介绍2021-04-29 1364

-

超高频RFID四通道读写器参数2020-12-24 3572

-

如何通过提高天线延长RFID读写器的操作距离2020-08-27 1761

-

一款基于R2000的高性能多天线结构读写器2018-09-12 658

-

基于R2000芯片的读写器架构分析 浅谈R2000芯片之架构2018-08-13 19660

-

r2000芯片引脚图详解_r2000芯片使用说明2018-07-17 14868

-

R2000的电路设计2013-09-24 4161

-

手持RFID读写器的分形天线性能最佳2012-11-13 1488

-

UHF射频读写器的设计2011-11-03 942

全部0条评论

快来发表一下你的评论吧 !