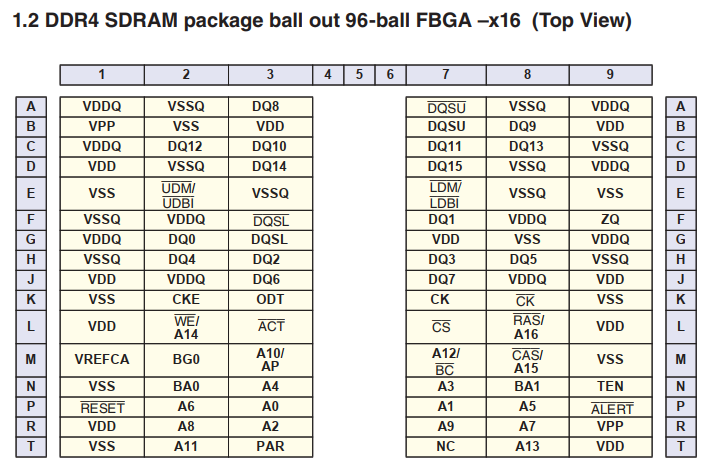

DDR器件管脚说明

描述

以下文章来源于硬件BIG BANG,作者Henry Xiao

引言:DDR是硬件设计的重要一环,作为一名硬件工程师除了对DDR基础和原理要有了解外,最重要的也就是对DDR控制器的掌握。本文章从DDR外部管脚的角度进行描述,学习DDR的关键设计要注意和了解的部分。

一、DM_n、UDM_n和LDM_n

——均为数据掩码信号(Data Mask)数据掩码作用,掩码信号的核心功能:

写入时屏蔽数据:当掩码信号为有效电平(通常为低电平)时,对应数据总线的字节(或半字节)不会被写入内存。

同步时序:掩码信号与数据选通信号(DQS)同步采样,确保在数据窗口中心对齐时生效

| 信号名称 | 适用位宽 | 作用范围 | DDR支持 | 关键特性 |

| DM_n | x8 | 全部8位数据(DQ[7:0]) | DDR1~DDR5 | 基础掩码;DDR4可复用为DBI/TDQS |

| LDM_n | x16 | 低8位数据(DQ[7:0]) | DDR3/DDR4 | 与LDQS同步采样 |

| UDM_n | x16 | 高8位数据(DQ[15:8]) | DDR3/DDR4 | 与UDQS同步采样 |

二、DQS_c、DQS_t

DQS_T(Data Strobe True)和 DQS_C(Data Strobe Complement)是一对差分数据选通信号,共同构成数据传输的同步基准。它们的核心区别在于相位关系、功能角色和时序对齐方式

1. 读取操作(Read)

信号来源:由DRAM芯片生成并发送给控制器(如CPU)。

时序对齐:

DQS_T/DQS_C 的边沿(上升/下降沿)与数据(DQ)的边沿对齐,标识每个数据周期的起始点

控制器在 DQS_T 上升沿和 DQS_C 下降沿的交叉点采样数据

目的:确保接收方在数据窗口的稳定中心点采样,避免因 tAC(数据输出时间偏差)导致错误

2. 写入操作(Write)

信号来源:由控制器(如CPU)生成并发送给DRAM。

时序对齐:

DQS_T/DQS_C 的电平中点(非边沿)与数据(DQ)的稳定中心对齐。

DRAM在 DQS_T 的上升沿和 DQS_C 的下降沿触发数据采样

目的:利用数据保持周期(Data Hold Window)最大化时序容限,适应传输延迟差异

三、ALERT_n

ALERT_n是DDR4及DDR5内存中的关键错误报告引脚,其核心功能是实时反馈内存内部异常状态,通过低电平有效信号(LOW)向控制器传递错误信息。

命令/地址奇偶校验错误(CA Parity Error)

当命令或地址总线传输的数据奇偶校验失败时触发,表明传输过程存在信号完整性问题(如干扰或时序偏移)

写入数据CRC校验错误(Write CRC Error)

在支持CRC校验的DDR4/DDR5中,写入数据若CRC校验失败,则通过ALERT_n通知控制器

温度超限或刷新错误

部分设计中可扩展用于报告温度传感器超限(如过热)或刷新操作失败等异常

四、TDQS_t 和 TDQS_c

TDQS_t 和 TDQS_c 是 DDR 内存中的终端数据选通信号(Terminal Data Strobe),主要用于优化信号完整性,特别是在 x8 位宽配置的 DRAM 芯片中。为何 x16 不需要 TDQS?独立的 DQS 分组x16 设备将 16 位数据拆分为高低两个字节组(每组 8 位),分别由 DQSU_t/c(高字节)和 DQSL_t/c(低字节)独立控制每组 DQS 自带终端电阻,无需TDQS 提供额外支持。负载均衡设计,x16 的 DQS 信号已通过分组隔离(如高低字节分离)实现负载均衡,反射问题在组内解决而 x8 设备单组 DQS需覆盖全部 8 位数据,混合系统易因负载不均引发反射,故需 TDQS 辅助。

五、TEN

TEN引脚(Test Enable) 是专用于连接性测试模式(Connectivity Test Mode) 的功能性引脚,其核心作用是在生产测试或系统调试阶段验证内存芯片与控制器之间的物理连接完整性和基本功能。

| 维度 | 说明 |

| 核心功能 | 高电平启用并行连接性测试,验证信号路径与电气连续性 |

| 正常操作 | 必须保持低电平,否则导致功能异常 |

| 电气特性 | CMOS轨到轨信号,高低电平阈值与 VDD 强相关 |

| 适用设备 | x16强制支持;x4/x8需≥8Gb容量;Micron 3DS不支持 |

| 设计建议 | 生产测试后硬接GND;系统设计时确保无噪声干扰;退出CT模式后必须复位 |

注:在DDR5中,TEN 功能被保留并优化,但部分厂商(如三星)可能扩展其用途至温度监控(需结合模式寄存器)。

六、ACT_n, RAS_n/A16,CAS_n/A15,WE_n/A14

在DDR(Double Data Rate)内存系统中,RAS_n/A16、CAS_n/A15、WE_n/A14 是复用引脚,其功能由 ACT_n(激活命令输入)信号的电平状态动态切换。它们既是命令控制信号(如行选通、列选通),又是地址线的高位部分(A16、A15、A14),通过复用设计减少引脚数量,同时支持更灵活的寻址机制。

场景:执行激活命令(ACTIVATE)时,ACT_n=0,此时引脚传输完整的行地址(如选择Bank内特定行)

场景:执行读写命令时,ACT_n=1,三引脚组合生成命令编码(如读命令:RAS_n=1, CAS_n=0, WE_n=1)

RAS_n:行地址选通信号,低电平时触发行激活或预充电

CAS_n:列地址选通信号,低电平时触发列读写操作

WE_n:写使能信号,低电平表示写操作,高电平表示读操作

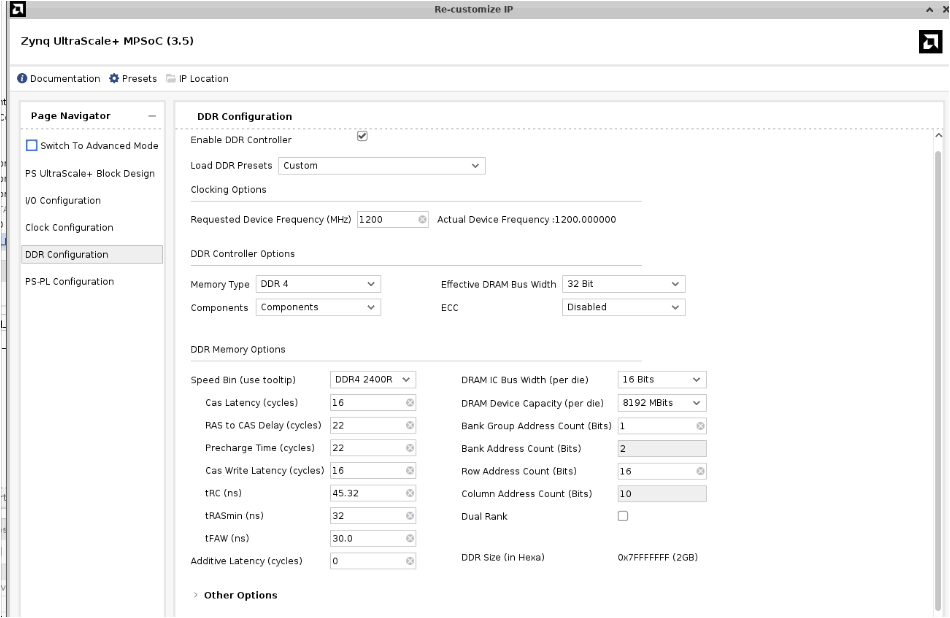

关键时序参数

tRCD(RAS to CAS Delay):行激活到列操作的最小延迟(典型值10-20ns),确保行数据稳定

tRAS(行活跃时间):行激活到预充电的最短周期,避免数据丢失

tRP(Row Precharge Time):预充电到下一行激活的间隔,影响Bank切换效率

图: 实际使用中会配置的时序参数

七、CKE、CK_t/CK_c

CKE:时钟使能信号

1. 工作逻辑

高电平(激活):启用内部时钟电路、输入缓冲器和输出驱动器,允许正常读写操作

低电平(休眠):触发低功耗模式:

预充电掉电(Precharge Power-Down):所有Bank空闲时进入,关闭非必要电路

激活掉电(Active Power-Down):任一Bank有激活行时进入,保留数据但暂停操作

自刷新(Self-Refresh):关闭除CKE外所有输入缓冲,内部定时刷新数据以维持存储内容

2. 关键约束

读写期间:必须保持高电平,否则可能导致命令失效或数据错误

模式切换:

退出自刷新需同步操作:CKE拉高后,需等待 tXSR(自刷新退出时间)再发送有效命令

掉电模式退出需满足 tCKE(最小CKE脉冲宽度)

3. 多Rank系统扩展

当存在多个Rank(如双通道内存)时,每个Rank有独立的CKE信号(如CKE0、CKE1),支持分时休眠以优化系统功耗

CK_t/c:时钟信号

CK_t(True Clock)和CK_c(Complementary Clock)构成差分时钟对,提供全系统操作的时序基准。所有地址、控制信号均在CK_t的上升沿与CK_c的下降沿的交叉点被采样.

八、CKE,CS_n,ODT

CS_n(Chip Select,片选)

核心作用:选择目标Rank(内存颗粒组),隔离未选Rank的命令响应

低电平(选中状态):

使能命令解码,内存响应控制器指令(如ACT、READ、WRITE)

多Rank系统中,仅被选中的Rank执行操作,避免总线冲突

高电平(未选中状态):

屏蔽所有命令,未选Rank忽略地址/控制信号

关键时序:

读写期间必须保持稳定低电平,否则导致操作失败

与CKE协同:在掉电模式下,CS_n无效但仍需保持电平稳定

多Rank扩展:每增加一个Rank需独立CS_n信号(如CS0_n/CS1_n),实现物理隔离与并发访问

ODT(On-Die Termination,片上终端电阻)

核心作用:动态启用片内终端电阻,匹配传输线阻抗,抑制信号反射

使能逻辑:

高电平:启用终端电阻(常见阻值:40Ω/48Ω/60Ω)

低电平:禁用终端电阻,减少静态功耗

配置方式:

通过模式寄存器(MR)设定阻值(如DDR3的MR1、DDR4的MR1_A11)

支持动态切换:写入时目标Rank启用ODT,读取时控制器启用ODT

限制场景:

自刷新模式下ODT无效

部分配置(如DDR5 x4颗粒)不支持ODT

信号完整性价值:

减少高频信号(>3200MT/s)的反射和串扰,替代主板外部电阻

多Rank系统中分组控制(如ODT0/ODT1),避免并联阻抗失配

八*、C0/CKE1,C1/CS1_n,C2/ODT1

在DDR(尤其是DDR4及后续版本)内存系统中,堆叠地址输入(Stack Address Inputs)是专为多层堆叠封装设计的关键引脚,用于解决高密度存储集成中的芯片选择与信号控制问题。

堆叠地址输入引脚主要包括 **C0/CKE1、C1/CS1_n、C2/ODT1** 等复用信号,其作用根据封装类型动态切换:

基本角色:

在堆叠封装(如2H/4H/8H层高的x4/x8颗粒)中,用于选择堆叠中的特定芯片层(Chip ID)

在非堆叠封装(如单层mono或x16配置)中,这些引脚通常未连接(NC)或复用为控制信号

复用机制:

当ACT_n=0(地址模式)时,C0/C1/C2 作为地址线 A0/A1/A2 使用。

当ACT_n=1(命令模式)时,切换为控制信号 CKE1(时钟使能)、CS1_n(片选)、ODT1(终端电阻使能)

堆叠封装中的具体作用

1. DDP(Dual-Die Package)封装

功能:在双芯片堆叠中,C0/C1/C2直接控制第二芯片的 CKE1、CS1_n、ODT1

协同逻辑:

主芯片由 CS0_n 选通,副芯片由 CS1_n 选通,实现双Rank独立控制。

读写时,通过 ODT1 独立启用副芯片的终端电阻,优化信号完整性

2. 高堆叠配置(4H/8H)

芯片ID选择:在4层或8层堆叠中,C0/C1/C2 组合编码(如二进制 000-111)选择目标芯片层

信号扩展:

共享同一组命令/地址总线,但通过芯片ID实现分时操作,避免数据冲突。

例如:发送激活命令时,C0-C2携带芯片ID,与行地址同步锁存

九、BA、BG

BA与BG的协同设计是DDR高带宽、大容量的基石:BA解决“微观”并行,BG实现“宏观”流水。

| 信号 | 定位层级 | 核心功能 | 性能影响 |

| BA | Bank选择 | 组内存储体寻址 | 提升Bank级并行度 |

| BG | Bank Group选择 | 组间隔离与并发控制 | 降低延迟,突破带宽瓶颈 |

十、PAR

奇偶校验(Parity Check)

功能原理:

PAR引脚接收内存控制器生成的奇偶校验位,该位基于当前时钟周期内所有命令和地址信号(如CS_n、CKE、ODT、BG/BA、A[17:0]等)的二进制值计算得出(通常采用偶校验)

若信号中“1”的数量为奇数,则校验位=1;若为偶数,则校验位=0。

错误检测:

DRAM内部重新计算校验值,并与PAR输入比对。若不一致,则触发错误标志(通过ALERT_n引脚拉低通知控制器)

动态使能控制:

可通过模式寄存器(MR) 配置启用或禁用校验功能

禁用时,PAR引脚状态被忽略,不参与校验流程。

-

PCB基本的器件管脚类型及其补偿说明2022-07-22 6493

-

ddr datasheet元器件资料下载2012-08-11 2200

-

新建元器件的管脚怎么修改和编辑2017-12-06 9123

-

RK3288 DDR 设计2018-02-23 8038

-

器件PIN不能显示管脚序号2019-04-22 1799

-

TTL常用器件管脚排列和功能说明2019-04-25 1925

-

Altium designer 怎么自动交换器件管脚2019-10-25 2972

-

Xilinx 7系列FPGA管脚是如何定义的?2021-05-28 4738

-

Xilinx 7系列FPGA芯片管脚定义与封装2021-07-08 12215

-

CMOS器件空闲管脚怎么处理?2021-11-05 5294

-

FPGA芯片_GW2AN-55器件封装与管脚手册2022-09-29 774

-

ALTERA FPGA特殊管脚说明2010-06-11 534

-

DDR内存条引脚定义图 管脚定义图2007-12-15 32165

-

如何快速复制器件的管脚?2021-06-28 4508

-

GW2AN 55器件封装与管脚手册2022-09-15 565

全部0条评论

快来发表一下你的评论吧 !