AM6546 Sitara™处理器技术文档总结

描述

AM654x 和 AM652x Sitara™ 处理器是 Arm 应用处理器,旨在满足现代工业 4.0 嵌入式产品的复杂处理需求。

AM654x 和 AM652x 器件将四个或两个 Arm Cortex-A53 内核与双 Arm Cortex-R5F MCU 子系统相结合,该子系统包括旨在帮助客户实现其最终产品功能安全目标的功能,以及三个千兆工业通信子系统 (PRU_ICSSG),以创建能够为功能安全应用提供工业连接和处理的高性能工业控制的 SoC。AM65xx目前正在接受TÜV南德意志集团根据IEC 61508认证的评估。

*附件:am6546.pdf

AM654x 中的四个 Arm Cortex-A53 内核排列在两个具有共享 L2 内存的双核集群中,以创建两个处理通道。AM652x 中的两个 Arm Cortex-A53 内核提供单个双核集群和两个单核集群选项。片上存储器、外设和互连上包含广泛的 ECC,以确保可靠性。整个 SoC 包括旨在帮助客户设计能够实现其功能安全目标的系统的功能(有待 TÜV SÜD 评估)。除了由 DMSC 管理的粒度防火墙外,某些 AM654x 和 AM652x 设备还提供加密加速和安全启动。

具有 Arm Neon™ 扩展的 Arm Cortex-A53 RISC CPU 提供了可编程性,双 Arm Cortex-R5F MCU 子系统可作为两个内核用于通用用途,也可以同步使用,以帮助满足功能安全应用的需求。PRU_ICSSG子系统可用于提供多达六个工业以太网端口,例如 Profinet IRT、TSN、Ethernet/IP 或 EtherCAT(以及许多其他端口),也可用于标准千兆以太网连接。

TI 为 Arm 内核提供了一套完整的软件和开发工具,包括处理器 SDK Linux、Linux-RT、RTOS 和 Android,以及 C 编译器以及用于查看源代码执行的调试接口。将提供适用的功能安全和安保文档,以协助客户开发其功能安全或安保相关系统。

特性

处理器内核:

双核或四核 Arm Cortex-A53 微处理器子系统,频率高达 1.1 GHz

- 最多两个双核或两个单核 Arm Cortex-A53 集群,具有 512KB 二级缓存,包括 SECDED

- 每个 A53 内核具有 32KB L1 ICache 和 32K L1 DCache

双核 Arm Cortex-R5F,频率高达 400 MHz

- 支持锁步模式

- 每个 R5F 内核 16KB ICache、16KB DCache 和 64KB RAM

工业子系统:

三个千兆工业通信子系统 (PRU_ICSSG)

- 每个PRU_ICSSG最多两个 10/100/1000 以太网端口

- 支持两个 SGMII 端口 (2)

- 与 10/100Mb PRU-ICSS 兼容

- 每PRU_ICSSG 24× PWM

- 逐周期控制

- 增强的跳闸控制

- 每PRU_ICSSG 18× 个 Σ-δ 滤波器

- 短路逻辑

- 过流逻辑

- 6× 每个PRU_ICSSG的多协议位置编码器接口

内存子系统:

高达 2MB 的片上 L3 RAM,带 SECDED

多核共享内存控制器 (MSMC)

- 高达 2MB(2 组 × 1MB)带 SECDED 的 SRAM

- 共享相干2级或3级内存映射SRAM

- 共享相干的 3 级缓存

- 256 位处理器端口总线和 40 位物理地址总线

- 用于连接到处理器或设备主站的一致统一双向接口

- L2、L3 缓存预热和后刷新

- 具有饥饿限制的带宽管理

- 一个基础设施主界面

- 单个外部存储器主接口

- 支持分布式虚拟系统

- 支持内部 DMA 引擎 – 数据路由单元 (DRU)

- ECC 错误保护

- 高达 2MB(2 组 × 1MB)带 SECDED 的 SRAM

DDR 子系统 (DDRSS)

- 支持高达 DDR-1600 的 DDR4 内存类型

- 32位数据总线和7位SECDED总线

- 8 GB 的总可寻址空间

通用内存控制器 (GPMC)功能安全:

符合功能安全标准 [工业]

- 专为功能安全应用而开发

- 可用于帮助 IEC 61508 功能安全系统设计的文档

- 系统能力高达 SIL 3

- 硬件完整性高达 SIL 2

- 安全相关认证

功能安全特性:

- 计算关键存储器和内部总线互连上的 ECC 或奇偶校验

- 防火墙有助于提供不受干扰 (FFI)

- 用于 CPU、高端定时器和片上 RAM 的内置自检 (BIST)

- 对诊断测试的硬件错误注入支持

- 错误信号模块 (ESM),用于捕获功能安全相关错误

- 电压、温度和时钟监控

- 多个时钟域中的窗口和非窗口看门狗定时器

MCU岛

- 双核 Arm Cortex-R5F 微处理器子系统的隔离

- 独立的电压、时钟、复位和专用外设

- 与 SoC 其余部分的内部 MCSPI 连接

安全:

支持安全启动

- 硬件强制实施的信任根

- 支持通过备份密钥切换信任根

- 支持接管保护、IP 保护和防回滚保护

支持加密加速

- 会话感知加密引擎,能够根据传入数据流自动切换密钥材料

- 支持加密核心

- AES – 128/192/256 位密钥大小

- 3DES – 56/112/168 位密钥大小

- MD5、SHA1

- SHA2 – 224/256/384/512

- DRBG 与真随机数生成器

- PKA(公钥加速器)辅助 RSA/ECC 处理

- DMA 支持

调试安全性

- 安全的软件控制调试访问

- 安全感知调试

支持可信执行环境 (TEE)

- 基于 Arm TrustZone 的 TEE

- 广泛的防火墙支持隔离

- 安全的 DMA 路径和互连

- 安全看门狗/定时器/IPC

安全存储支持

对 OSPI 接口的动态加密和身份验证支持

通过基于数据包的硬件加密引擎对数据(有效负载)加密/身份验证的网络安全支持

用于密钥和安全管理的安全协处理器 (DMSC),具有用于安全软件的专用设备级互连SoC 服务:

设备管理安全控制器 (DMSC)

- 集中式 SoC 系统控制器

- 管理系统服务,包括初始启动、安全、功能安全和时钟/复位/电源管理

- 用于有源和低功耗模式的电源管理控制器

- 通过消息管理器与各种处理单元进行通信

- 用于优化未使用的外设的简化接口

- 跟踪和调试能力

16 个 32 位通用定时器

两个数据移动和控制导航子系统 (NAVSS)

- 环形加速器 (RA)

- 统一 DMA (UDMA)

- 多达 2 个定时器管理器 (TM)(每个定时器 1024 个)

多媒体:

显示子系统

- 两个完全输入映射的叠加管理器与两个显示输出相关联

- 单端口 MIPI DPI 并行接口

- 一个端口 OLDI

PowerVR SGX544-MP1 3D 图形处理单元 (GPU)

单摄像头串行接口-2 (MIPI CSI-2)

单端口视频捕获:BT.656/1120(无嵌入式同步)高速接口:

一个千兆以太网 (CPSW) 接口支持

- RMII (10/100) 或 RGMII (10/100/1000)

- IEEE1588(2008 年附件 D、附件 E、附件 F)和 802.1AS PTP

- 音频/视频桥接 (P802.1Qav/D6.0)

- 节能以太网 (802.3az)

- 巨型帧(2024 字节)

- 第 45 条 MDIO PHY 管理

两个 PCI-Express (PCIe) 修订版 3.1 子系统 (2)

- 支持 Gen2 (5.0GT/s)作

- 两个独立的 1 通道端口或一个 2 通道端口

- 支持并发根复合体和端点作

USB 3.1 双角色设备 (DRD) 子系统 (2)

- 一个增强型 SuperSpeed Gen1 端口

- 一个 USB 2.0 端口

- 每个端口可独立配置为 USB 主机、USB 外设或 USB DRD

一般连接:

6× 集成电路间 (I2C™) 端口

5×可配置的UART/IrDA/CIR模块

两个同时闪存接口配置为

- 两个 OSPI 闪存接口

- 或 HyperBus™ 和 OSPI1 闪存接口

2× 12位模数转换器(ADC)

- 高达 4 Msamples/s

- 八个多路复用模拟输入

8× 多通道串行外设接口 (MCSPI) 控制器

- 两个带内部连接

- 六个带外部接口

通用 I/O (GPIO) 引脚控制接口:

6×增强型高分辨率脉宽调制器(EHRPWM)模块

一个增强型捕获 (ECAP) 模块

3×增强型正交编码器脉冲(EQEP)模块汽车接口:

2×模块化控制器局域网(MCAN)模块,完全支持CAN-FD音频接口:

3× 多通道音频串行端口 (MCASP) 模块媒体和数据存储:

2× 多媒体卡™/安全数字(MMC™/SD)接口简化的电源管理:

简化的电源序列,完全支持双电压 I/O

集成LDO降低了电源解决方案的复杂性

集成SDIO LDO,用于处理SD接口的自动电压转换

集成上电复位 (POR) 生成,降低电源解决方案的复杂性

用于功能安全监控的集成电压监控器

集成电源毛刺检测器,用于检测快速电源瞬变模拟/系统集成:

集成 USB VBUS 检测

用于 DDR RESET 的故障安全 I/O

所有 I/O 引脚驱动器在复位期间禁用以避免总线冲突

重置期间禁用默认 I/O 拉取以避免系统冲突

支持动态 I/O pinmux 配置更改片上系统 (SoC) 架构:

支持从 UART、I2C、OSPI、HyperBus、并行 NOR 闪存、SD 或 eMMC™、USB、PCIe 和以太网接口进行主启动

28纳米CMOS技术

23 mm × 23 mm、0.8 mm 间距、784 引脚 FCBGA (ACD)

参数

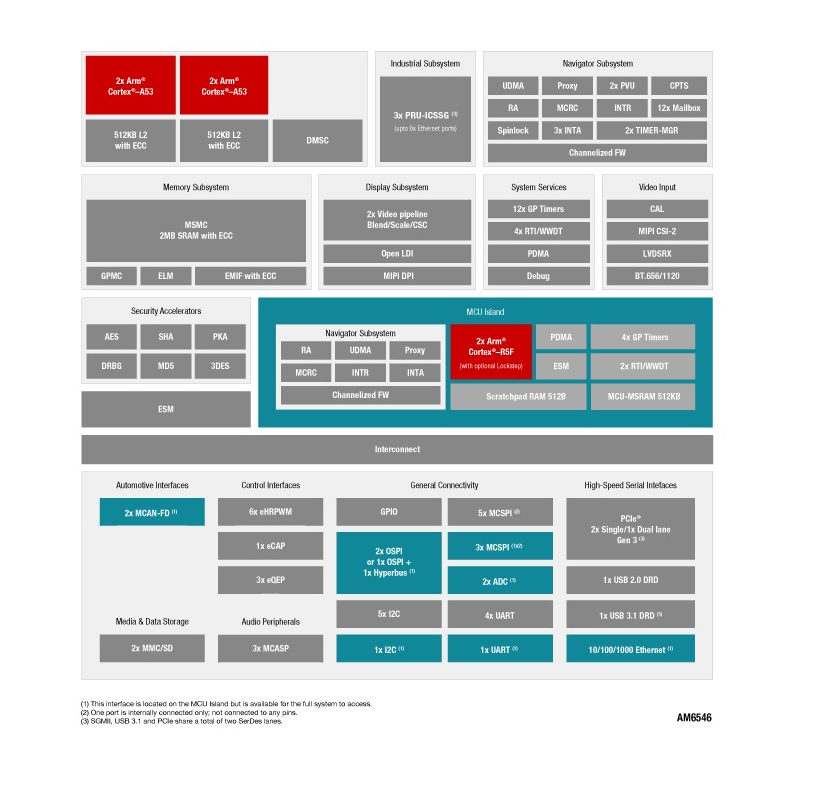

方框图

1. 产品概述

- 型号系列:AM6548/AM6528/AM6546/AM6526,基于Arm® Cortex®架构,面向工业4.0应用设计。

- 核心配置:

- AM654x:四核Cortex-A53(双集群)+ 双核Cortex-R5F(支持锁步模式)。

- AM652x:双核Cortex-A53(单集群)+ 双核Cortex-R5F。

- 工艺技术:28nm CMOS,784引脚FCBGA封装(23mm×23mm)。

2. 关键特性

- 工业通信:集成3个PRU_ICSSG子系统,支持多协议工业以太网(如Profinet IRT、EtherCAT®)。

- 功能安全:通过IEC 61508认证(SIL 3系统性能力/SIL 2硬件完整性),支持ECC、防火墙、BIST等安全特性。

- 高性能接口:

- DDR4控制器(最高8GB,32位总线)。

- PCIe® 3.1、USB 3.1、千兆以太网(CPSW)。

- 多媒体加速:PowerVR® SGX544-MP1 GPU、双显示输出(MIPI DPI/OLDI)。

3. 应用场景

- 工业PLC、机器人控制、HMI、电网保护继电器、电机驱动等。

4. 文档结构

- 功能描述:详细说明处理器子系统、内存架构(2MB L3 RAM)、外设(如MCASP、EQEP)。

- 电气特性:涵盖工作温度、电压范围、功耗及ESD等级。

- 引脚配置:784-ball FCBGA封装引脚定义及复用功能表(如GPIO、UART、SPI等)。

5. 开发支持

- 提供Linux/RTOS/Android SDK,配套功能安全与安全认证文档。

注:本文档为德州仪器(TI)发布的修订版(SPRSP52C,2023年9月),包含完整的规格参数、设计指南及参考电路。

-

AM243x Sitara™ 微控制器技术文档总结2025-10-10 1453

-

AM62Ax处理器技术文档总结2025-09-30 2395

-

AM335x和AMIC110 Sitara™处理器技术参考手册2024-11-14 566

-

AM335x和AM43xx Sitara处理器USB布局指南2024-09-19 402

-

AM570x Sitara™处理器数据表2024-08-08 431

-

AM3715、AM3703 Sitara ARM微处理器数据表2024-08-05 675

-

AM62Ax Sitara™处理器数据表2024-08-03 523

-

AM3874 AM3872 AM3871 Sitara ARM微处理器数据表2024-08-02 407

-

AM6546 Sitara 处理器:四核 Arm Cortex-A53 和双核 Arm Cortex-R5F,千兆位 PRU-ICSS2019-01-08 759

-

AM335x Sitara 处理器2015-07-07 2269

-

AM1810 Sitara ARM 微处理器2011-01-24 3067

-

TI推出Sitara微处理器单元Sitara微处理器单元AM2010-06-21 863

全部0条评论

快来发表一下你的评论吧 !